(一)简述

AArch拥有31个通用寄存器,系统运行在64位状态下的时候名字叫Xn,运行在32位的时候就叫Wn;

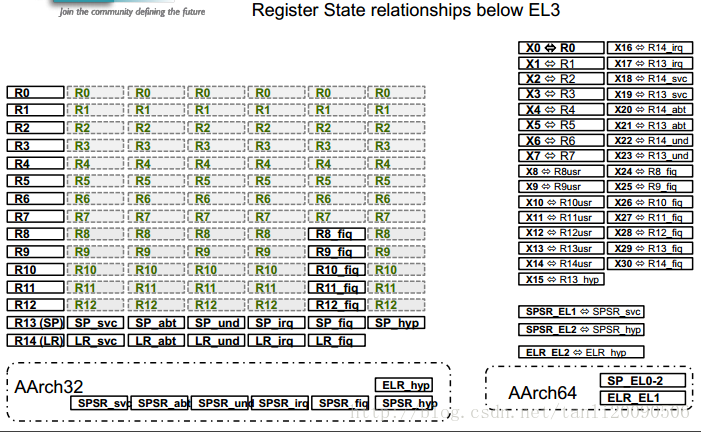

AArch32与AArch64寄存器对应关系:

(二)PSTATE

PSTATE不是一个寄存器,它表示的是保存当前process状态信息的一组寄存器或者一些标志位信息的统称,当异常发生的时候这些信息就会保存到EL所对应的SPSR寄存器当中;

寄存器:

标志位:

type ProcState is (

bits (1) N,

bits (1) Z,

bits (1) C,

bits (1) V,

bits (1) D,

bits (1) A,

bits (1) I,

bits (1) F,

bits (1) SS,

bits (1) IL,

bits (2) EL,

bits (1) nRW,

bits (1) SP,

bits (1) Q,

bits (4) GE,

bits (8) IT,

bits (1) J,

bits (1) T,

bits (1) E,

bits (5) M

)

PSTATE.{N, Z, C, V}: 条件标志位,这些位的含义跟之前AArch32位一样,分别表示补码标志,运算结果为0标志,进位标志,带符号位溢出标志,具体请参考:ARM(V8) Architecture Reference Manual.pdf page B1-62;

PSTATE.SS:异常发生的时候,通过设置MDSCR_EL1.SS 为 1启动单步调试机制;

PSTATE.IL:异常执行状态标志,非法异常产生的时候,会设置这个标志位,会导致的事件请参考:D1.11.3page D1-1439;

PSTATE.{D, A, I, F}:D表示debug异常产生,比如软件断点指令/断点/观察点/向量捕获/软件单步 等;A, I, F表示异步异常标志,异步异常会有两种类型:一种是物理中断产生的,包括SError(系统错误类型,包括外部数据终止),IRQ或者FIQ;另一种是虚拟中断产生的,这种中断发生在运行在EL2管理者enable的情况下:vSError,vIRQ,vFIQ;

PSTATE.nRW:表示当前ELx 所运行的状态,分为AArch64和AArch32:

- SPSR_EL1.M[4] 决定EL0的执行状态,为0(64bit ),1(32bit);

- HCR_EL2.RW 决定EL1的执行状态,为1(64bit ),0(32bit);

- SCR_EL3.RW确定EL2 or EL1的执行状态,为1(64bit ),0(32bit);

PSTATE.SP: 某个ELx 下的堆栈指针,EL0下就表示sp_el0;

SPSR registers:

SPSR状态寄存器:之前也有说过当运行在EL0层的时候,所用的是sp_el0,当在更高级ELx运行的时候同时可以使用spsr_el0或者spsr_elx,所以这里用t,h后缀来区分,SPSR_ELx保存了进入ELx的PSTATE状态信息:

(三)A64指令集

(0)A64特点

- 移除了批量加载寄存器指令 LDM/STM, PUSH/POP, 使用STP/LDP 一对加载寄存器指令代替;

- 没有提供访问CPSR的单一寄存器,但是提供访问PSTATE的状态域寄存器;

- A64没有协处理器的概念,没有协处理器指令MCR,MRC;

- 相比A32少了很多条件执行指令,只有条件跳转和少数数据处理这类指令才有条件执行.附件为条件指令码;

指令基本格式:

<Opcode>{<Cond>}<S> <Rd>, <Rn> {,<Opcode2>}

Opcode:操作码,也就是助记符,说明指令需要执行的操作类型

Cond:指令执行条件码,查看附件图;

S:条件码设置项,决定本次指令执行是否影响PSTATE寄存器响应状态位值

Rd/Xt:目标寄存器,A32指令可以选择R0-R14,T32指令大部分只能选择RO-R7,A64指令可以选择X0-X30;

Rn/Xn:第一个操作数的寄存器,和Rd一样,不同指令有不同要求;

Opcode2:第二个操作数,可以是立即数,寄存器Rm和寄存器移位方式(Rm,#shit);

各种指令详细说明请查看ARM(V8) Architecture Reference Manual.pdf page C6-387 这里只是贴出了内存访问操作的指令;

内存操作指令load/store

所支持的寻址方式:

- Base register only (no offset) :基址寄存器无偏移;

- Base plus offset:基址寄存器加偏移;

- Pre-indexed:事先更新寻址,先变化后操作,[base, #imm]!,!表示则当数据传送完毕之后,将最后的地址写入基址寄存器,否则基址寄存器的内容不改变;

- Post-indexed:事后更新寻址,先操作后变化,[base], #imm;

- Literal (PC-relative): PC相对寻址;

load/store指令分类(C3.2-131):批量寄存器、单个寄存器、一对寄存器、非-暂存、非特权、独占}以及load-Acquire、store-Release指令;

(1)单个寄存器load/store:

以LDR为例,下面为三种取址方式:

如:LDR X1,[X2]; 取出X2寄存器存储的地址中的内容复制到X1;

如:LDR X1,[X2],#4; 取出X2寄存器存储的地址中的内容复制到X1,然后X2 = X2 + 4;

如:LDR X1,[PC,#4];

(2)unscaled offset load/store:

Scaled 和Unscaled其实就是可以见到理解为对齐和非对齐,本质就是是否乘以一个常量,因为scaled的总是可以乘以一个常量来达到对齐,而Unscaled就不需要,是多少就多少,更符合人类自然的理解,寻址方式只支持:基址 + 9bit 的立即数偏移值范围为(-256 ~ 255)因为是带有符号的;

以LDUR为例:

(3)Load/Store Pair:

从Memory地址addr处读取两个双字/字数据到目标寄存器Xt1,Xt2;寻址方式:对齐的,有符号#simm7偏移,支持pre-/post-index 操作;

以LDP为例:

(4)Load/Store Non-temporal Pair:

所谓Non-temporal就是就是用于你确定知道该地址只加载一次,不需要触发缓存,避免数据被刷新,优化性能,其它指令都默认会写Cache;寻址方式:对齐的,有符号#simm7偏移,不支持pre-/post-index 操作;

以LDNP为例:

(4)Load/Store Unprivileged:

所谓Unprivileged就是说EL0/EL1的内存有不同的权限控制,这条指令以EL0的权限存取,用于模拟EL0的行为,该指令应用于EL1和EL0之间的交互;寻址方式: 非对齐的,有符号#simm9偏移,不支持pre-/post-index 操作;

以LDTR为例:

(4)Load-Exclusive/Store-Exclusive:

在多核CPU下,对一个地址的访问可能引起冲突,这个指令解决了冲突,保证原子性(所谓原子操作简单理解就是不能被中断的操作),是解决多个CPU访问同一内存地址导致冲突的一种机制。通常用于锁,比如spinlock,可以参考代码:

arch/arm64/include/asm/spinlock.h

寻址方式:无偏移基址寄存器,不支持pre-/post-index 操作;

以LDXR为例:

(4)Load-Acquire/Store-Release:

内存屏障操作,Load-Acquire读操作,相当于半个DMB指令,只管读内存操作;Store-Release写操作,相当于半个DMB指令,只管写内存操作;本质是为了解决乱序执行中有依赖关系的指令可以按正确的逻辑执行的一种机制,而DMB,DSB,ISB的强制性(权限)由低到高;寻址方式:无偏移基址寄存器,不支持pre-/post-index 操作;

以LDAR为例:

附件

条件指令码:

特殊符号定义:

特殊符号 对应伪操作 含义

& DCD 分配一片连续的字存储单元并用指定的数据初始化

% SPACE 分配一片连续的存储单元

^ MAP 定义一个结构化内存表的首地址

# FILED 定义一个结构化内存表的数据域(经常和MAP一起使用,一个定义起始地址,一个定义长度)

* EQU 为程序中的常量、标号等定义一个等效的字符名

! 地址更新

[ 相当于IF

| 相当于ELSE

] 相当于ENDIF

本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有涉嫌抄袭侵权的内容,请联系:hwhale#tublm.com(使用前将#替换为@)