FPGA编程入门

文章目录

- FPGA编程入门

- 一、1位全加器

- 1、原理图

-

- 2. verilog实现1位全加器

- 2.1 代码

- 2.2 编译,查看RTL

- 2.3 仿真实现

- 二、烧录

- 三、4位全加器

- 1. 原理图实现4位全加器

- 2. verilog实现4位全加器

-

- 四、总结

- 五、参考

一、1位全加器

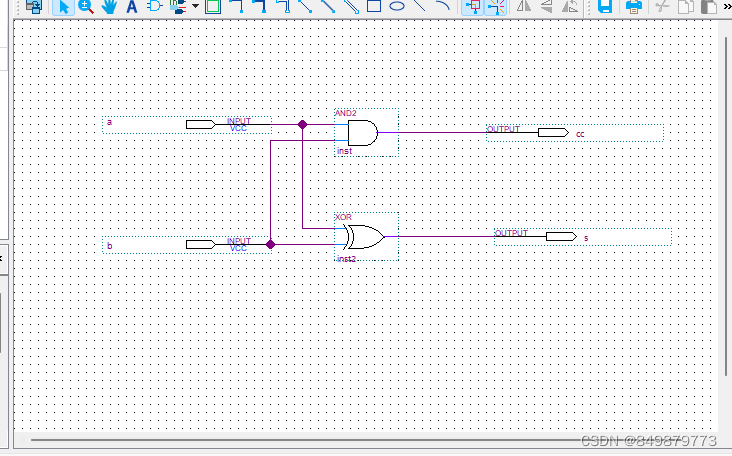

1、原理图

1.1原理图

创建工程过程

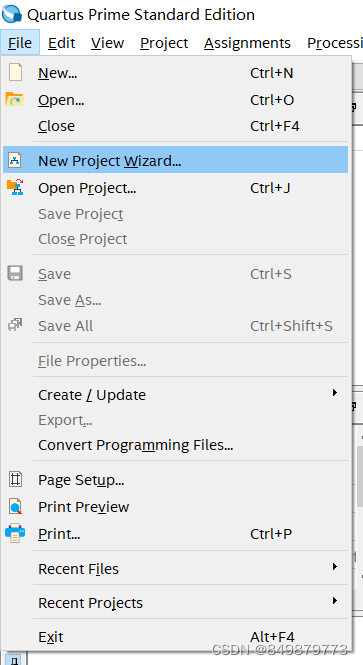

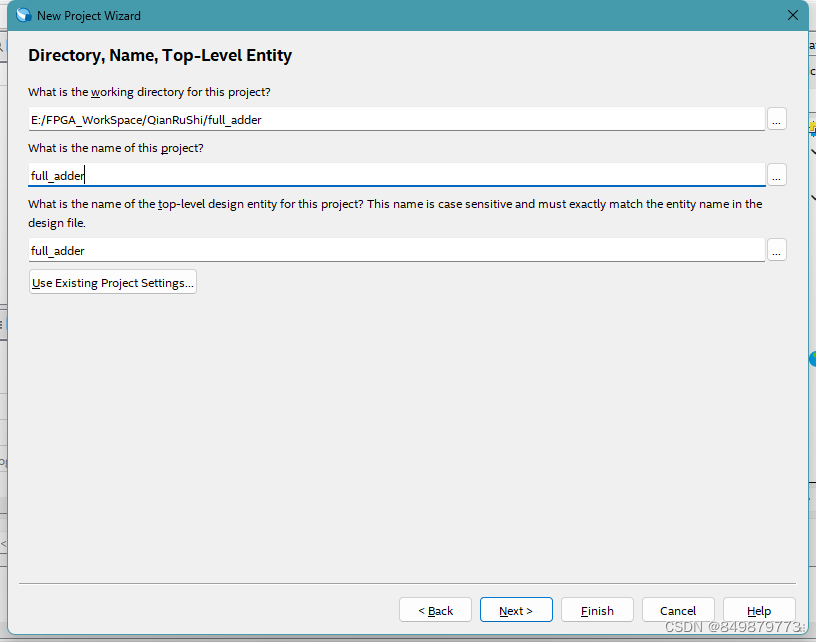

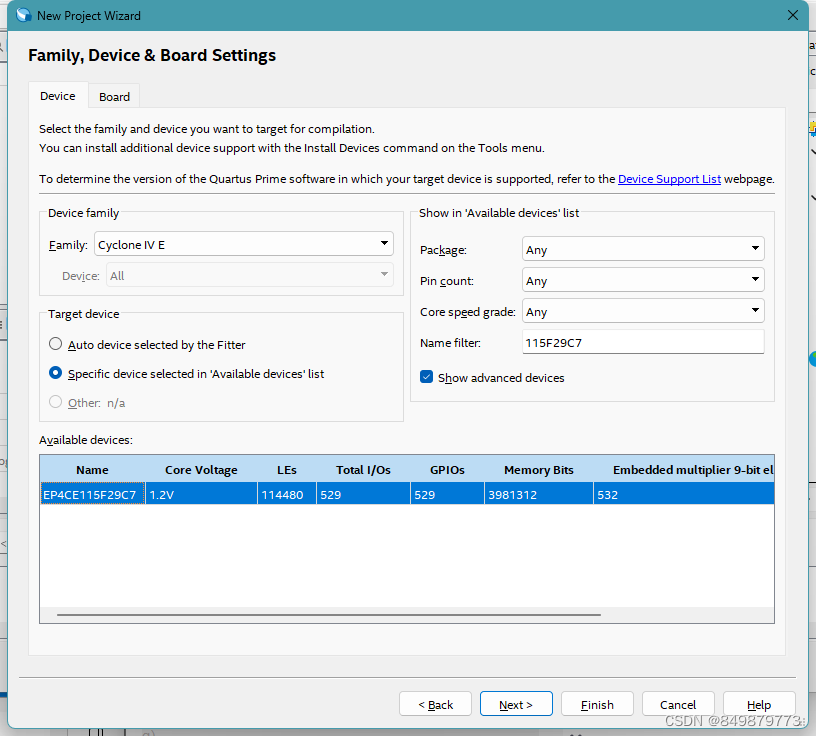

启动 Quartus II 软件,选择File->New Project Wizard,在出现的界面下先Next,填写工程的路径和名称,然后接着Next,直到出现下面界面并进行相应操作。接着一路Next,直到Finish,完成工程的创建。

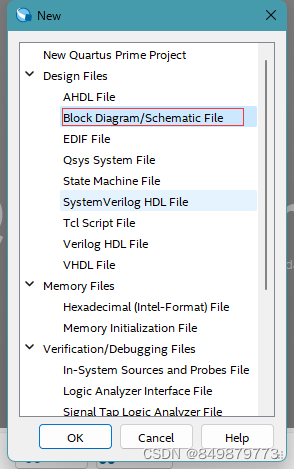

首先选择File->New,进入后选择Block Diagram/Schematic File

原理图

原理图

保存文件,并编译

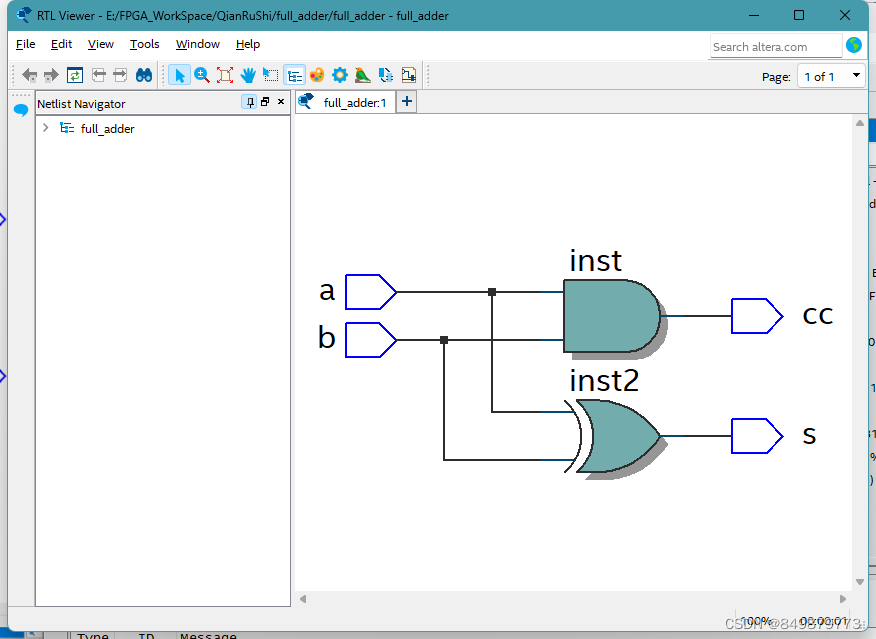

通过tool->Netlist Viewers->RTL Viewer,查看电路图

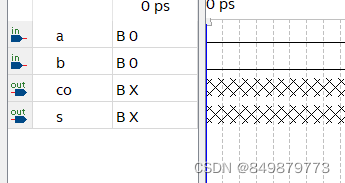

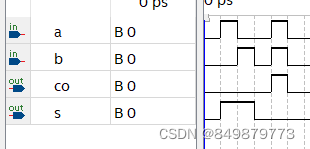

仿真模拟:

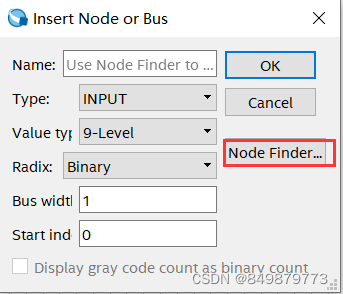

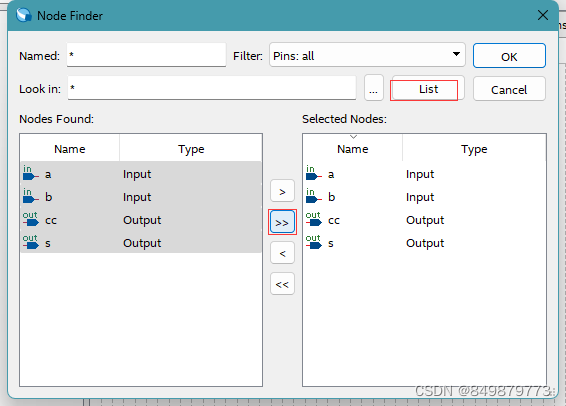

创建一个向量波形文件,选择菜单项 File→New->VWF

保存文件并启动功能仿真,结果如下

1.2 全加器

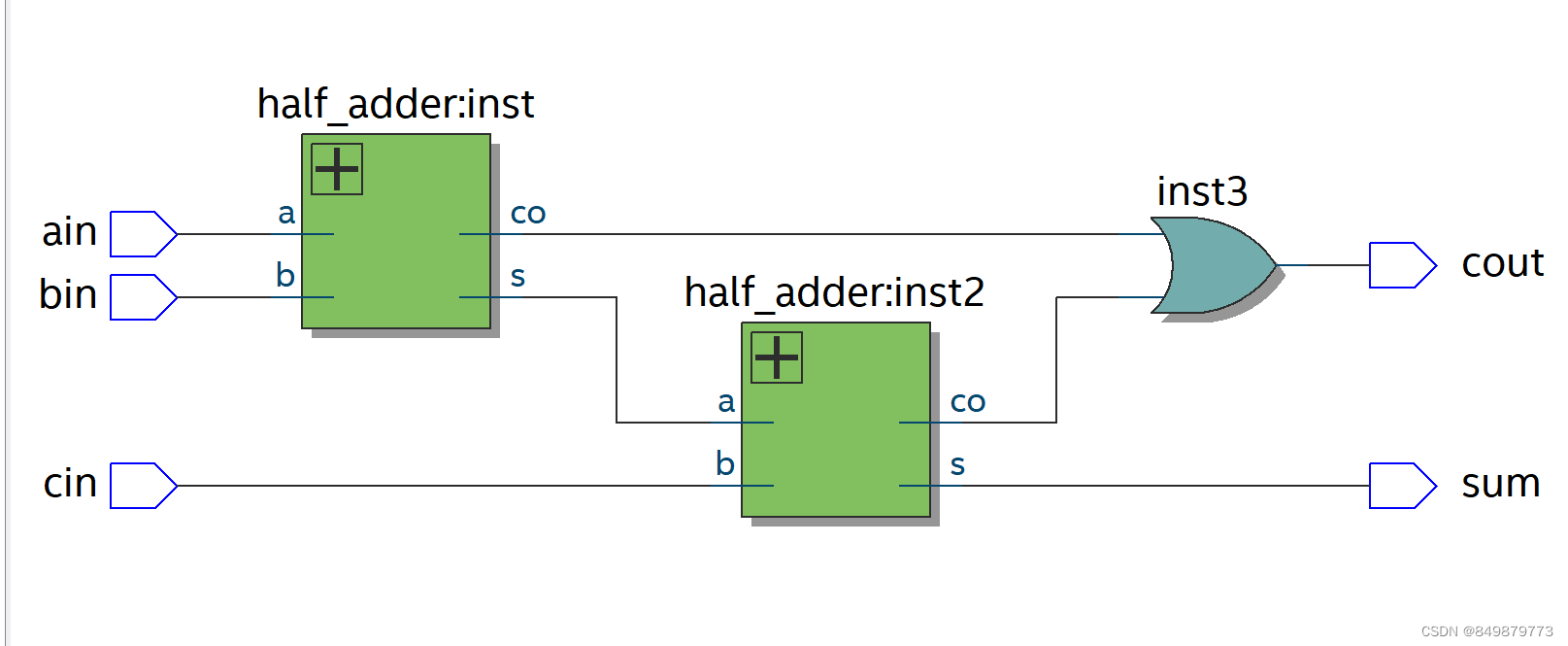

利用半加器元件实现全加器

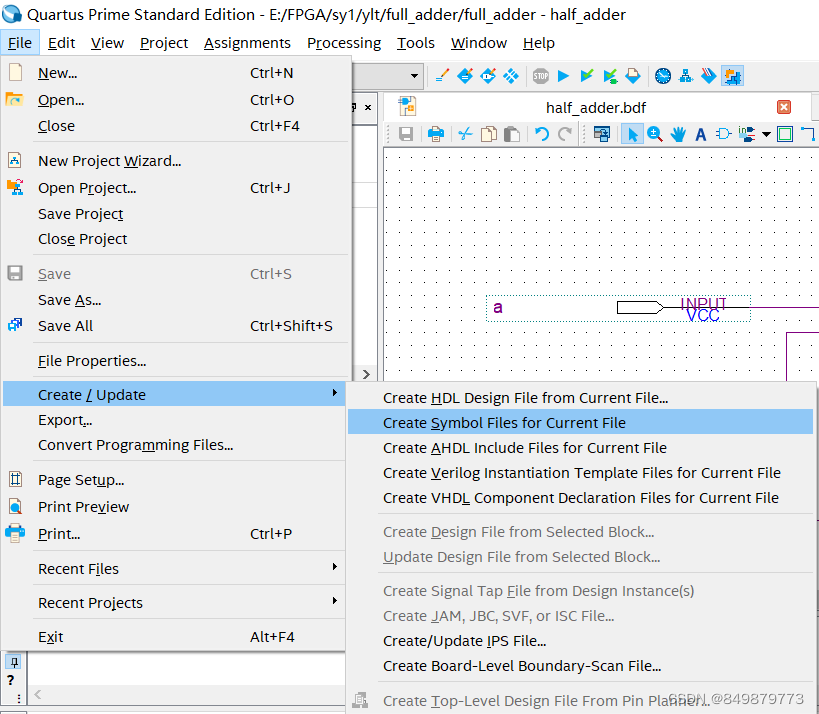

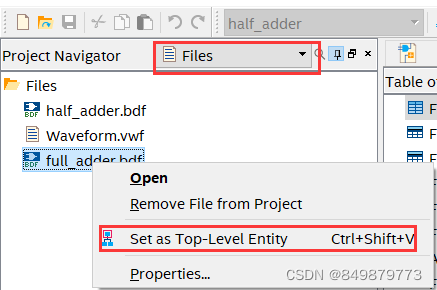

将设计项目设置为可调用的元件

在打开半加器原理图文件half_adder.bdf的情况下,选择菜中File中的Create/Update→CreateSymbolFilesforCurrentFile项,即可将当前文件h_adder.bdf变成一个元件符号存盘,以待在高层次设计中调用

选择File->New,进入后选择Block Diagram/Schematic File

原理图如下

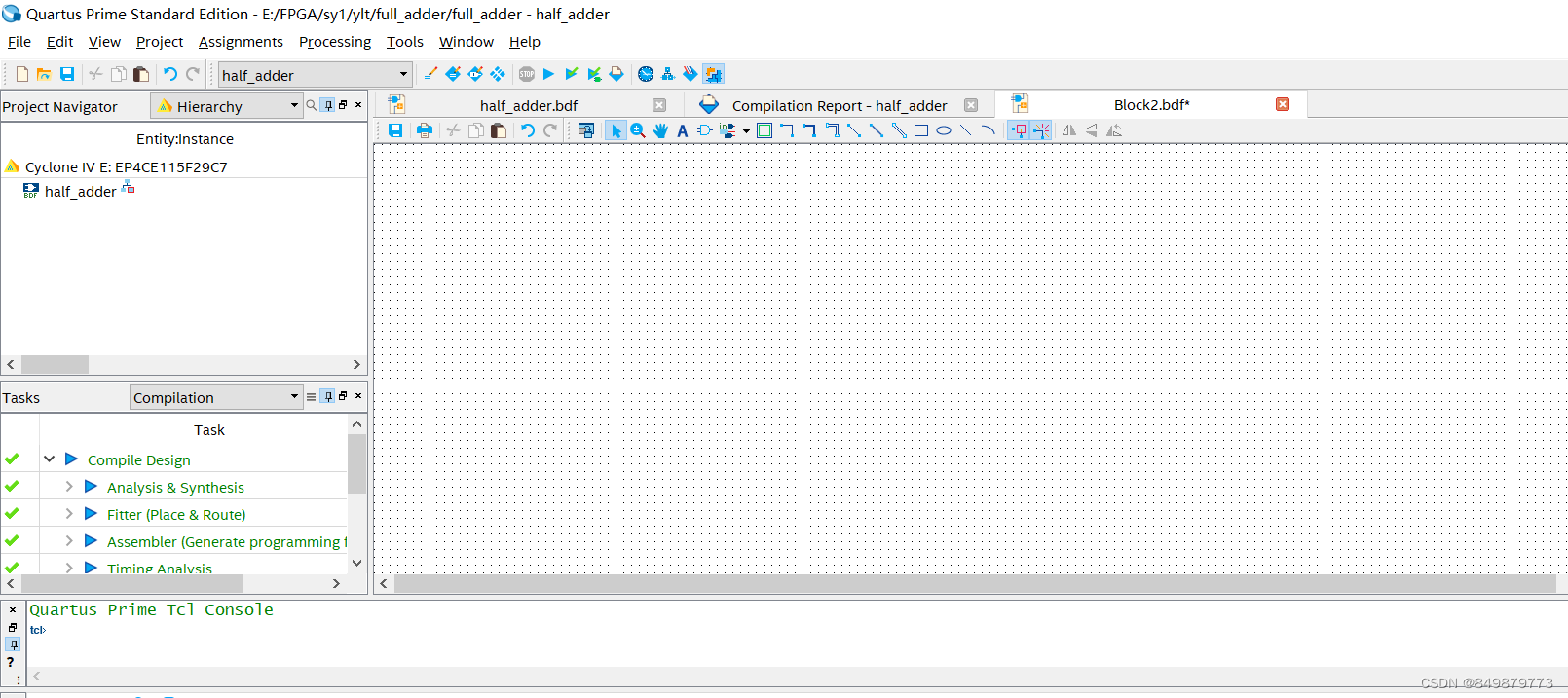

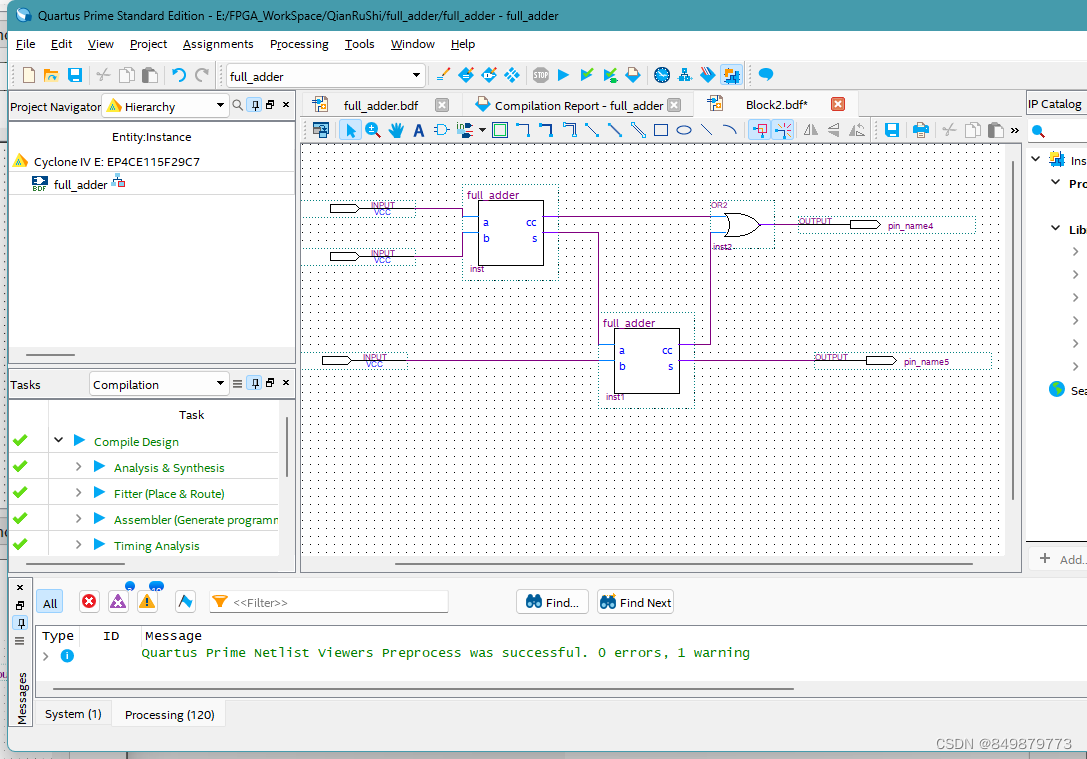

将全加器设置为顶层文件

编译,查看RTL

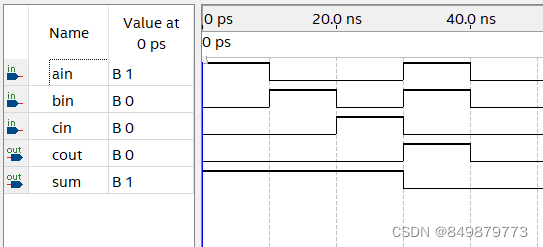

仿真模拟:

2. verilog实现1位全加器

重头开始创建一个项目,选择verilog HDL FILE

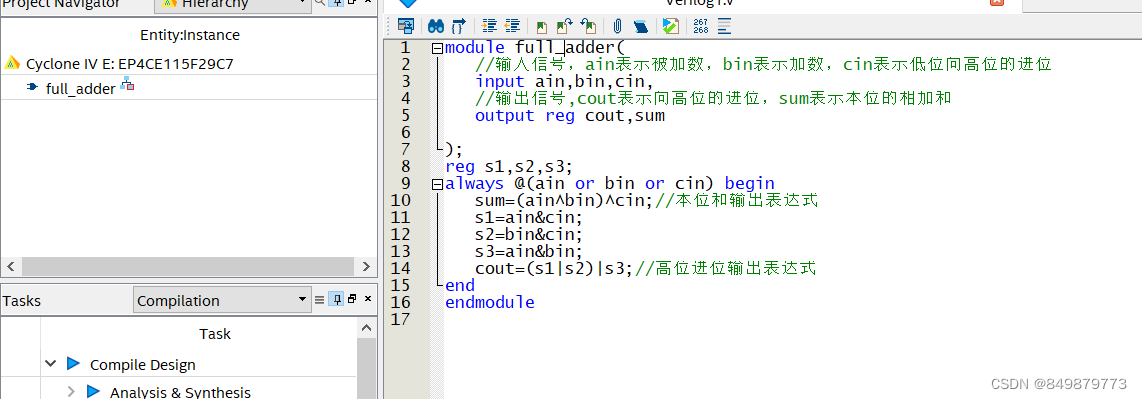

2.1 代码

module full_adder(

input ain,bin,cin,

output reg cout,sum

);

reg s1,s2,s3;

always @(ain or bin or cin) begin

sum=(ain^bin)^cin;

s1=ain&cin;

s2=bin&cin;

s3=ain&bin;

cout=(s1|s2)|s3;

end

endmodule

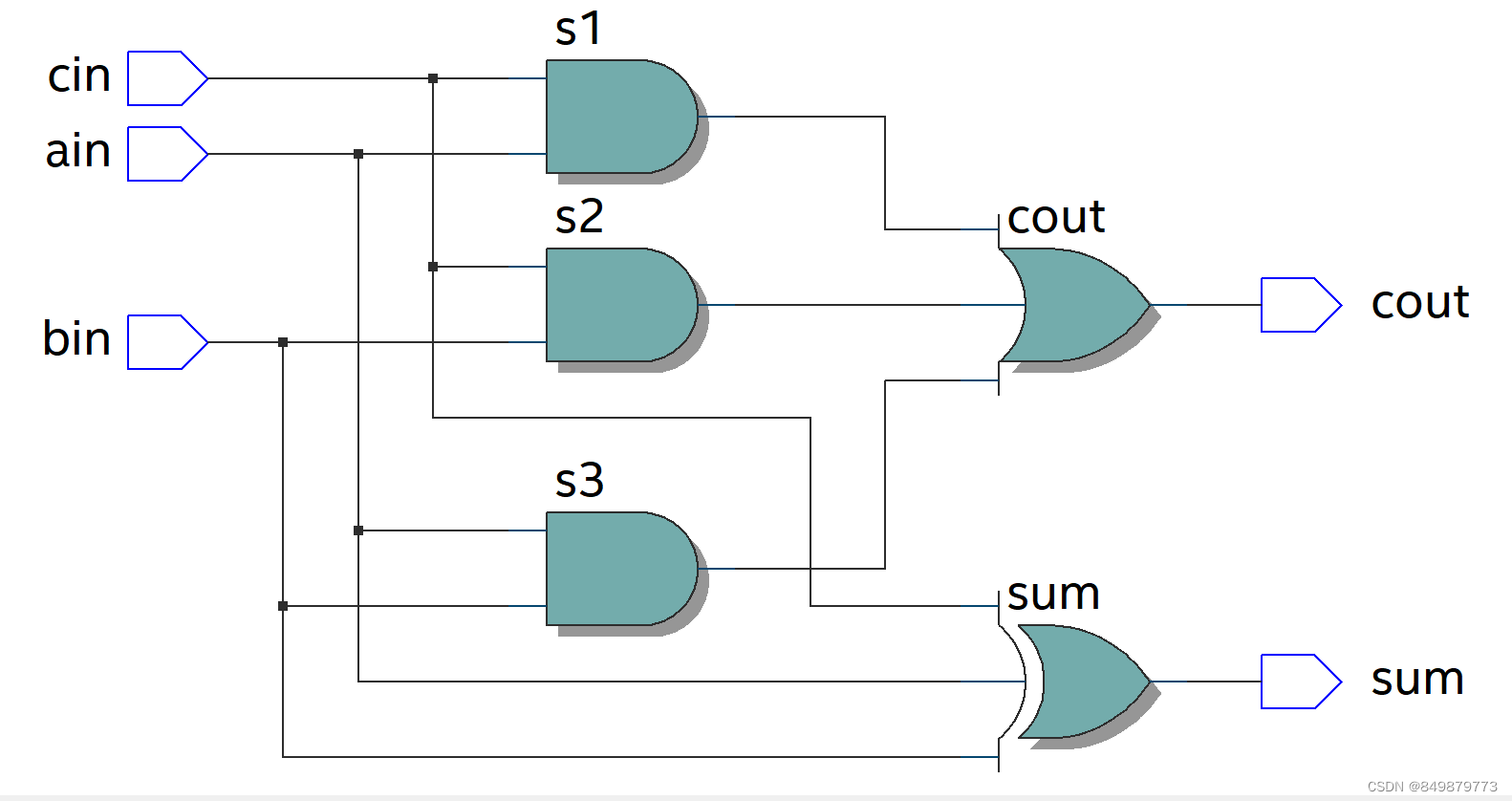

2.2 编译,查看RTL

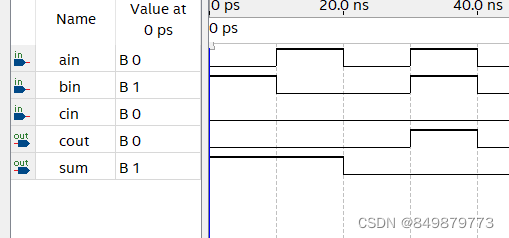

2.3 仿真实现

二、烧录

三、4位全加器

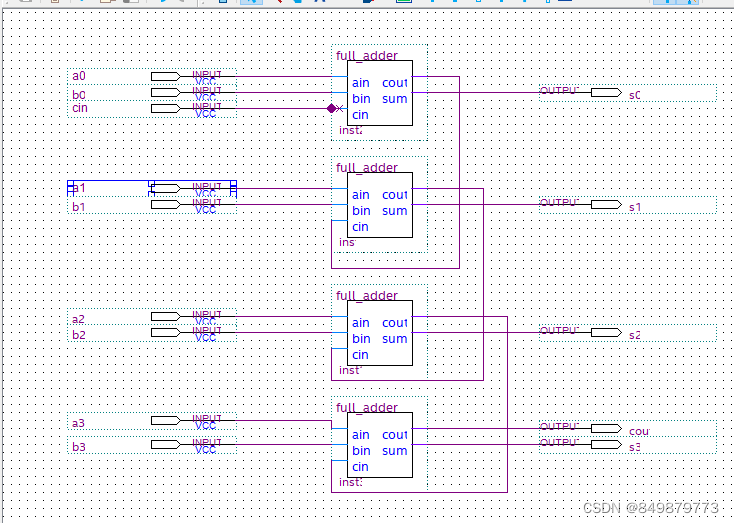

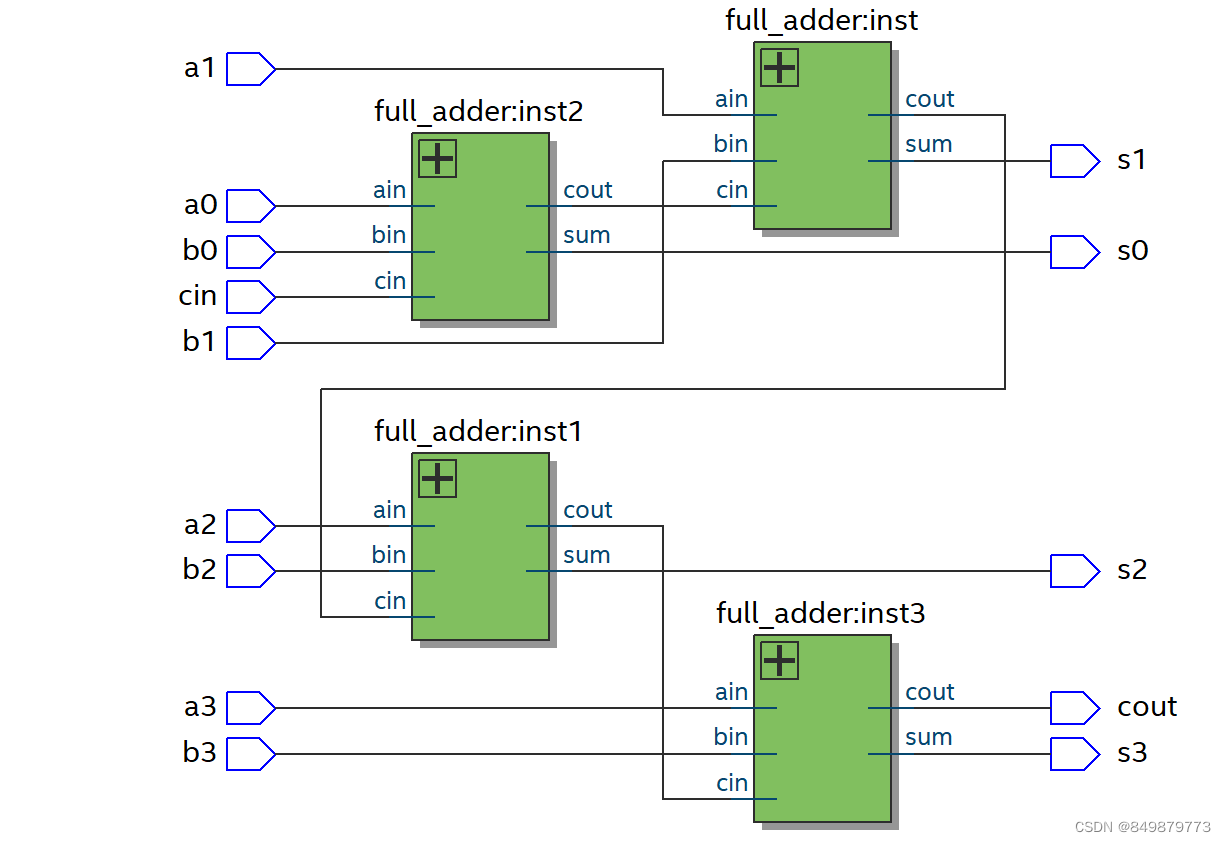

1. 原理图实现4位全加器

将1位全加器保存为元件

新建空白图层,搭建4位全加器

RTL

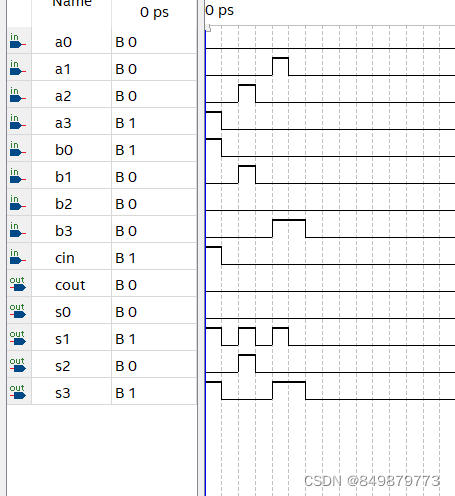

仿真实现:

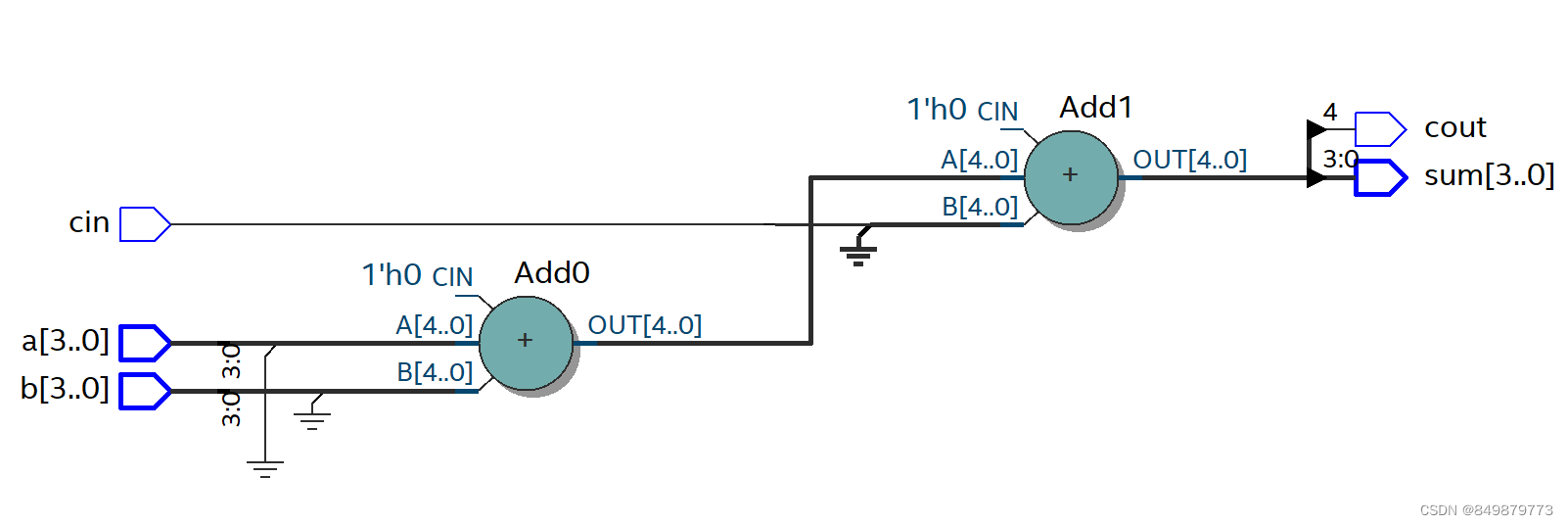

2. verilog实现4位全加器

2.1 代码

module full_adder4(

input[3:0] a,b,

input cin,

output[3:0] sum,

output cout

);

assign{cout,sum} = a+b+cin;

endmodule

2.2 RTL

四、总结

本次实验使用FPGA制作了全加器,并从1位全加器扩展到了4位。复习了前面学习的数电知识,以及更进一步地练习了verilog语法与fpga的使用。

五、参考

https://blog.csdn.net/qq_43279579/article/details/115480406

本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有涉嫌抄袭侵权的内容,请联系:hwhale#tublm.com(使用前将#替换为@)