一个学习信号完整性仿真的layout工程师

在进行PCB投板之前,往往需要将PCB的结构发给结构的同事确认。一般会导出DXF和EMN文件,或者导出3D模型。3D模型包含版型、器件的实际3D模型等等。可以比较直观的看到PCB板上的器件情况,下面简单介绍PCB的3D模型导出。

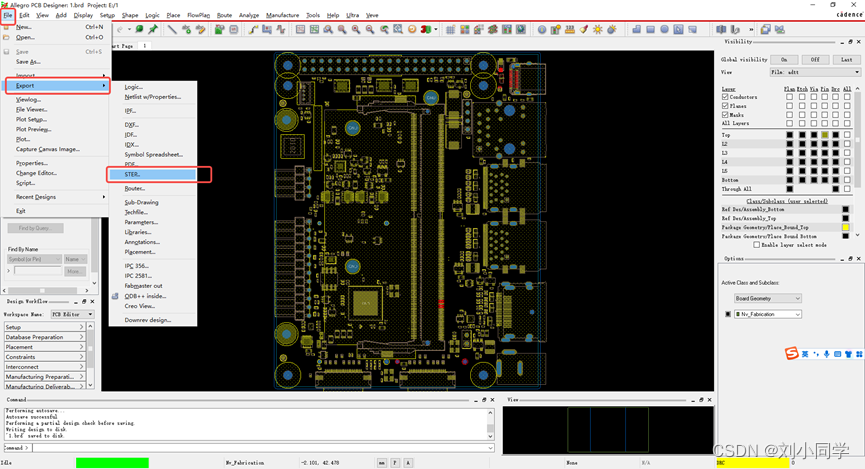

1. 在Allegro的菜单下选择File命令,点击Export中的STEP,STEP各式代表3D,可以显示PCB上各种器件的3D模型,如下图所示:

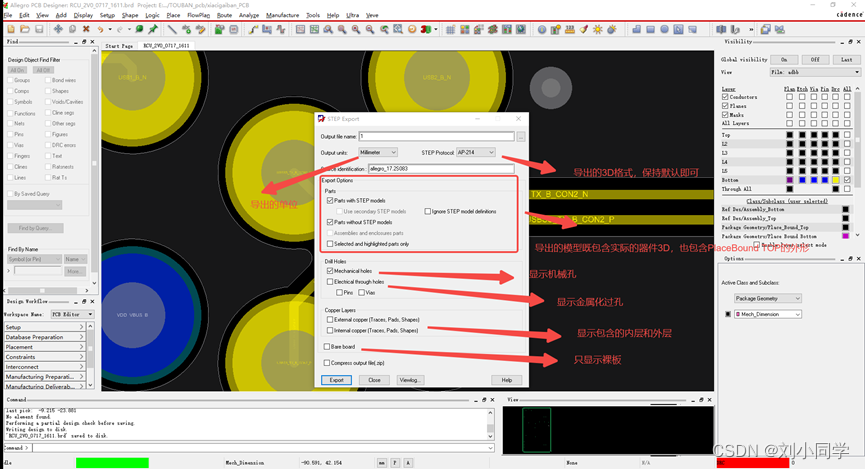

2.完成上一步,会弹出STEP Export对话框,其中可以设置许多导出属性,如下图所示:

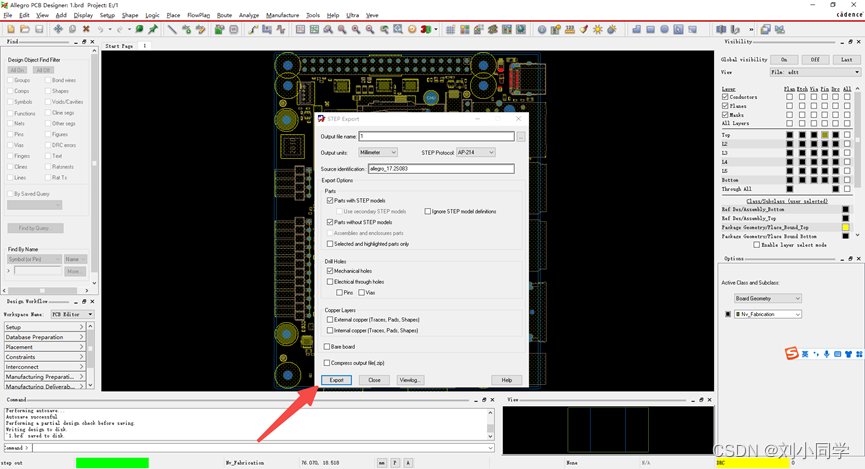

3.点击导出,就可以看到3D模型文件,默认保存在PCB的根目录下,

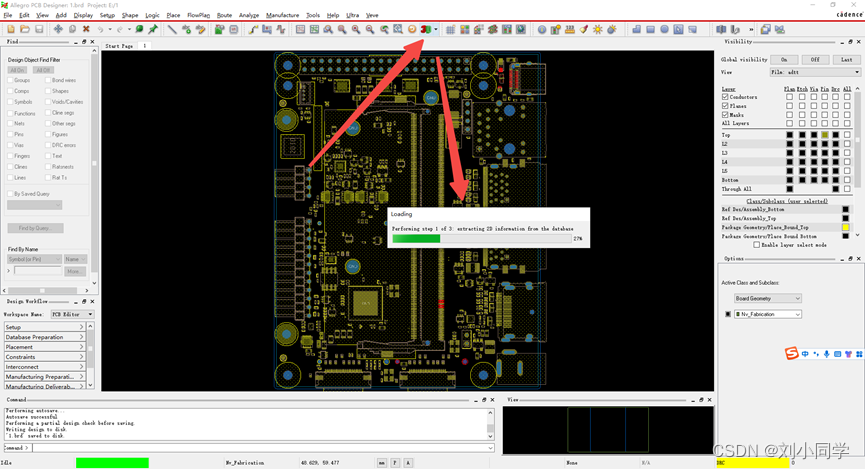

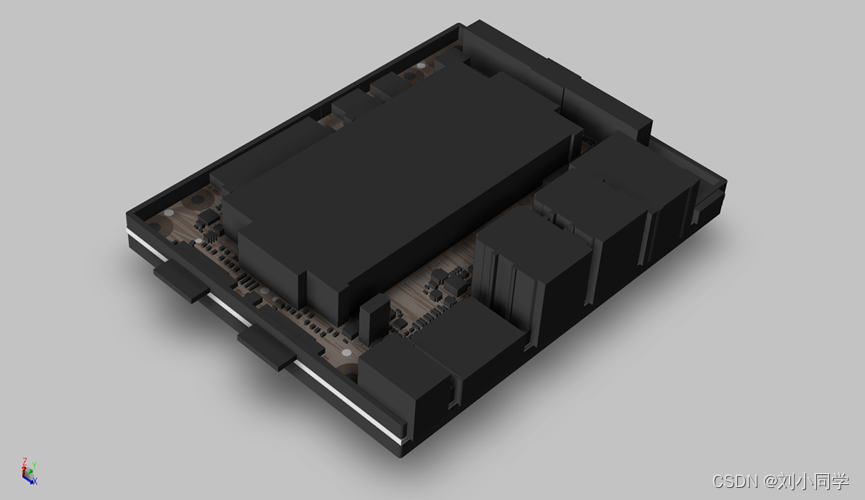

4.在Allegro中提前查看PCB的3D模型,点击3D,加载文件,如下图所示:

按照shift和鼠标中间滚轮,就可以翻转图形:

5.导出设置:在导出界面可多看到有三种类型:

STEP 203所有零件都在同一层,即所有的零件在一个图层中可以全部显示出来,而

STEP 214所有零件会有不同层,所以在查看时需要根据需求调用不同的图层。

STEP AP 242是基于STEP AP 203和STEP AP 214的基础上进行升级,将会兼容更多的数据。

5.在导出的3D模型,有时可以看到版外形不全的情况,如下图:

这时可以查看Borad Geometry 中的Cutout中是否有切割外形,上述情况可能是由于此层包含外形导致,删除铜皮,就可以显示完整的外形。

上一篇文章:Cadence Allegro PCB设计88问解析(二十九) 之 Allegro中泪滴的使用的链接如下,大家可以点击查看哟 ,链接: link

以上资料主要是本人在PCB设计中和网络搜索整理而成

如有雷同或错误,希望各位大神留言指正,感谢!!!