组合逻辑电路——编码器

概念

编码的概念:在数字系统中,常需要将有特定意义的信息编成二进制代码,这一过程称为编码。

编码器:实现编码的数字电路被称为编码器

二进制编码器

这里我们采用与非门来设计二进制编码器。二进制编码器输出端数量不定,可以根据需要来确定。

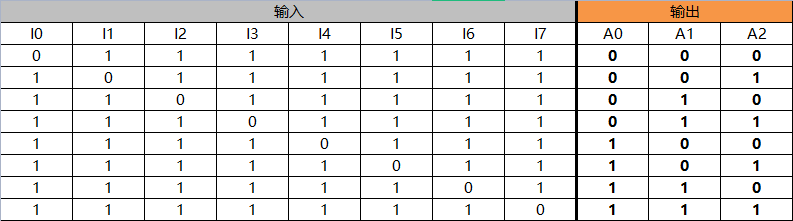

这里我们以三位(三输出端)二进制编码器为例,并将这三个输出端规定为A0、A1、A2

注:由于编码的唯一性,8个输入电平中只能有一个为低电平,所以不允许出现输入端00000000等含有多个0的情况(00000000仅是其中一个例子,还有其他情况)

)

)

A

0

=

I

1

⋅

I

3

⋅

I

5

⋅

I

7

‾

A_0 = \overline{I_1\cdot I_3\cdot I_5\cdot I_7}

A0=I1⋅I3⋅I5⋅I7

A

1

=

I

2

⋅

I

3

⋅

I

6

⋅

I

7

‾

A_1 = \overline{I_2\cdot I_3\cdot I_6\cdot I_7}

A1=I2⋅I3⋅I6⋅I7

A

2

=

I

4

⋅

I

5

⋅

I

6

⋅

I

7

‾

A_2 = \overline{I_4\cdot I_5\cdot I_6\cdot I_7}

A2=I4⋅I5⋅I6⋅I7

优先编码器

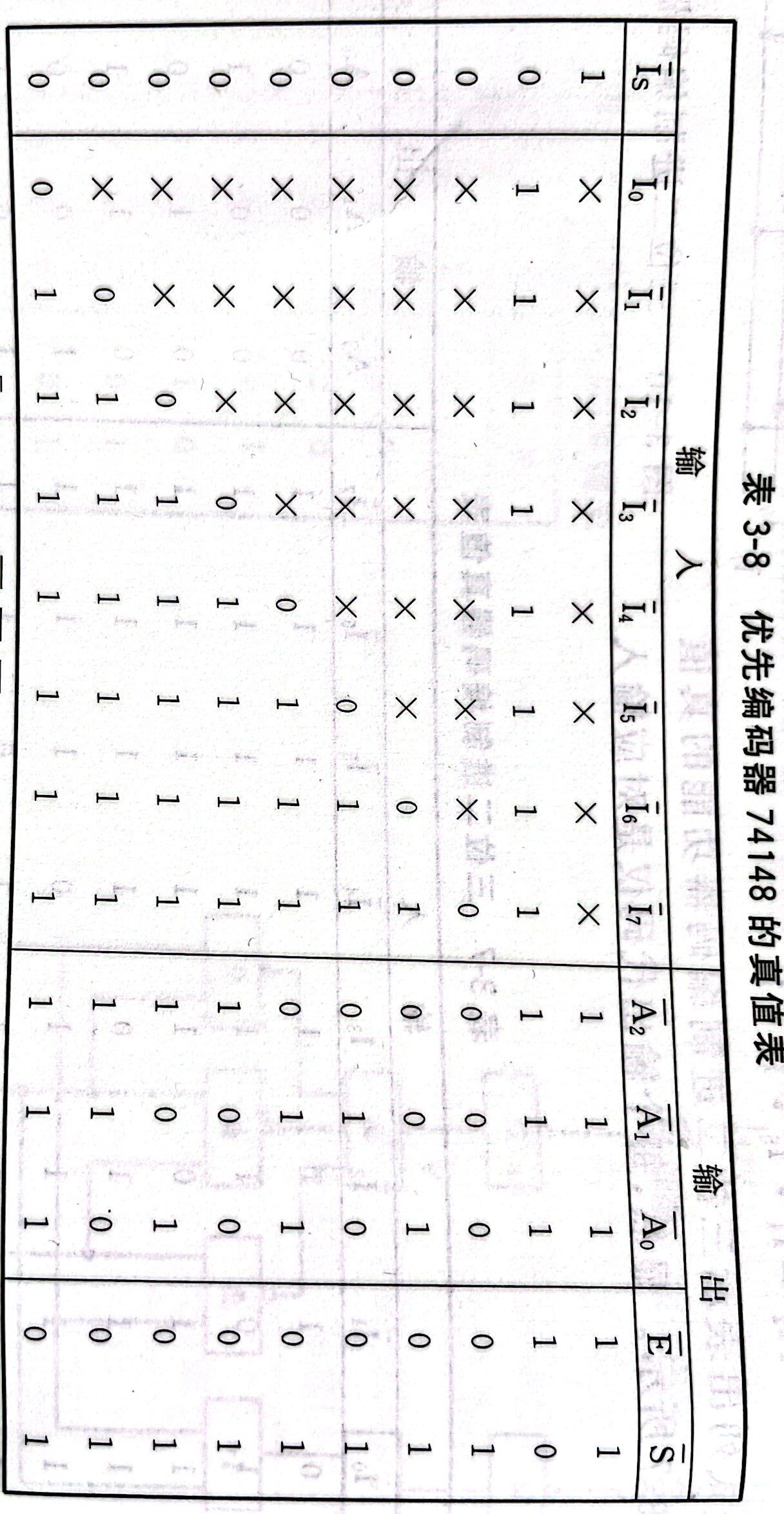

相对于二进制编码器,优先编码器允许同时在几个输入端加入有效信号,但是它根据设计编码器时已规定好的信号优先编码级别,选择其中优先级最高的输入信号进行编码。

本文以74LS148优先编码器为例

74LS148电路及真值表

74LS148原理

- !I_0~!I_7为输入端,优先级依次升高

- !I_S为控制端,只有当此端电平为低电平编码器才能正常工作

- !E为扩展端,用于扩展

- !S为选通输出端

- !A_0~!A_2为输出端

- 当无信号输入时,!A_0~!A_2输出全为1

- 由真值表可看出,输出为反码形式,比如7对应!I_7,且7的二进制应为

111,其反码为000,输出结果为000