数字电路器件

反相器

反相器是最基础的MOS器件,英文是inverter,一般缩写为INV。

反相器对信号有驱动作用,但是会使信号反相。

反相器由NMOS和PMOS组成,栅端(G)相连作为输入端,漏断相连作为输出端,NMOS的源端接地,PMOS的源端接电源VDD.

逻辑门

逻辑门(Logic Gates)是在集成电路(Integrated Circuit)上的基本组件。简单的逻辑门可由晶体管组成。这些晶体管的组合可以使代表两种信号的高低电平在通过它们之后产生高电平或者低电平的信号。高、低电平可以分别代表逻辑上的“真”与“假”或二进制当中的1和0,从而实现逻辑运算。

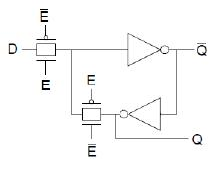

触发器

触发器类型:RS型、JK型、D型和T型(含T’型)触发器。工作中最常用的是D型触发器(D-FlipFlop)。

触发器是最基本、最重要的时序单元电路,也是构成时序逻辑电路的基本单元电路(时序逻辑电路具有记忆功能)

工作原理:

当无时钟脉冲作用(C=0)时,控制电路封锁,无论D为何值,与非门G3、G4输出均为1,触发器状态保持不变。

当时钟脉冲作用(C=1)时,若D=0,则门G4输出为1,门G3输出为0,触发器状态被置0;若D=1,则门G4输出为0,门G3输出为1,触发器状态被置1.

锁存器

所谓锁存器,就是输出端的状态不会随输入端的状态变化而变化,仅在有锁存信号时输入的状态才被保存到输出,直到下一个锁存信号到来时才改变。

由若干个钟控D触发器构成的一次能存储多位二进制代码的时序逻辑电路。数据有效迟后于时钟信号有效。这意味着时钟信号先到,数据信号后到。在某些运算器电路中有时采用锁存器作为数据暂存器。

Latch电路结构

当 E = 1 时,latch直传(transparent),D端信号的变化会即时反应在Q端;

当 E = 0 时,latch关断(closed),Q端保持关断瞬间D端的值。

设计中使用Latch的好处是,相比寄存器的面积更小,功耗更低。

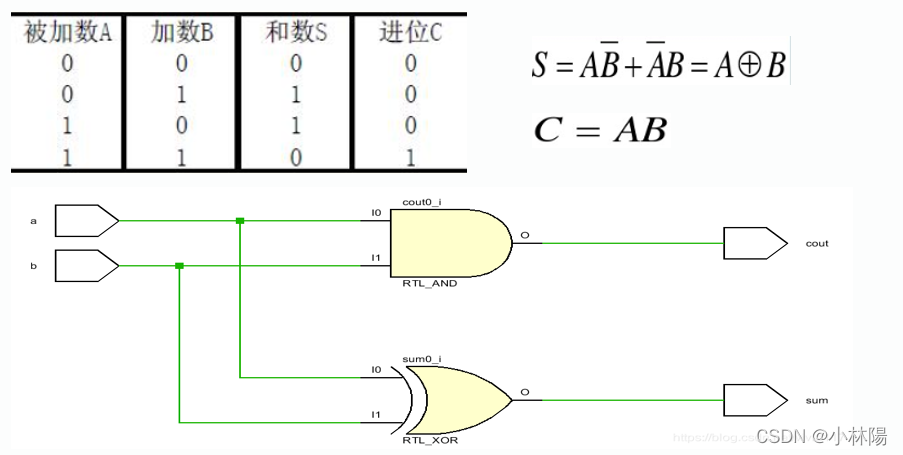

半加器

半加器不考虑低位进位来的进位值,只有两个输入,两个输出。由一个与门和异或门构成.

真值表/逻辑表达式/门电路图

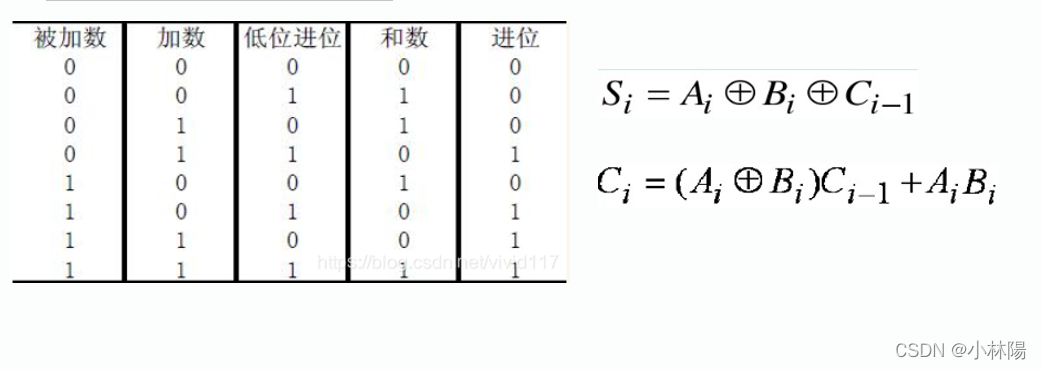

全加器

当多位数相加时,半加器可用于最低位求和,并给出进位数。第二位的相加有两个待加数和,还有一个来自前面低位送来的进位数。这三个数相加,得出本位和数(全加和数)和进位数。这种就是“全加"

真值表/逻辑表达式/门电路图

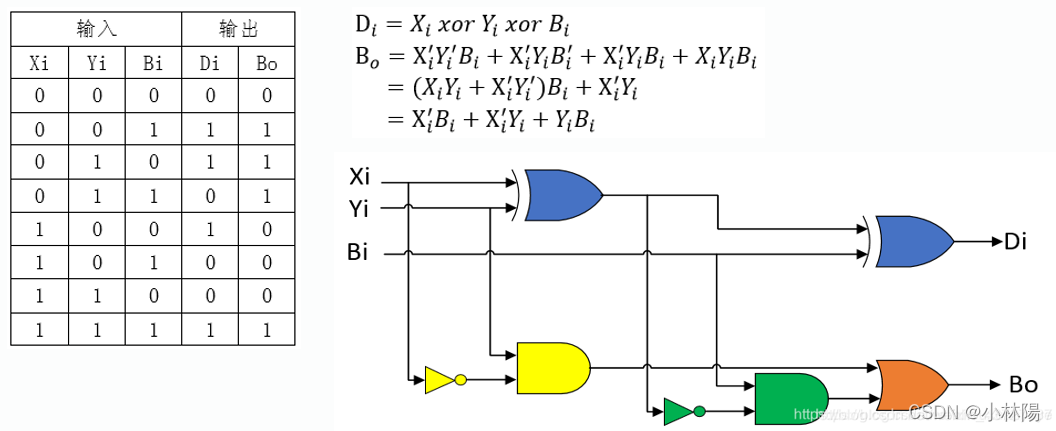

半减器

半减器用于计算两bitXi和Yi的减法,输出结果Di和向高位的借位Bo(Borrow output)

真值表/逻辑表达式/门电路图

全减器

全减器不同于半减器在于,全减器输入来自低位的借位Bi(Borrow input),另外两个输入xi、yi,输出为Di和向高位借位Bo

真值表/逻辑表达式/门电路图

数字后端常见Cell相关名词

buffer

理论上,buffer是由两个完全相同的inverter级联而成,但这不是标准库单元中设计buffer的做法。为了节省面积,buffer的第一级通常驱动很小,并且离第二级inverter很近,而第二级 inverter的驱动力更大。

数字电路中的buffer一般有两个作用:

1.提高驱动能力

buffer是一种宽高比很大的mos管,宽高比大意味着电流大,驱动能力高。

在扇出很大的wire中插入buffer可以提高带负载能力,常见于时钟树中。

2.确保信号时序正确

当一条wire很长时,延迟很大(delay正比于长度的平方,设长度为1,delay为1),这时在中间插入buffer,wire delay变为1/4+1/4=1/2,只要buffer delay小于1/2,则buffer的插入可以缩短wire delay。

当一条wire的延迟不大时,如果有hold violation(表现为数据到达过快,需要滞后到达),则插入buffer,利用buffer delay可以修正这个hold violation。

repeater

中继器,原理上buffer/inverter都属于中继器。

eco阶段经常使用ecoAddRepeater修复timing

使用方法:

ecoAddRepeater -loc {x y} -cell BUF_X4B_A9TR40 -net $net_name

delay cell

延迟单元,常用于data path上,相比较与buffer,可以添加更多的delay,用来修复hold timing。

它可以起到增加更多delay的作用,用来修复hold time的violation。但是驱动很弱,需要避免让它推动load较大的cell。

endcap cell

boundary cell,也被称为endcap Cell。Endcap是一种特殊的标准单元。

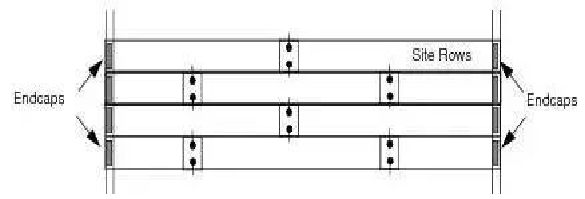

在后端物理设计中,除了与,非,或等一些常见的标准单元外,还有一些特殊的物理单元(physical cell),它们通常没有逻辑电路,不存在与netlist当中,但是对整个芯片的运行,稳定却起着举足轻重的作用。那endcap cell就是其中一种,它俗称为拐角单元,作用是确保每个nwell都是nwell enclosed,类似一个封闭环。主要加在row的结尾(两边都要加) , 以及memory 或者其他block的周围包边,如下图所示:

使用方法

create_tap_cells

tap cell

也被称为welltap cell。一种特殊的物理单元。

welltap是只包含well contact的cell,将衬底接到电源和地网络,避免衬底悬浮。主要防止CMOS器件的寄生闩锁效应(latch-up)

一般tap cell的作用范围是30~40um, 即每隔60um左右放置一个tap cell,具体的数据要参考工艺商给的document

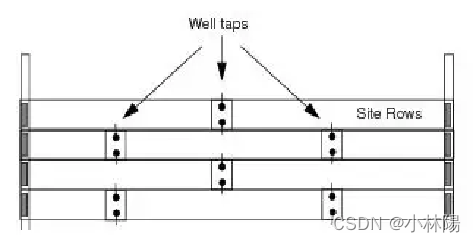

well tap cell一般交错摆放,类似棋盘分布。如下图所示:

使用方法

create_tap_cells

decap cell

去耦单元,增加电源的电容值。可以降低动态电压降。

在电源电压正常的时候,DECAP可以充电来存储能量,当电源电压较低的时候就可以放电来起到一定的缓冲作用。

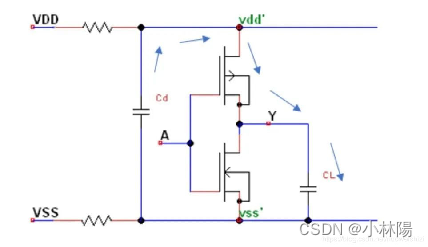

tie cell

tie cell(电压钳位单元),常见的有tie high,tie low两种,分别提供电源地电位。主要起到ESD保护的功能。通常在placement之后,route之前添加。

上图中,M1的栅极和漏极连接在一起,M1工作在饱和区,起到有源电阻的作用。A点的电位为高电位,M2始终导通工作在线性区,OUT1输出低电平。这样M1,M2组成了Tie low。同理,M3,M4组成了Tie high。

filler cell

通常是单元库中与逻辑无关的填充物,可以分为IO filler以及普通的standard cell filler

IO filler,也叫作pad filler,通常是用来填充I/O 单元与I/O单元之间的空隙。为了更好的完成power ring(电源环),也就是ESD之间的电源连接。通常是在Floorplan阶段时添加。

使用方法:

create_io_filler_cells

create_io_filler_cells -reference_cells FILLER

standard cell filler,也是为了填充std cell之间的空隙。主要是把扩散层连接起来满足DRC规则和设计需求,并形成power rails。这个在route之前,之后加都可以。

使用方法:

create_stdcell_fillers

create_stdcell_fillers -lib_cells {mylib/FILL_2X mylib/FILL_1X}

spare cell

spare cell就是备用的cell。 简单来说,就是每块地方洒一些类似SDFF,NAND,AND,XOR,INV等的备用cell, 为以后做function eco和metal eco用。

一般Foundry会提供一种服务,允许客户在量产工艺加工进行到某个阶段的时候,让部分wafer暂时停止,而部分wafer继续加工。这样的话,客户可以在加工到poly层时(后面的金属层还没有做),停止大部分wafer的进程,而让少量wafer继续加工到完成,然后对这些已完成的wafer上的die进行测试,如果发现有功能或时序上的问题,就可能通过预先布在die上的 Spare cell来解决。只是改动几层金属层光罩就可以完成standard cell重新连接,而不用改动standard cell的布局(要改poly层之前的所有光罩)。那些暂停加工的wafer这时就可以用新的金属层光罩往后加工,于是在silicon和光罩两方面都降低了成本。

使用方法:

add_spare_cells

add_spare_cells -cell_name spare1 -lib_cell {AND2 OR2} -num_instances 250

clock gating cell

时钟门控单元。为了减少时钟网络中的功耗消耗,最直接的办法就是如果不需要时钟的时候,就把时钟关掉。这种方法就是门控时钟。

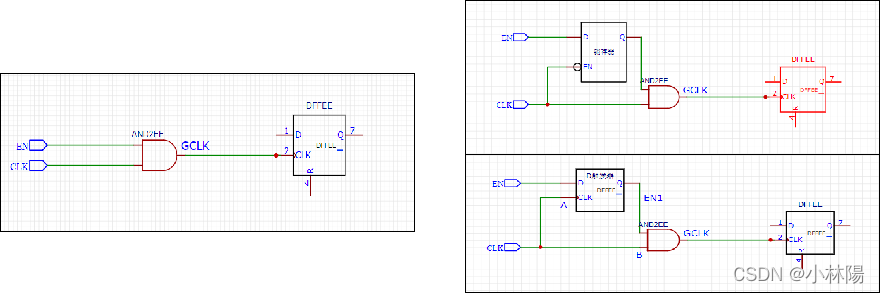

更具控制方法的不同,一般可以分与门门控、锁存门控、寄存门控。实际soc设计用的最多的是锁存结构的门控时钟。

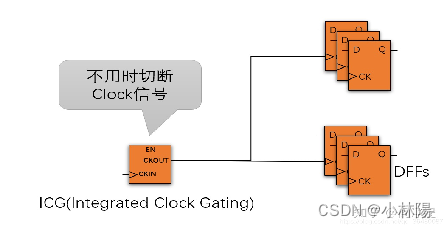

ICG cell

1.什么是ICG?

为了节约动态功耗,最初有个十分简单的想法:在芯片实际工作过程中,有些信号或者功能并不需要一直开启,那么就可以在它们不用的时候将其时钟信号关闭。这样一来信号不再翻转,从而能够有效减少动态功耗,这就是Clock Gating。

可以看到在加入Clock Gating之后,DFF的clock信号前多了一个使能端EN,从而可以控制该时钟信号的打开与关闭

一般每个ICG会控制一个或多个DFF,通过某个DFF传递过来的控制信号控制ICG的开启或者关断。

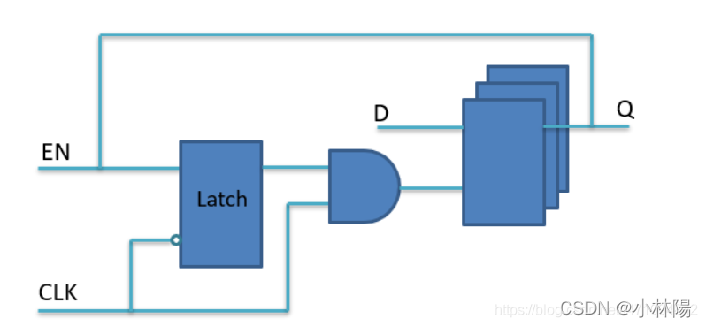

2.clock gate cell 时钟门控单元结构图

latch或reg:用于同步使能信号,防止出现亚稳态和毛刺。

与门:使能信号无效时,关断模块输入时钟。

D触发器:简化的reg。

3.为什么要使用ICG?

在数字IC设计中,时钟树的功耗占比可能高达30%,而使用ICG电路后,可以从两个方面节省功耗:

1.减少了时钟端的翻转

2.使用ICG的电路资源消耗相对减少

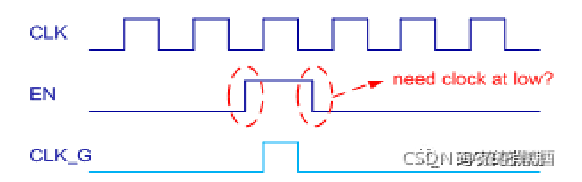

4.如何clk gate?

将一直翻转的时钟变为en有效才翻转的时钟,即将CLK转化为CLK_G。

#以上是从各个网页收集整理,如有侵权请告知。