Quartus分配管脚(Pin)

1.在打开项目,点击选项Assignments->Pin Planner,入下图所示

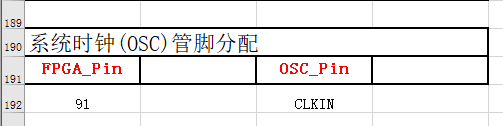

2.根据板子DataSheet给的管脚分配信息,给各输出输入的location选择pin

2.1例如我需要给时钟信号分配对应的管脚,知道50MHZ晶振提供的信号来自PIN_91

2.2在Pin Planner给clk选择PIN_91

2.3最终给各节点分配好对应的输入和输出

本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有涉嫌抄袭侵权的内容,请联系:hwhale#tublm.com(使用前将#替换为@)