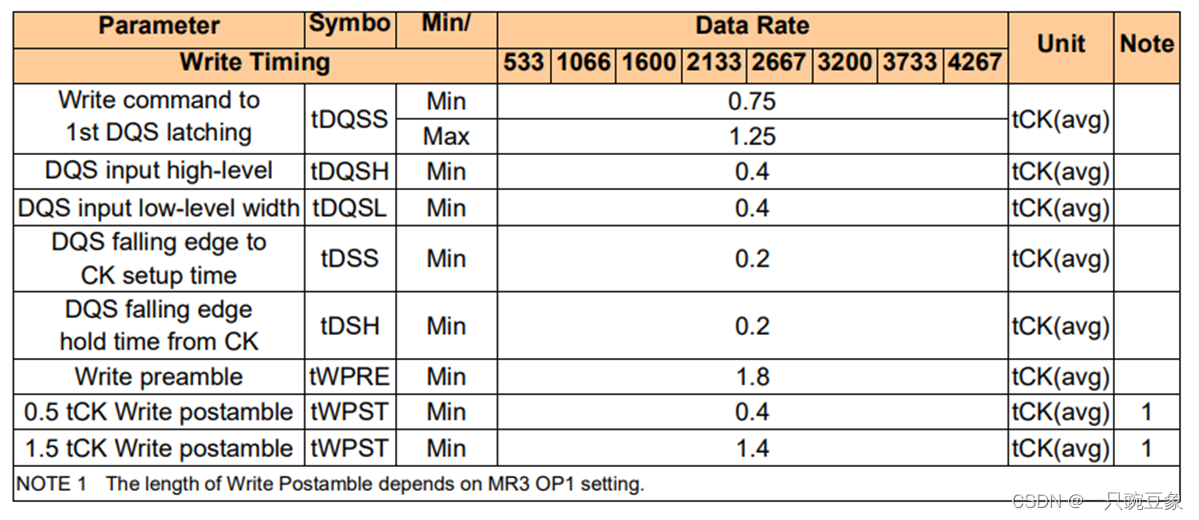

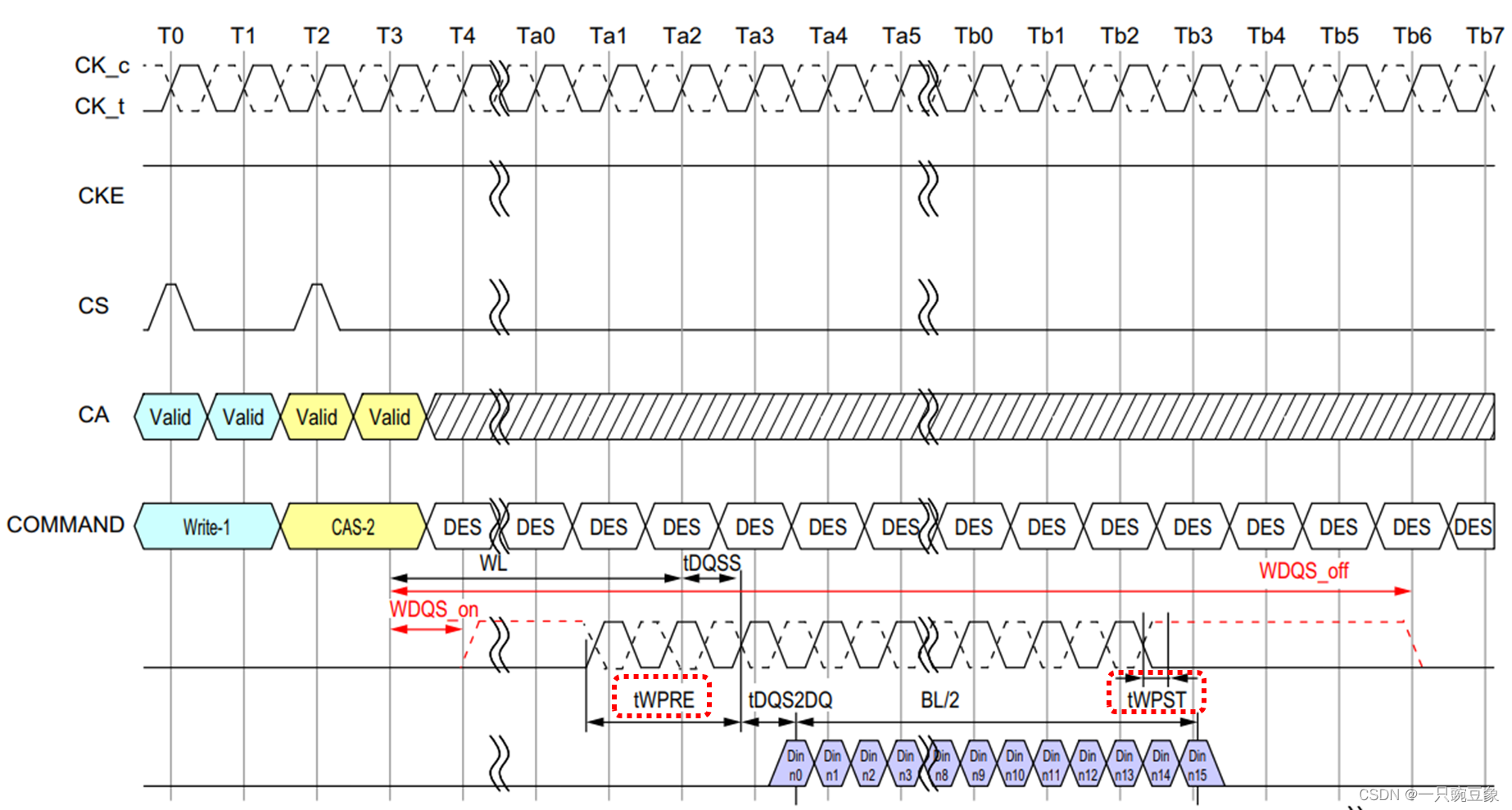

在LPDDR4的JEDEC标准中,写操作相关的时序参数要求基本都是围绕DQS信号,如下图所示,图中的单位“tCK”指的是时钟信号的工作周期:

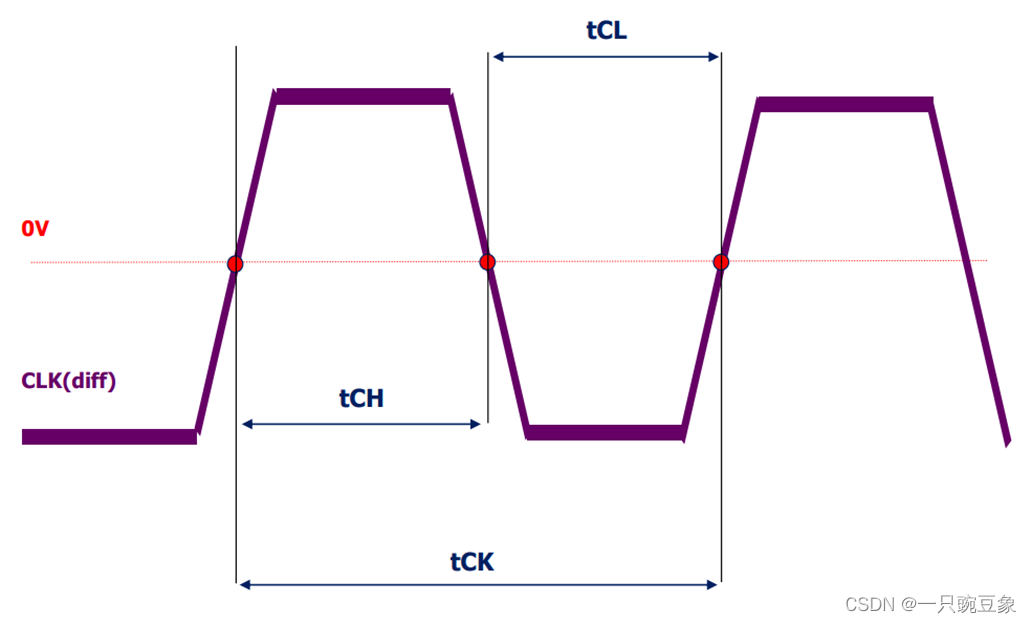

tCK的测试方法如下图所示:

Write preamble and postamble设置

这一步对于测试之前的设置来说,非常关键,如果设置不当,将导致时序测试产生偏差。

以LPDDR4为例,在锁定DQS_t的第一个有效上升沿时,需要留有一定的缓冲时间进行预判(或者说“定位”),对于写操作,所有工作频率下都需要一个2*tCK时间长度的DQS前置差分工作信号,这就是write preamble,即下图中红色虚线框的tWPRE。

而在DQS完成工作后,还需要持续0.5*tCK或者1.5*tCK时间长度的DQS后置差分工作信号,写操作才被允许完全结束,这就是write postamble,即下图中红色虚线框的tWPST。

做好preamble and postamble的配置后,方可开始进行时序的测试。

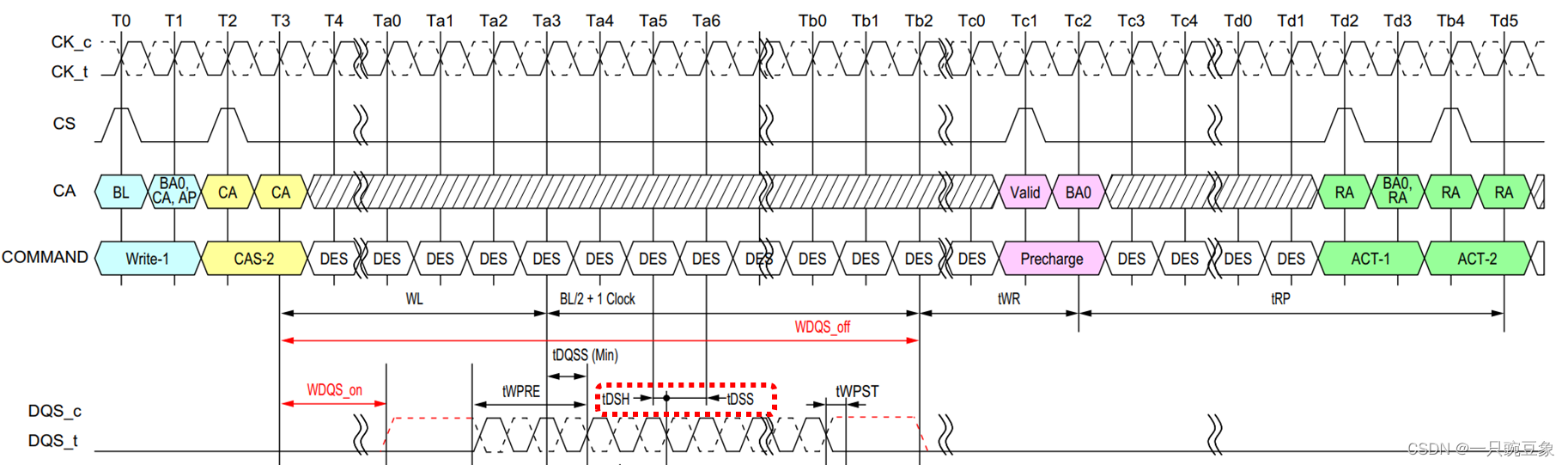

tDQSS: write command to 1st DQS latching

DRAM 写入中最重要的,不能违反的时序参数是 tDQSS,表示数据有效信号 DQS 与时钟信号 CK 的相对位置。tDQSS 必须在协议规定的 tDQSS(MIN) 和 tDQSS(MAX) 之间。如果 tDQSS 超出规定的限制,那么可能会写入错误的数据。

测试中,如果时钟信号交叉点与第一个锁存的DQS交叉点之间的时间差大于0.5UI,则将结果视为tDQSS,如果小于0.5UI,则需要再向前多定位一个时钟周期的交叉点,其在波形中的具体位置,可由上图中查找到。

如下图所示,是tDQSS的测试实例:

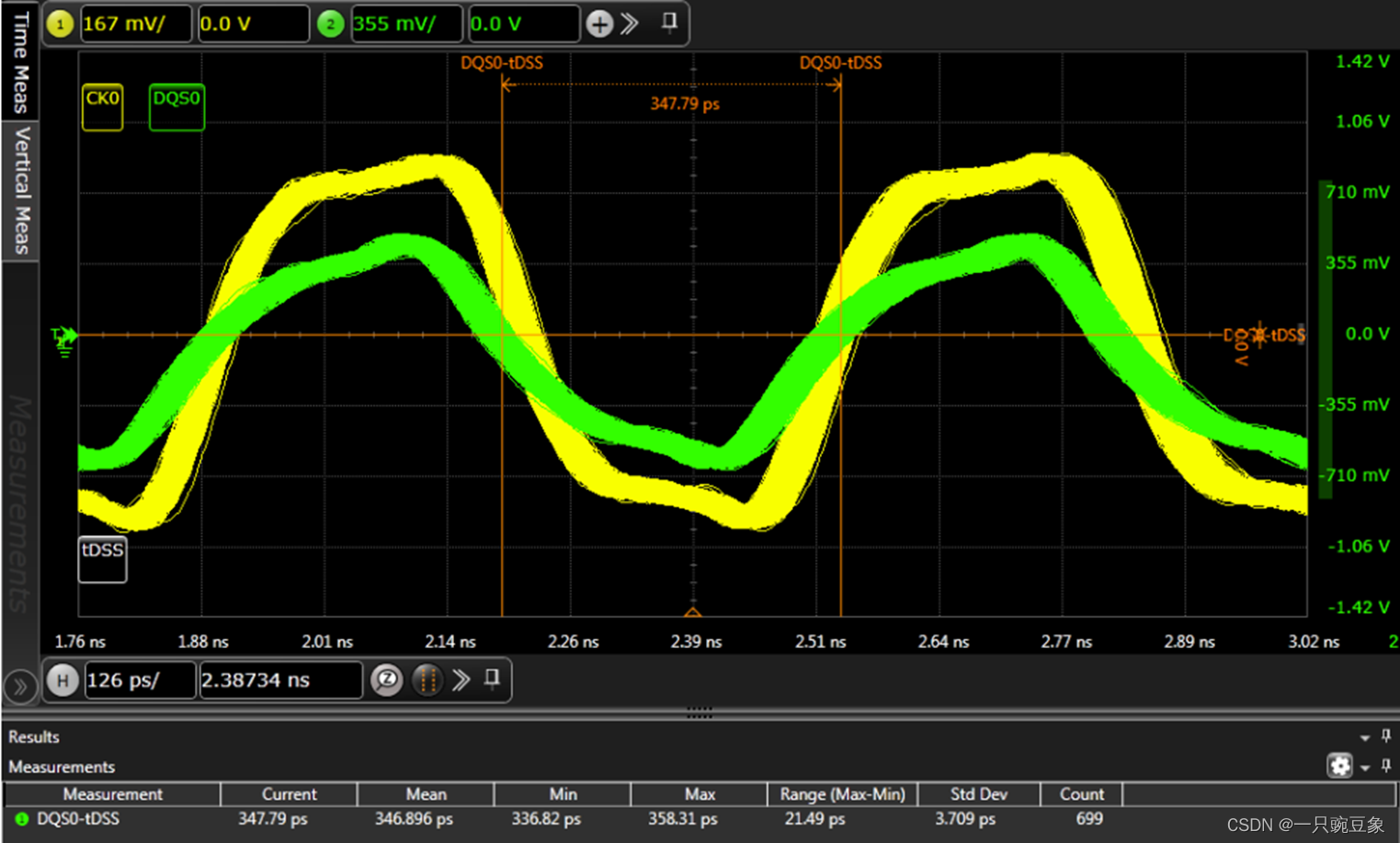

tDSS: DQS falling edge to CK setup time

测试从数据有效信号DQS的下降沿交叉点开始,到其后面紧邻的时钟信号CK的上升沿交叉点结束;

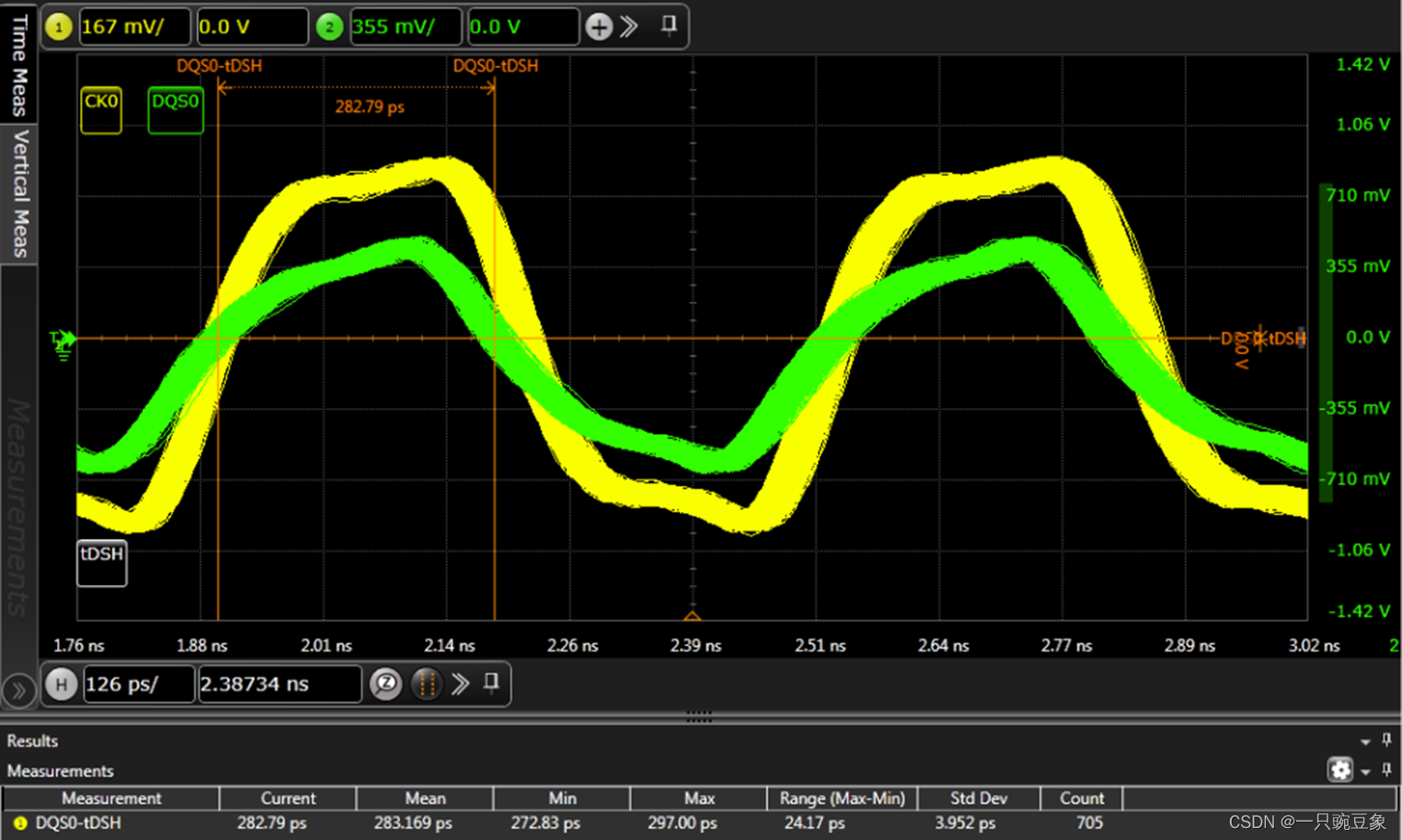

tDSH: DQS falling edge hold time from CK

测试从数据有效信号DQS的下降沿交叉点开始,到其前面紧邻的时钟信号CK的上升沿交叉点结束;

具体参数位置,如下图中虚线红色框所示,可以看到其具体对应的边沿关系。

如下图所示,是tDSS的实测波形:

如下图所示,是tDSH的实测波形:

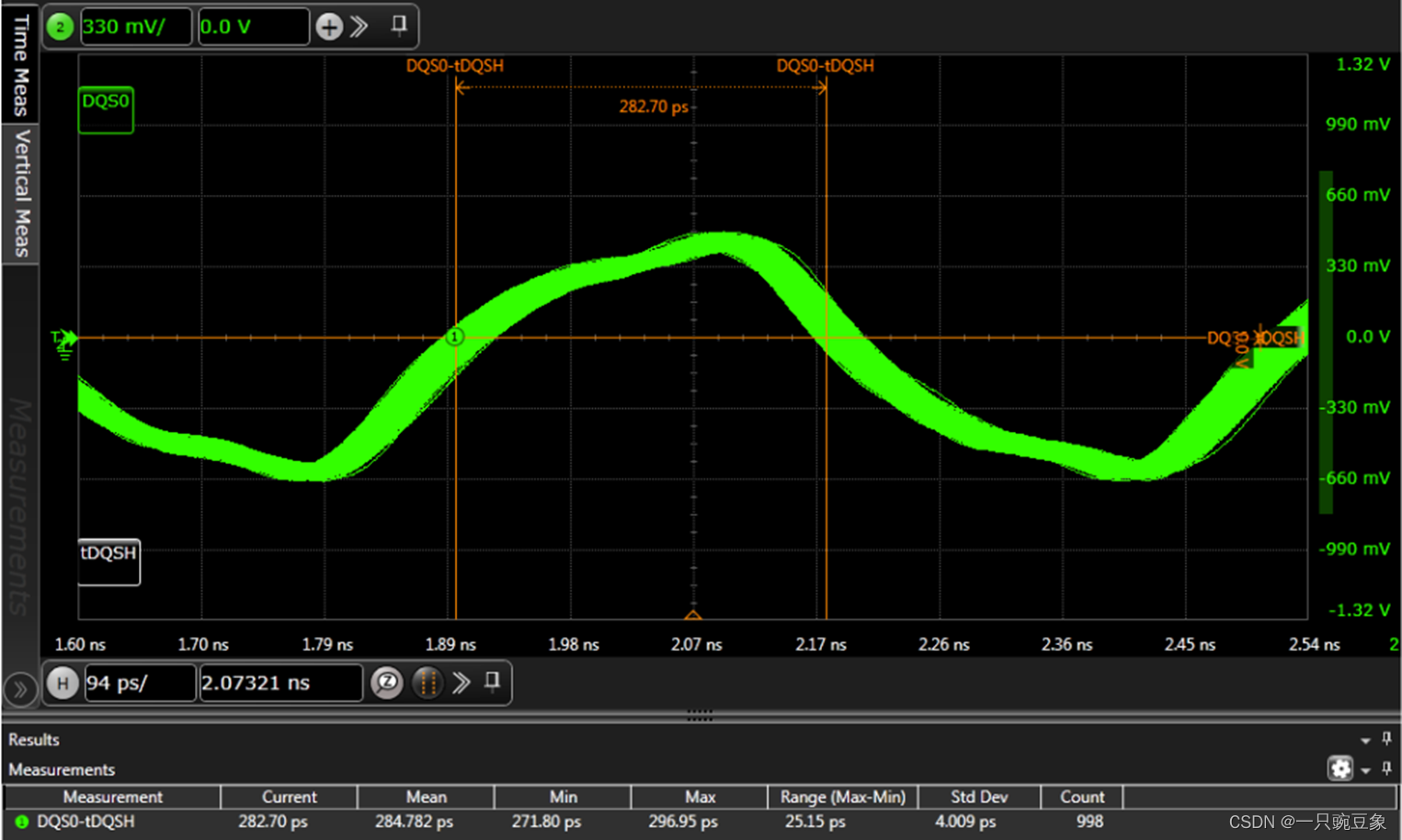

tDQSH: 用于验证DQS信号高电平的有效宽度;

tDQSL: 用于验证DQS信号低电平的有效宽度;

如下图所示,测试从前一个DQS的差分交叉点开始,紧邻的下一个差分交叉点结束,分别测量上升和下降沿。

如下图所示,是tDQSH的实测波形:

如下图所示,是tDQSL的实测波形:

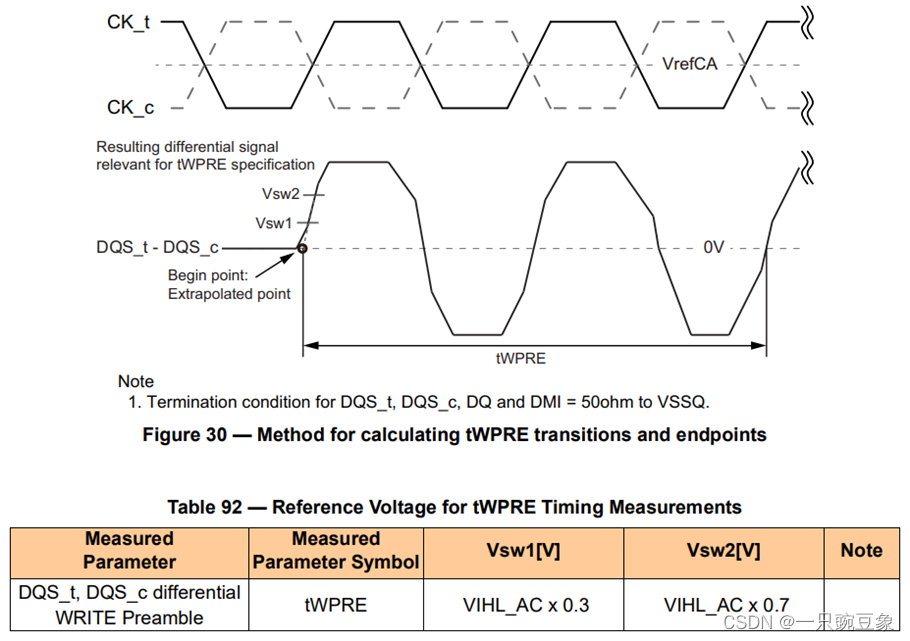

tWPRE: 用于验证write preamble的时间,测试从DQS置为高电平开始,到第一个写有效的DQS_t上升沿结束;

具体的测试方法如下图所示,需要注意找到处于写操作下的第一个DQS差分信号上升沿,在此上升沿中以Vsw1&2的直线斜率找到其测试起始点,并找到两个DQS周期后上升沿交叉点做为结束点,两个交叉点之间的时间即tWPRE。

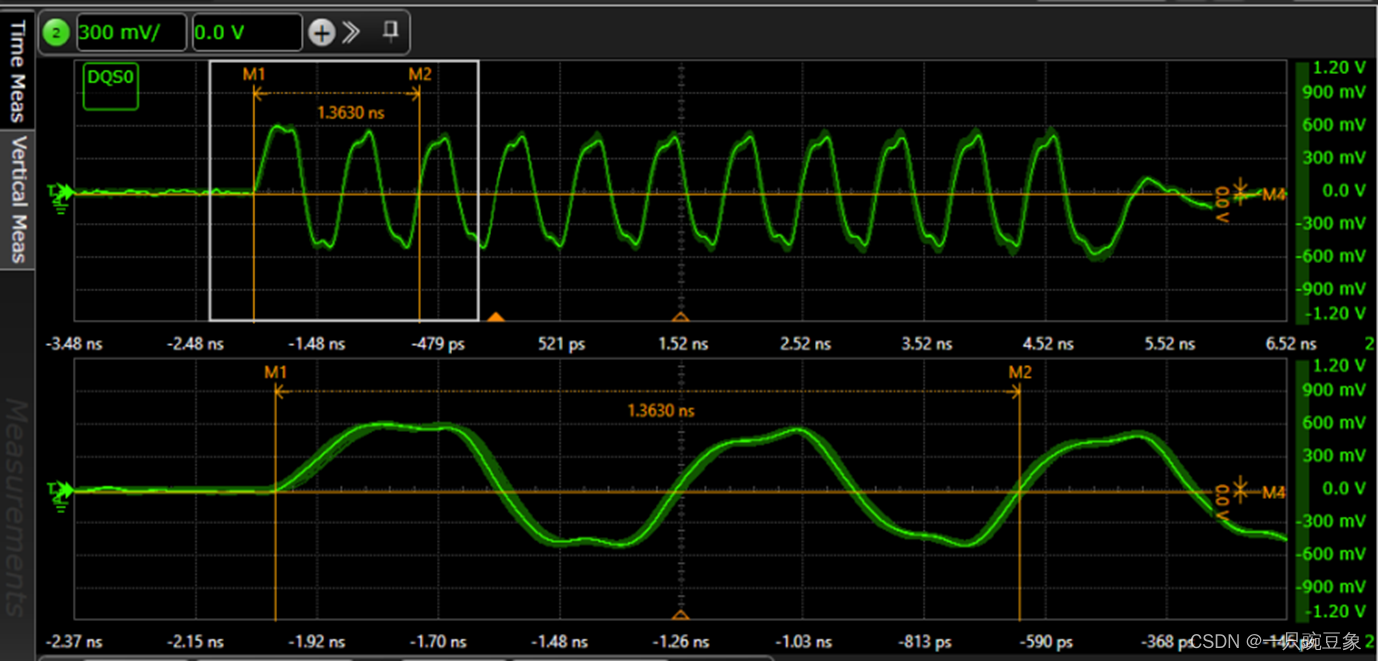

如下图所示,为tWPRE的实测波形:

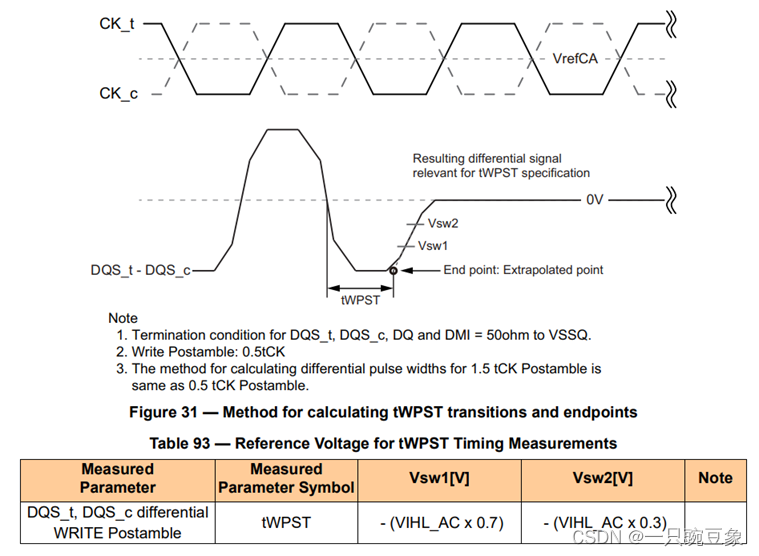

tWPST: 用于验证write postamble的时间,测试从最后一个DQS_t的下降沿开始,到DQS驱动被释放结束;

具体的测试方法如下图所示,需要注意找到处于写操作下的最后一个DQS的下降沿交叉点做为起始点,并在紧邻其后的上升沿中以Vsw1&2的直线斜率找到其测试结束点,两个交叉点之间的时间即tWPST。

而在手动测量中,上述两个参数测试点的选取,往往就只是粗略地取到DQS的差分交叉点即可,精度上要求不高。

如下图所示,为tWPST的实测波形,可以看出,实际中采用了扩展的1.5*tCK后置信号:

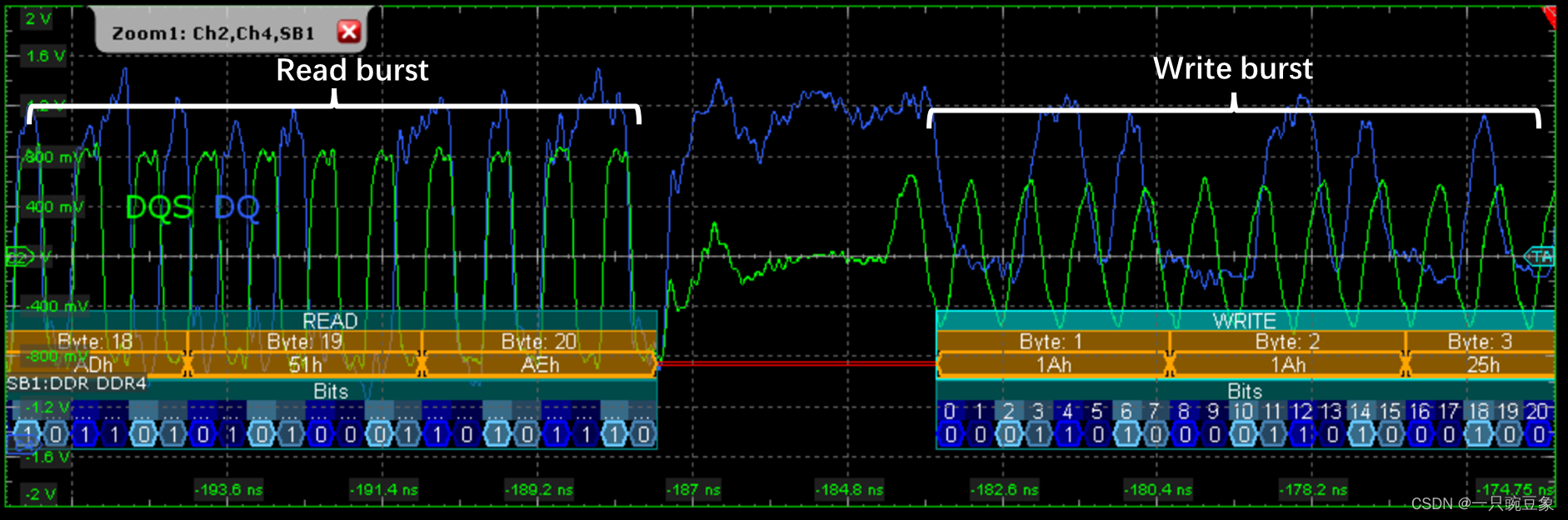

另外,读写操作信号其实是比较容易区分出来的,如下图所示,当DQS和DQ信号处于write burst状态下时,两者边沿是具有一定的相位差的,标准应当是DQS的双沿处于DQ的眼图的正中间,而处于read burst状态下时,边沿是完全同步,没有相位差的。

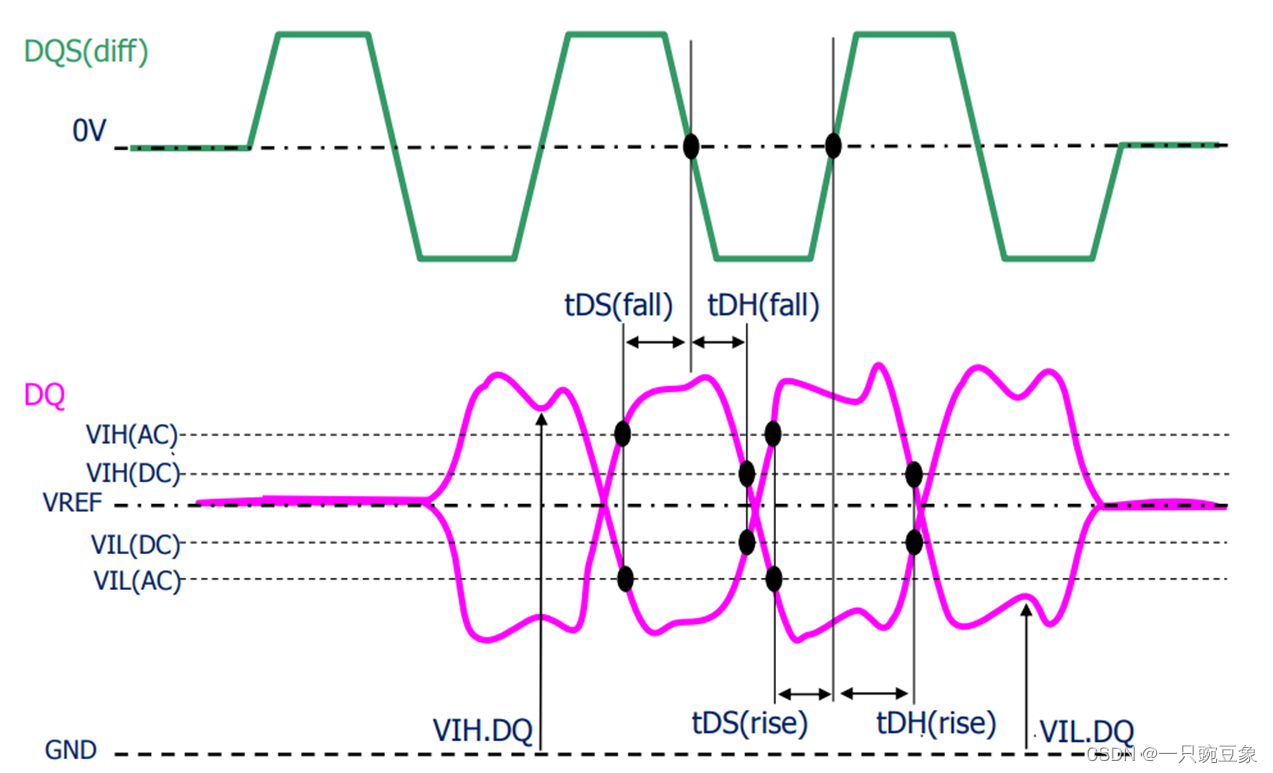

除此之外,在LPDDR4的JEDEC标准中,并没有直接给出如下图所示的DQS与DQ信号之间tDS和tDH的相关定义,而是通过眼图模板定义来涵盖这项指标;

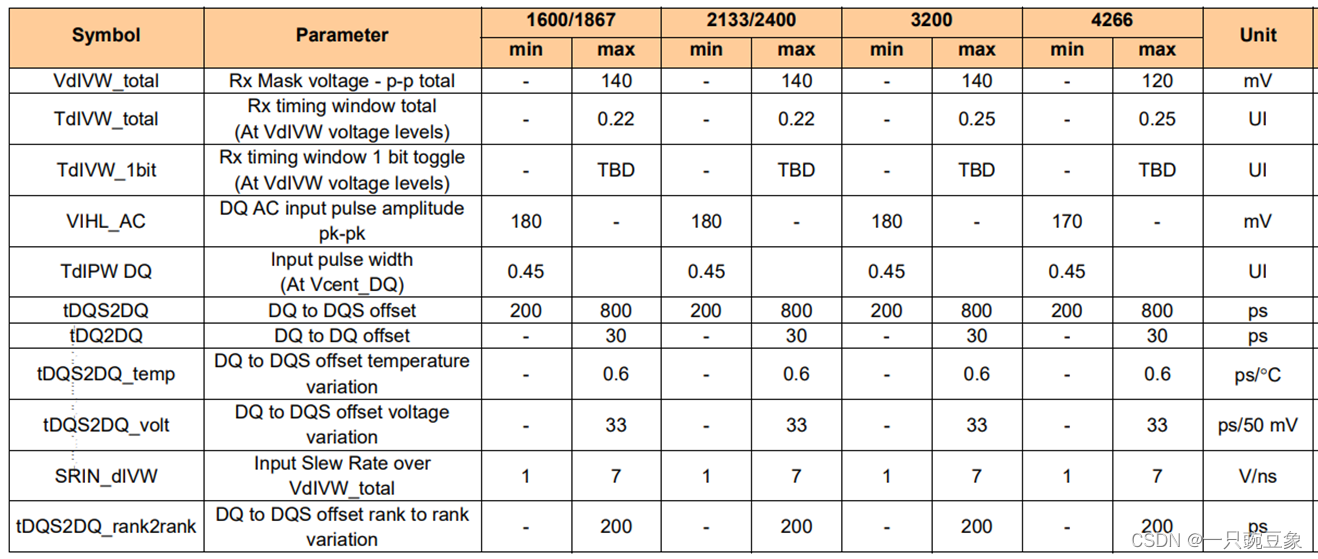

写操作下的眼图模板参数定义如下图所示,需要关注的参数主要有:tDIVW、vDIVW、SRIN_dIVW、tDIPW、tDQS2DQ、DQ_VIHL_AC、tDQ2DQ,接下来,对这些参数进行一一说明;

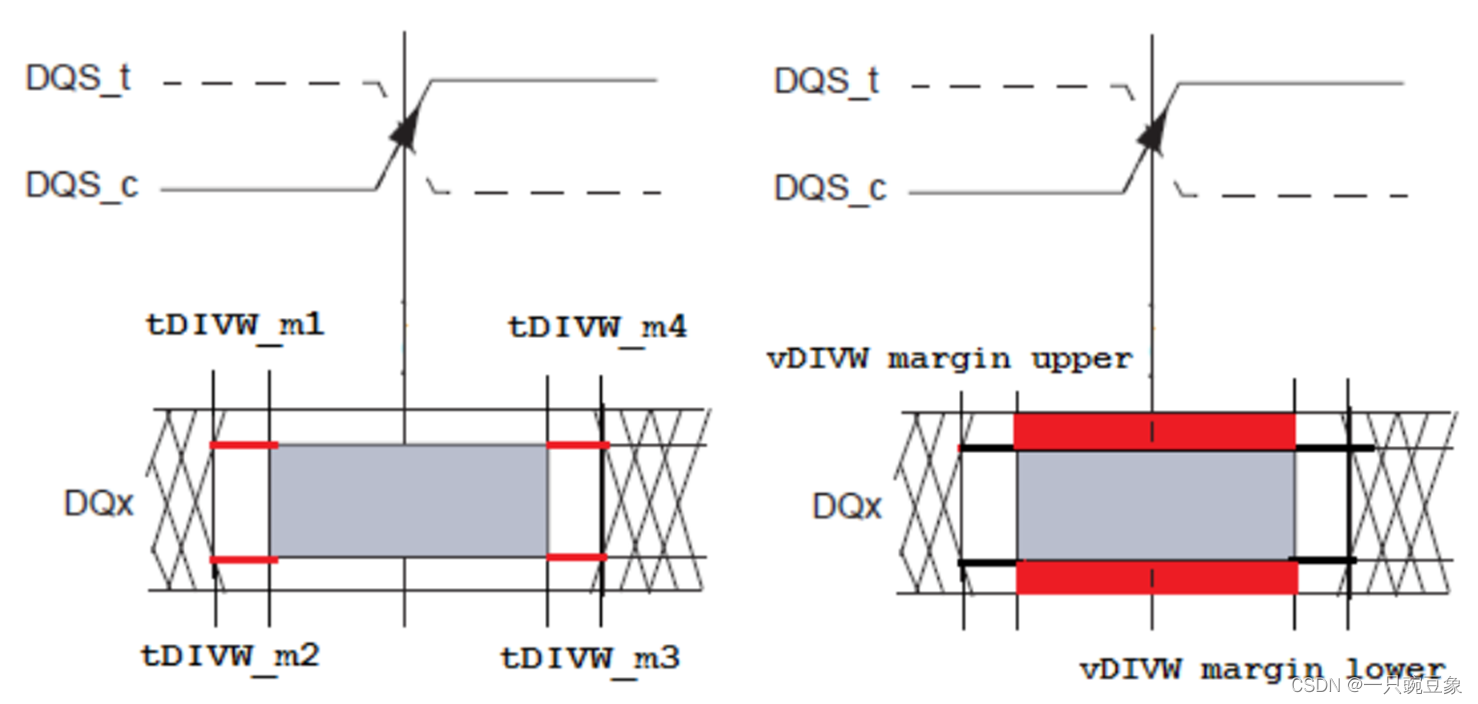

tDIVW和vDIVW的定义如下图所示,分别指的是DQ信号眼图的时间宽度和电压幅度限制值,需要根据信号速率在上表中进行选择,这不是测试项,而是一个测试的固定参考值的选取;

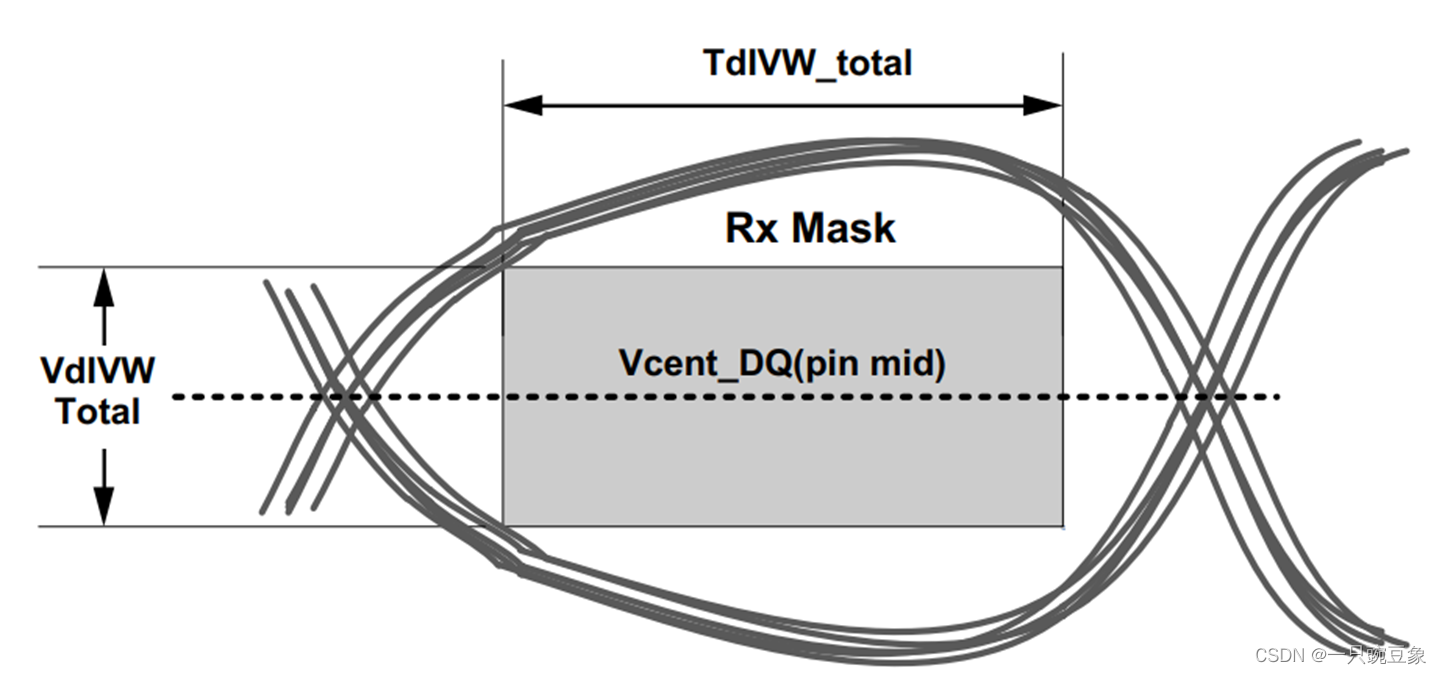

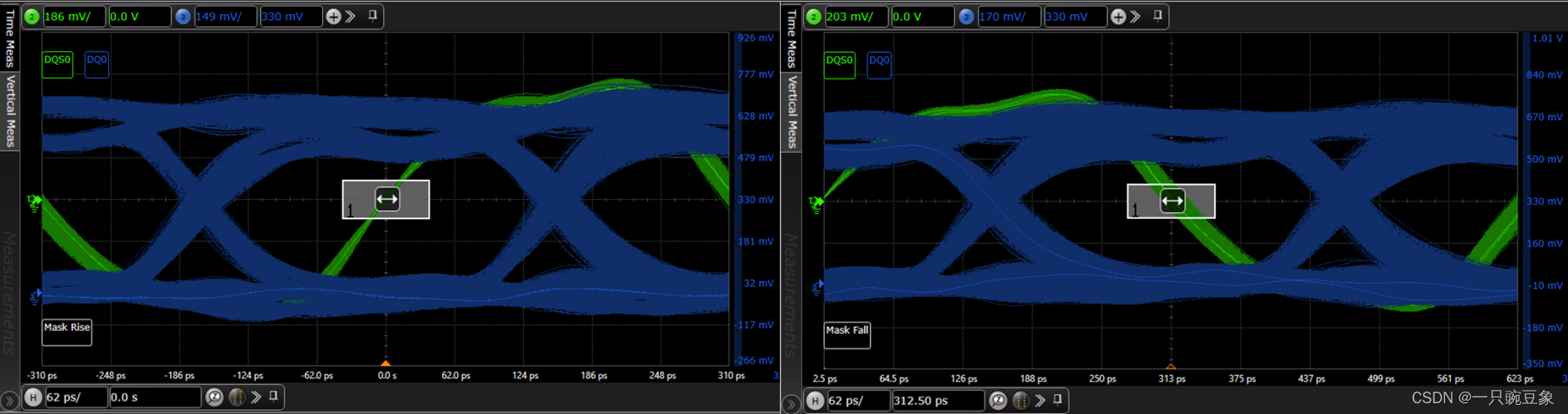

如下图所示,为实测的眼图结果,中间的方框即由tDIVW和vDIVW 组成的矩形眼图模板,眼睛张开的程度,应当不能碰触到该限制区域,测试分别在CK信号的上升和下降沿采样中完成:

根据结果,还可以得到tDIVW和vDIVW的最小裕量(如下图中红色区域所示),用于评估设计是否留有足够的优化空间:

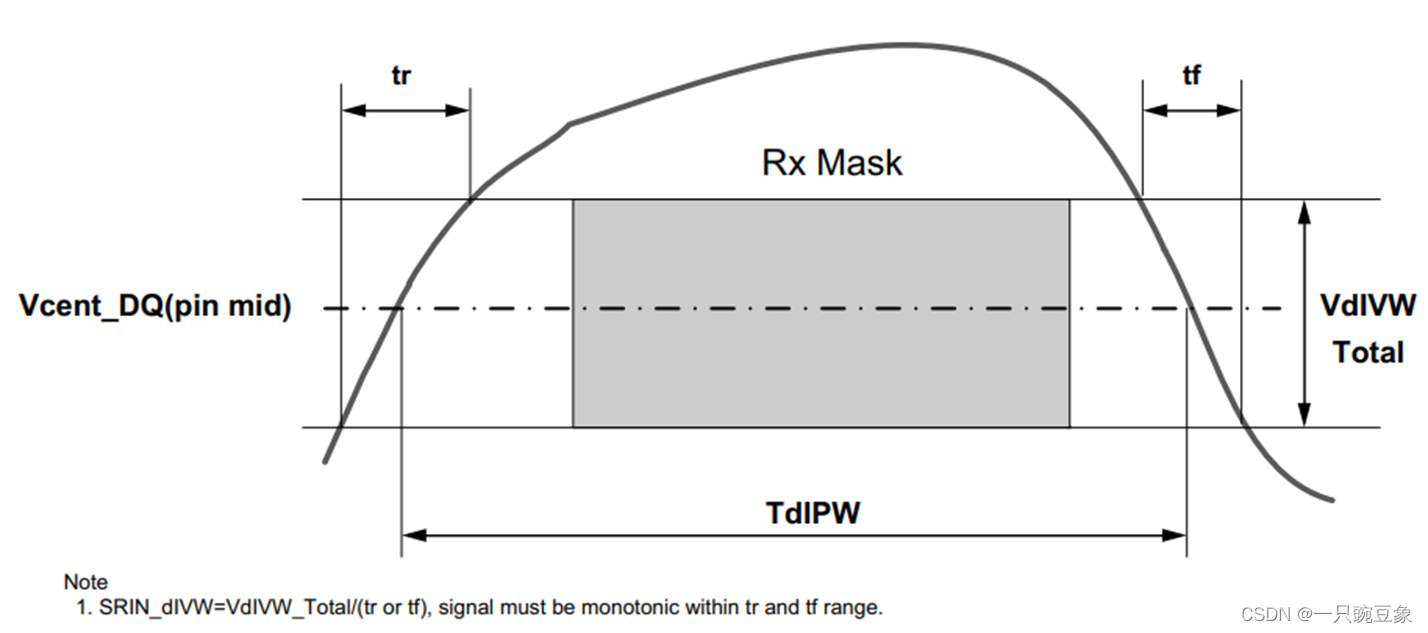

SRIN_dIVW,用于验证处于vDIVW电压区间内的信号边沿斜率,即下图中的tr和tf值;

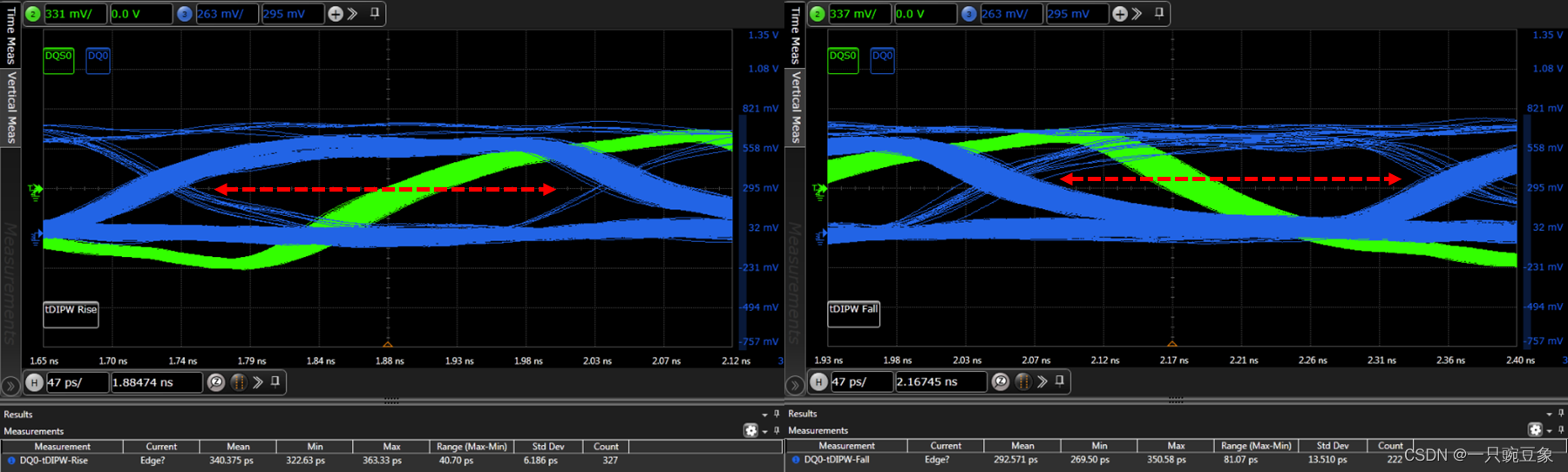

tDIPW,用于验证在Vcent_DQ上定义的最小DQ输入脉冲宽度,也可以理解为vDIVW的一半处;

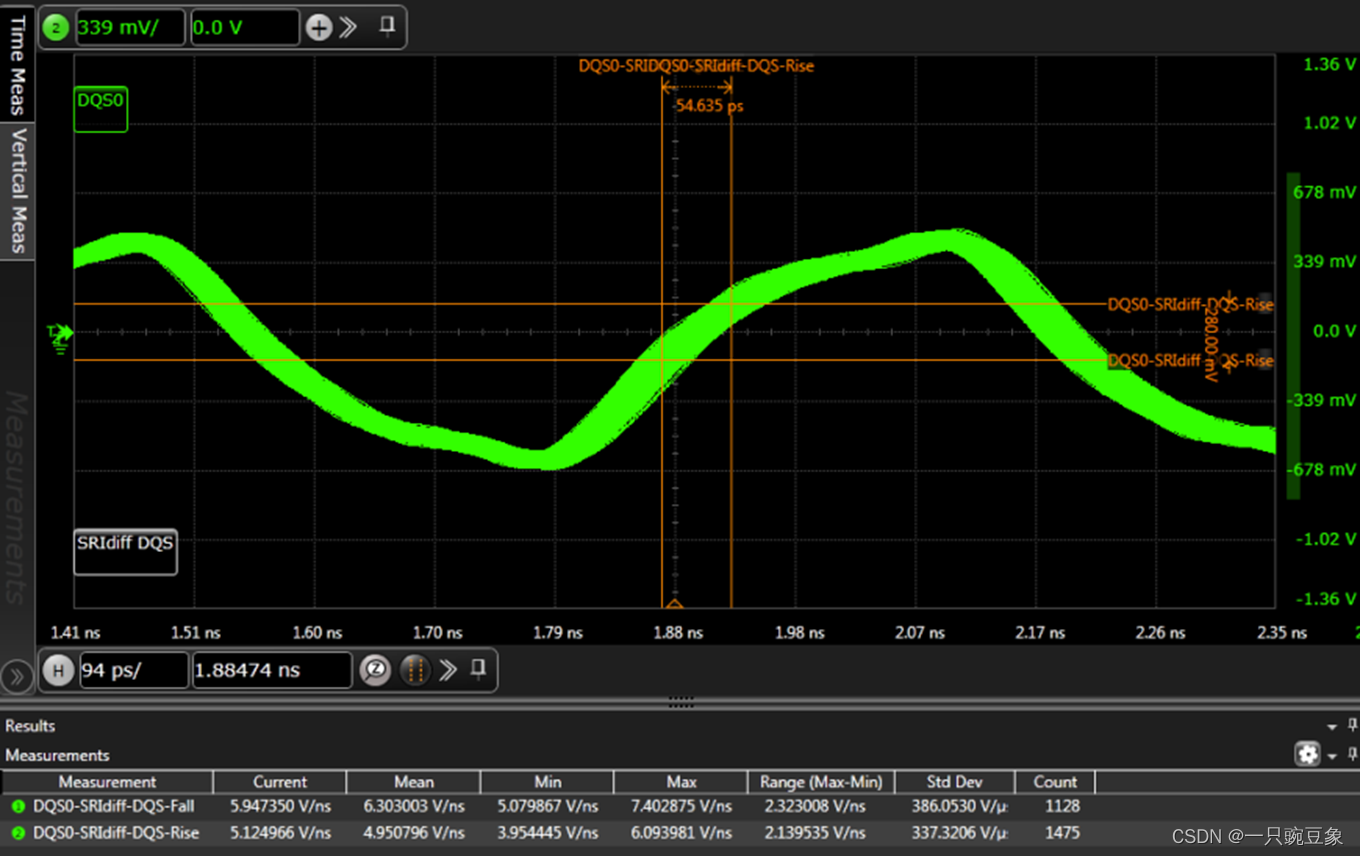

如下图所示,为SRIN_dIVW的实测波形:

如下图所示,为tDIPW的实测波形,分为DQS的上升和下降沿采样:

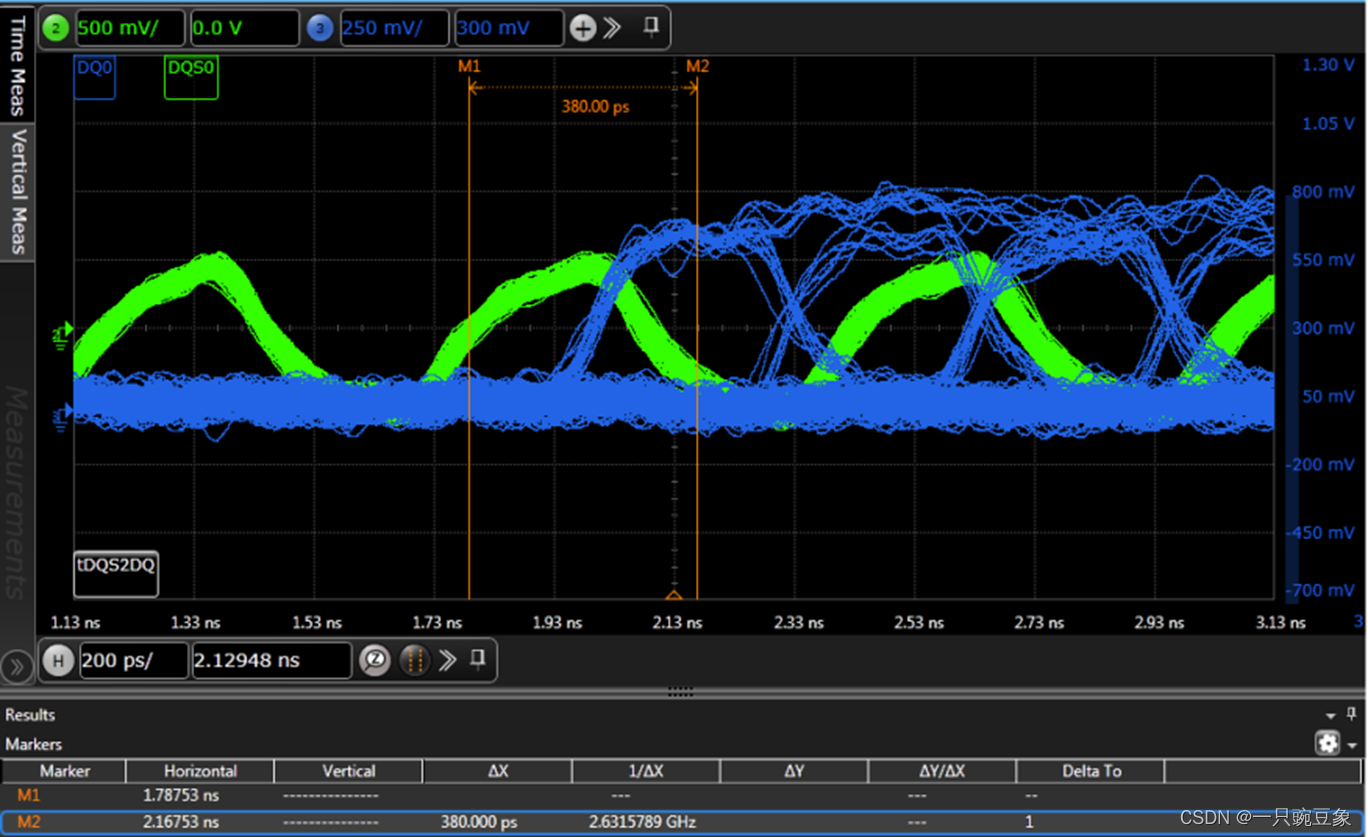

tDQS2DQ ,用于验证DQS相对于DQ的时间差值,如下图所示,因为在DDR设计中,要求DQS需要先于DQ信号到达BGA ball,这个提前的时间差需要控制,以保证DQS到达芯片内部die时处于最佳的采样点;

如下图所示,为tDQS2DQ的实测波形:

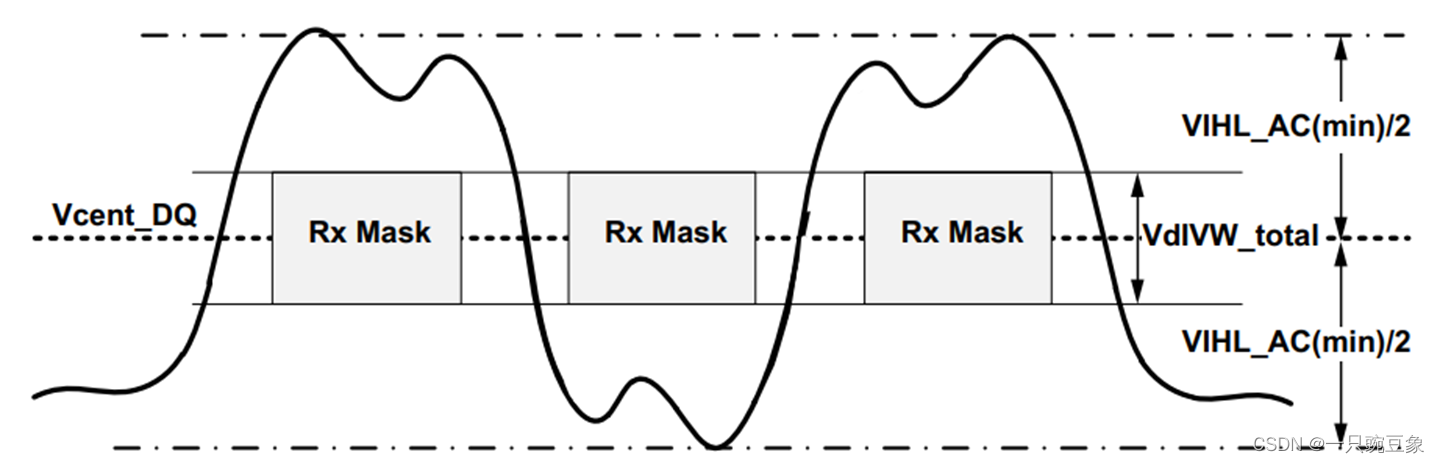

DQ_VIHL_AC,用于验证以Vcent_DQ为中心的峰峰值电压是否满足要求;

如下图所示,为DQ_VIHL_AC的实测波形:

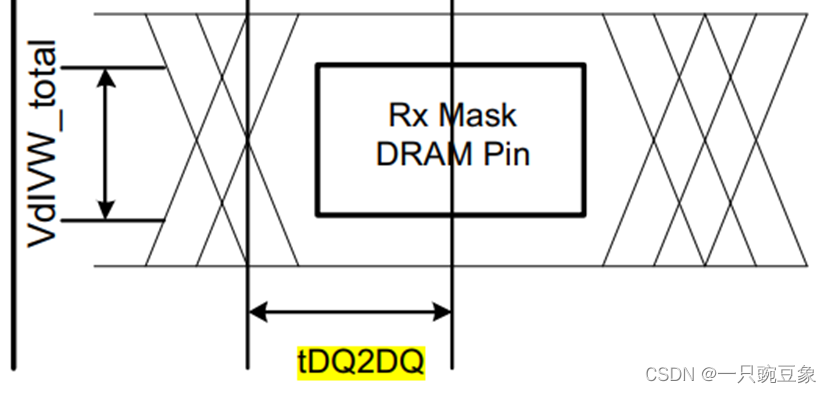

tDQ2DQ ,用于验证组内各个DQ信号相对于眼部模板时间中心处的偏差值,其测试原理是:由于每个DQ信号都存在不同程度的延时以及抖动,因此其边沿会呈现正态分布,由此带来的时间偏差变化量必须控制在一定的范围内,才可以保证组内数据传输的可靠性,但是,由于DQ数量众多,在测试中不可能全部测量,更多的需要靠仿真来进行评估。