目录

1、TF/SD走线要求

2、HDMI走线要求

3、LVDS信号线走线要求

4、DVP信号走线要求

5、eDP信号走线要求

6、MIPI信号线走线要求

7、USB走线要求

8、MAC走线要求

9、BT.1120走线要求

10、FLASH(SPI FLASH / NAND FLASH /eMMC)走线要求

11、PCIE2.0,PCIE3.0走线要求

PCIE2.0:

PCIE3.0:

1、TF/SD走线要求

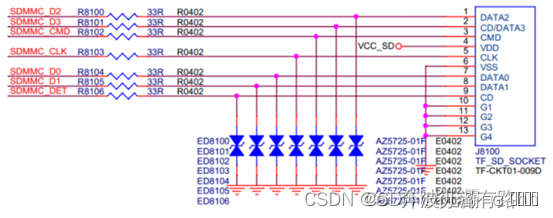

TF card电路兼容SD2.0/3.0,模块供电为输出可调的VCC_SD,默认为3.3V供电。

当插入SD 2.0存储卡时,模块供电与TF卡供电均为 3.3V,TF卡正常工作。

当插入SD 3.0存储卡时,主控芯片识别其为SD 3.0存储卡,调节VCC_SD供电为1.8V,以满足高速卡信号要求;同时TF卡供电VCC_SD通过卡片内部LDO,生成1.8V为TF卡提供电源。

SD卡走线为单端线,控制阻抗50欧姆;

1)VCC_SD的滤波电容靠近卡座引脚放置,遵循先大后小的原则。

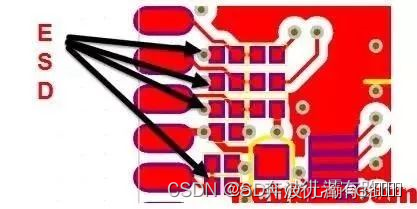

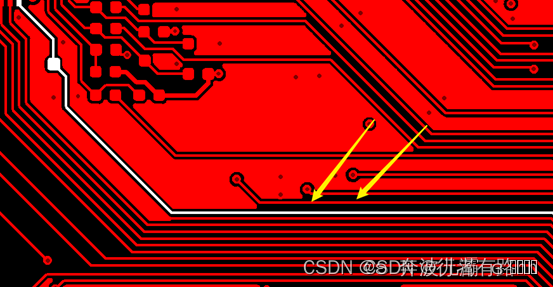

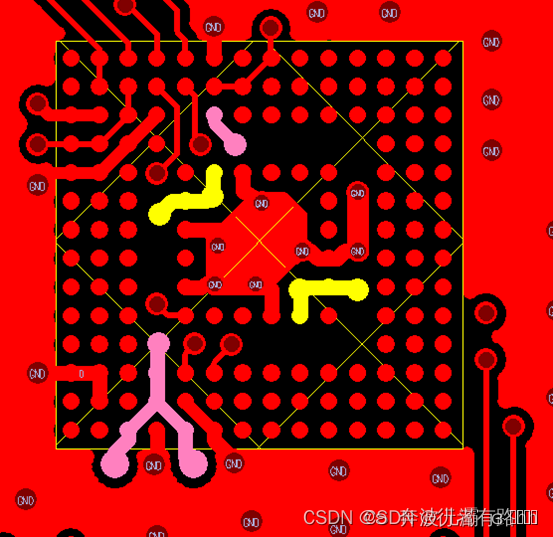

2)ESD器件要靠近TF卡引脚放置,走线需要先经过ESD器件再进入SD卡,不要打孔穿,如下图所示

3)所有的信号线尽量走在同一层,这样有利于信号的一致性,走线与高频信号分开;空间允许的情况下,单根包地,空间紧张的情况下整组包地,所有走线需要有完整的参考平面;

4)SD卡的CLK信号,与其他信号线的间距保证3W以上,有空间的话大于3W。在有空间的情况下,CLK信号单独包地处理,且包地线每隔400mil至少添加一个GND过孔。

5)组内数据线不要相差太大,需要控制400mil以内,走线总长度不要太长尽量控制在12.5 inch(317.5mm)之内,以提高信号稳定性和兼容性。

RK1126的要求是4 inch,即4000mil(101.6mm)。

6)SD卡所有的信号线要做等长处理,以时钟线为目标线,误差控制在300mil以内。

SD卡包括:DATA0、DATA1、DATA2、DATA3、CMD、CLK、DET 7根信号线。

(画板控制在100mil以内。)

只要等长:DATA0、DATA1、DATA2、DATA3、CMD、CLK,6根信号线。

称为SDIO信号。

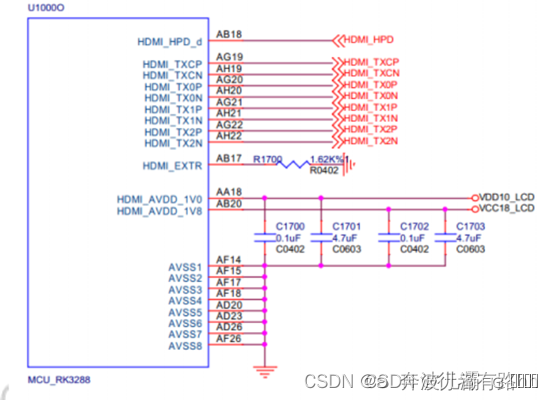

HDMI信号有三对数据信号差分线,一对时钟信号差分线。

HDMI_TXCP、HDMI_TXCN

HDMI_TX0N、HDMI_TX0P

HDMI_TX1N、HDMI_TX1P

HDMI_TX2N、HDMI_TX2P

HDMI的信号走线需严格遵循差分规则要求走线,阻抗要求 Z=100ohm± 10ohm;

线对内两根信号的长度误差控制在10mil以内,

线对与线对之间的长度误差控制在30mil以内;

走线拐角尽量用弧线或者钝角,不能为直角或锐角。

建议在 PCB内层走线,并保证走线参考面是一个连续完整的参考面,不被分割,否则会造成差分线阻抗的不连续性并增加外部噪声对差分线的影响。

如在 PCB表层走线,请注意用地线做包地处理;

在走线中应该尽可能的减少换层过孔,过孔会造成线路阻抗的不连续;最多只能有两个过孔。过孔周围必须伴随有GND孔。且两过孔间距,孔与旁边 shape 间距建议参考下图:

除了4对差分对要有完整的参考GND平面外,SDA、SCL、CEC、HPD信号线也要有完整的参考GND平面。

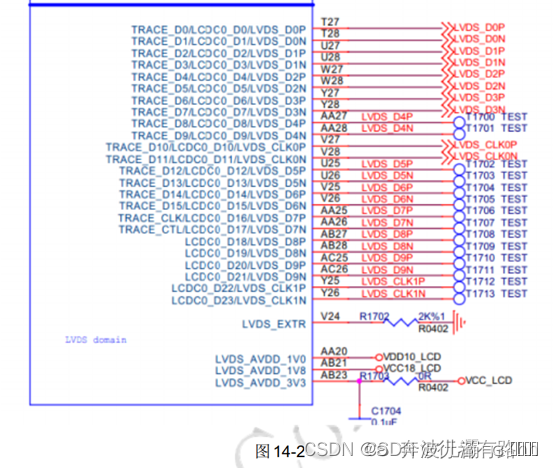

3、LVDS信号线走线要求

LVDS信号有10对数据信号差分对,两对时钟信号差分对。

LVDS_D0P、LVDS_D0N

LVDS_D1P、LVDS_D1N

LVDS_D2P、LVDS_D2N

LVDS_D3P、LVDS_D3N

LVDS_D4P、LVDS_D4N

LVDS_CLK0P、LVDS_CLK0N

LVDS_D5P、LVDS_D5N

LVDS_D6P、LVDS_D6N

LVDS_D7P、LVDS_D7N

LVDS_D8P、LVDS_D8N

LVDS_D9P、LVDS_D9N

LVDS_CLK1P、LVDS_CLK1N

LVDS的信号走线需严格遵循差分规则要求走线,阻抗要求 Z=100ohm± 10ohm;

线对内两根信号的长度误差控制在 30mil以内,

线对与线对之间的长度误差控制在 100mil 以内;

走线拐角尽量用弧线或者钝角,不能为直角或锐角。

4、DVP信号走线要求

常见的CMOS Image Sensor(CIS)接口有DVP和MIPI,本部分主要讲DVP。

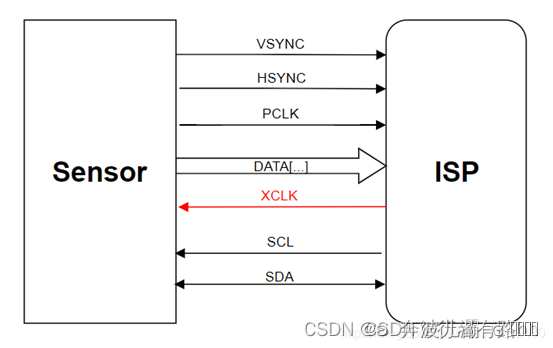

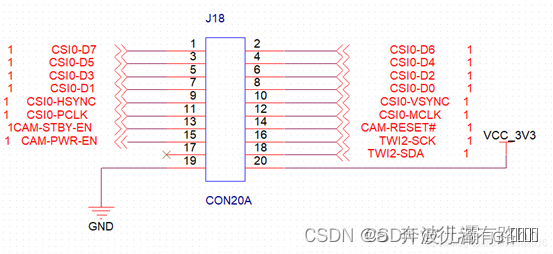

数字视频端口DVP(Digital Video Port) 是传统的sensor输出接口,采用并行输出方式,数据位宽有8bit、10bit、12bit,是CMOS电平信号(非差分信号),最高速率要比串行传输的MIPI接口低,高像素的sensor使用DVP就会比较勉强。PCLK最大速率为96MHz,接口如下图:

DVP是并口传输,速度较慢,传输的带宽低,使用需要以下信号:

PCLK:pixel clock,像素时钟,每个时钟对应一个像素数据,一般为几十MHz;对于时钟信号,一般做包地处理,减少对其他信号的干扰,还需要在源端加电阻和电容,减少过冲和振铃,从而减少对其他信号的干扰。

HSYNC:horizonal synchronization,行同步信号,一般为几十KHz;

VSYNC:vertical synchronization,帧同步信号,一般为几十Hz,与帧率FPS相同;

DATA:像素数据;D[0:11]并口数据(可以是8/10/12bit数据位数大小);

MCLK(XCLK):外部晶振或主控输出给sensor的驱动时钟,典型值是24MHz;

SCL,SDA:用来配置sensor寄存器的IIC接口。

PCLK、HSYNC、VSYNC、DATA[0:11]需要做等长处理。单端阻抗50R,等长200mil,有空间等长100mil。

DVP摄像头电源和MIPI一样。

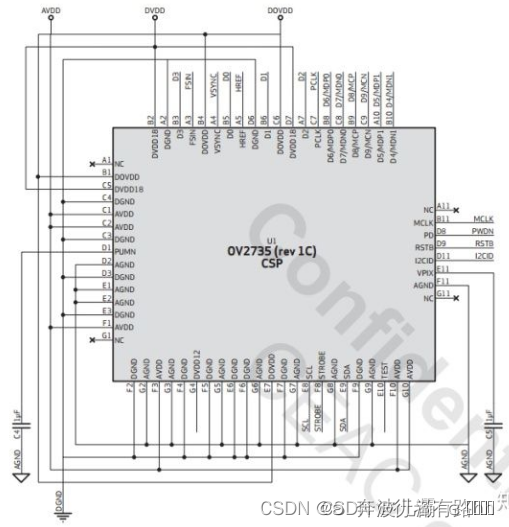

Sensor电源有3个,AVDD(模拟电源)、DOVDD(数字IO电源)、DVDD18(数字内核电源),OV2735的电源如图2所示,并注意上电时序,一般先后上电顺序依次是AVDD、DOVDD、DVDD18,或者至少三者同步上电,而不能是反过来的顺序。

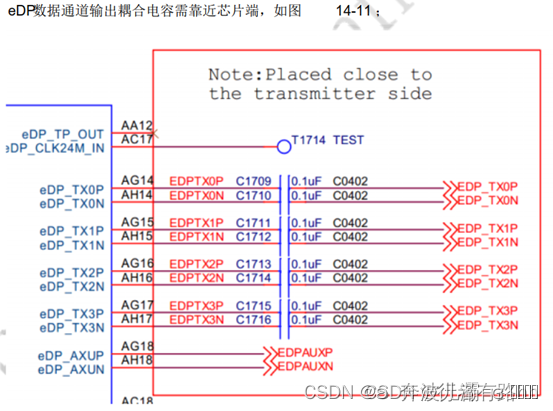

5、eDP信号走线要求

eDP信号有4对数据信号差分线,一对时钟信号差分线。

EDP_TX0P、EDP_TX0N

EDP_TX1P、EDP_TX1N

EDP_TX2P、EDP_TX2N

EDP_TX3P、EDP_TX3N

EDPAUXP、EDPAUXN

eDP的信号走线需严格遵循差分规则要求走线,阻抗要求 Z=100ohm± 10ohm;

线对内两根信号的长度误差控制在10mil以内,

线对与线对之间的长度误差控制在30mil以内;

走线拐角尽量用弧线或者钝角,不能为直角或锐角。

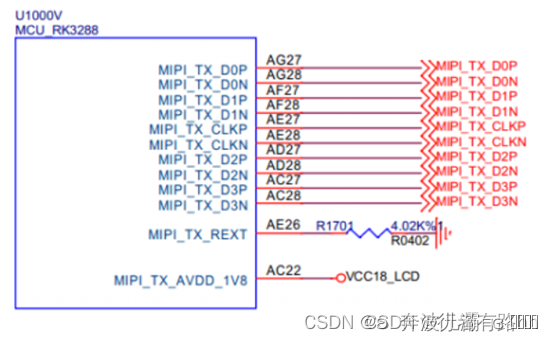

6、MIPI信号线走线要求

MIPI走线的6大法则

(1)等长

MIPI是一种高速差分信号的接口,为了保证信号的同步和一致性,必须保证MIPI DP/DN等长,无论是线对与线对之间(pair to pair)还是单组信号的DP/DN之间,一般需要遵守的长度规则如下:

camera pair to pair 30mil 单组之间:10mil

LCD pair to pair 30mil 单组之间:10mil

(2)等距

在MIPI走线时,一般需要保持DP/DN在走线的过程中保持等距,保证一定的耦合程度,但是需要弄清楚的是,等长的优先级是高于等距的。且在走线时,线对之间要保持3W的距离。

(3)参考层

MIPI走线应该保持连续的参考层,且最好是地层,如果这个条件实在无法满足的话,必须保证参考层的宽度可以达到4W,且为了防止ESD以及干扰等因素,MIPI走线最好走内层。

(4)打孔换层

MIPI尽量少打过孔,且必须注意的是,在打孔换层的时候必须DP/DN同时打孔换层,同时在周围多打地孔,保证信号的回流;

(5)远离干扰

远离RF以及开关电源等干扰源。

6)阻抗要求

MIPI具有阻抗的要求,一般需要达到差分阻抗为100ohm;

注:MIPI在走线时优先级最高的是匹配等长,其余的都可以以实际要求和应用进行灵活处理。

MIPI信号有4对数据信号差分线,一对时钟信号差分线。

MIPI_TX_D0P、MIPI_TX_D0N

MIPI_TX_D1P、MIPI_TX_D1N

MIPI_TX_D2P、MIPI_TX_D2N

MIPI_TX_D3P、MIPI_TX_D3N

MIPI_TX_CLKP、MIPI_TX_CLKN

MIPI的信号走线需严格遵循差分规则要求走线,

阻抗要求 Z=100ohm± 10ohm;

线对内两根信号的长度误差控制在10mil以内,

线对与线对之间的长度误差控制在30mil以内;

走线拐角尽量用弧线或者钝角,不能为直角或锐角。

除了5对差分对要有完整的参考GND以外,SDA、SCL、INT、RESET信号线也要有完整的参考地。

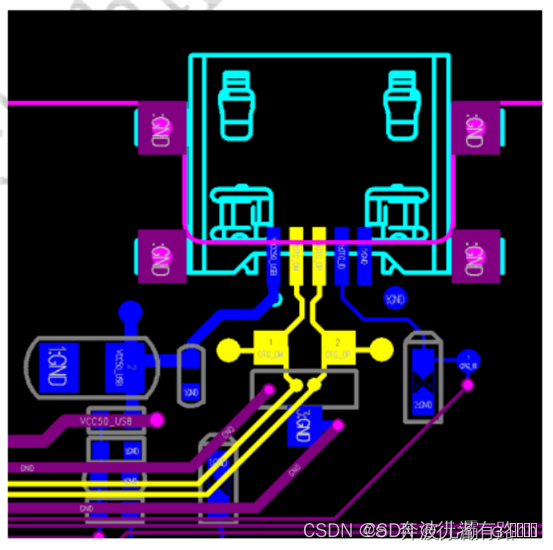

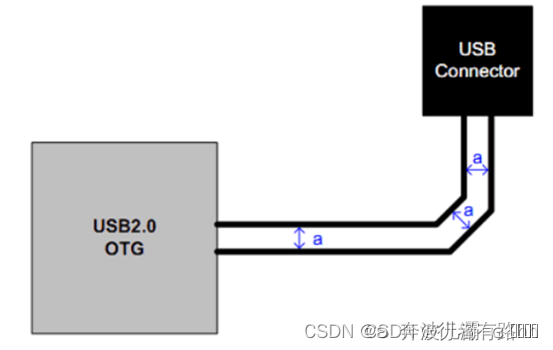

7、USB走线要求

USB2.0规范定义的电流为500mA,但是VBUS走线最好能承受1A的电流,以防过流。如果是在使用USB充电的情况下,VBUS走线需能承受2.5A的电流。

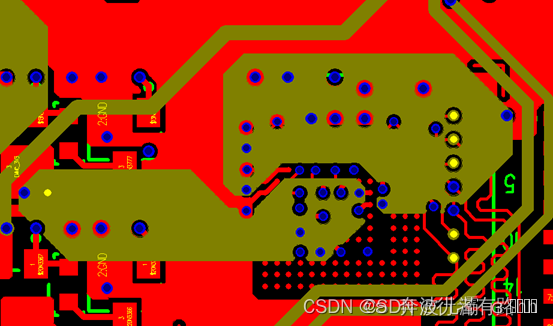

ESD保护器件、共模电感和大电容在布局时应尽可能的靠近USB接口,如下图所示

USB的信号走线必须严格遵循差分规则要求走线。

差分信号组内走线长度偏差控制在±30mil以内,阻抗要求 Z=90± 10ohm。

走线拐角尽量用弧线或者钝角,不能为直角或锐角。

USB差分线过孔数量不超过两个。

USB有打过孔的地方,过孔周围必须伴随有GND孔,以获得更好的信号质量。

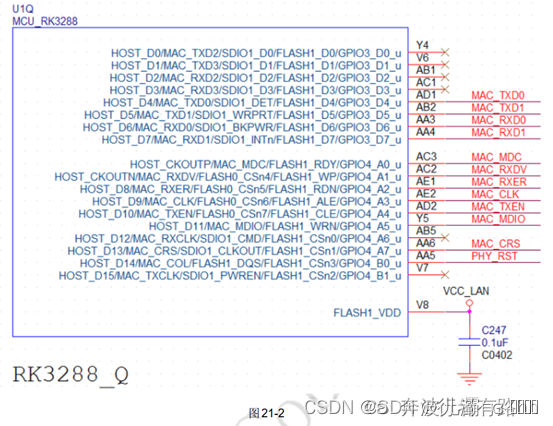

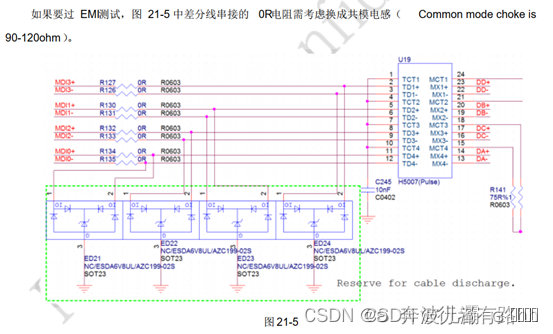

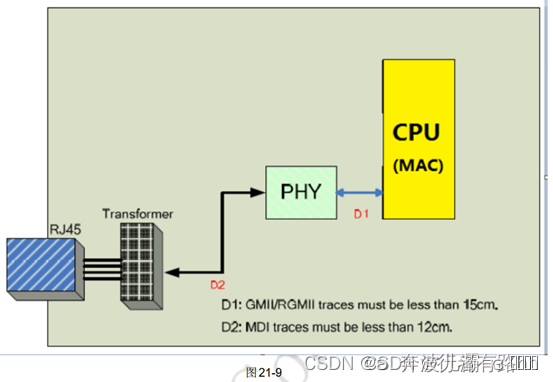

8、MAC走线要求

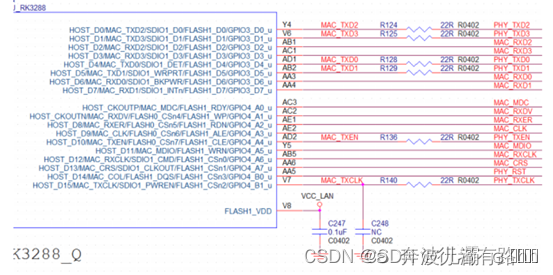

RK3288的MAC支持RMII、RGMII两种接口,图21-1为千兆RGMII,图21-2为百兆RMII接口。

MDI的4对差分线要等长处理;

线对内两根信号长度误差小于 10mil ;

线对与线对之间的长度误差控制在 30mil 以内;

走线拐角尽量用弧线或者钝角,不能为直角或锐角;

阻抗要求Z=100ohm± 10ohm;

走线要尽量短,差分走线总长度要小于 12CM,要有完整的参考面(如果不完整,可能产生最大的 EMI问题),尽量少打换层过孔。

下图串接电阻要靠近 PHY放置,改善 EMI。

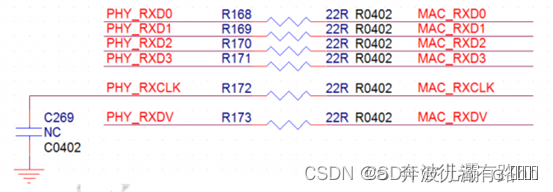

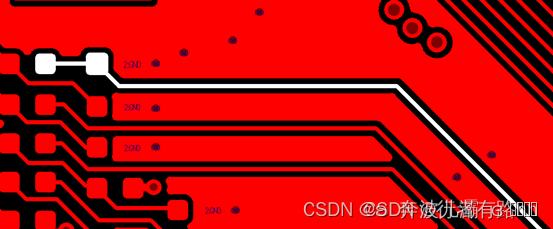

下图中的MAC_RXCLK 必须包地处理。如果没有条件做到包地的话,与其它信号至少要做到3W的间距。

RXD0,RXD1,RXD2,RXD3,RXCLK,RXDV信号间距要满足 3W布线原则;

RXD0,RXD1,RXD2,RXD3,RXCLK,RXDV走线要等长处理,相差小于 100mil,走线要尽量短,整条长度要小于15CM。

走线要有完整的参考面。

下图中的其它信号间距要满足 3W布线原则。

下图串接电阻要靠近 RK3288放置,为改善 EMI。

PHY_TXCLK 必须包地处理。如果没有条件做到包地的话,与其它信号至少要做到3W的间距。

RGMII和其他信号之间的最小间距:推荐RGMII走线宽度的3倍(4W)。至少为RGMII迹线宽度的2倍(3W)。

TXD0,TXD1,TXD2,TXD3,TXCLK,TXEN走线要等长处理,整条相差小于100mil ,走线要尽量短,整条长度要小于 15CM。

走线要有完整的参考面。

其它信号:遵循3W原则即可。

EPHY_RSTN:网口PHY复位信号

EPHY_CLK:网口PHY工作时钟

EPHY_MDCK:MDIO接口时钟输出

EPHY_MDIO:MDIO接口的输入/输出信号

9、BT.1120走线要求

BT.1120协议是一种广泛应用的高清数字视频传输协议,能够把取样结构为4:4:4和4:4:2的视频数据编码成内嵌同步定时基准码的视频数据流进行传输。

并行BT1120接口是16bit位宽(一根时钟线+16根数据线),那么对应的时钟速率是74.25MHz。(如果用的8bit位宽,时钟是148.5MHz)ITU-R BT.1120-9 中已经不再使用并行接口,改成10bit的串行接口。视频像素数据的分量为10bit,复用成单路10bit并行数据流。那么25P的1080P视屏的时钟速率为148.5MHz x 10=1.485GHz。30P的帧率视屏流同样使用1.485G的频率,只是传输的辅助数据更少而已。

单端50Ω阻抗;

组间100mil等长;

相邻走线间距“3W”原则;

保持信号参考平面完整,并避免信号走线穿越电源分割区域。

包括:

VO_DATA0、VO_DATA1、VO_DATA2、VO_DATA3、VO_DATA4、VO_DATA5、VO_DATA6、VO_DATA7、VO_DATA8、VO_DATA9、VO_DATA10、VO_DATA11、VO_DATA12、VO_DATA13、VO_DATA14、VO_DATA15、VO_CLK

共16根数据线和1根时钟线。这17根线需要做等长处理。

10、FLASH(SPI FLASH / NAND FLASH /eMMC)走线要求

避免信号走线穿越电源分割区域,并保持信号参考平面完整;

相邻信号走线间距保持“3W”原则;

等长控制在300mil以内。

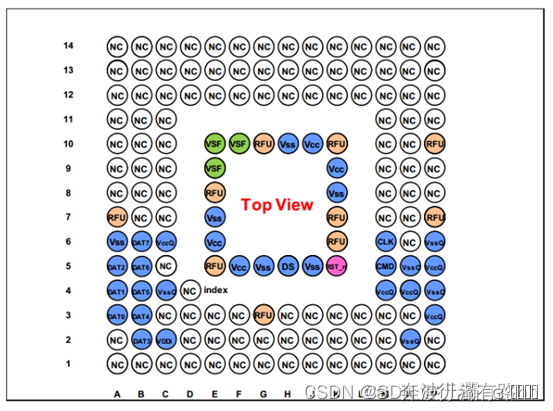

EMMC(Embedded Multi MediaCard):嵌入式多媒体卡,由一个嵌入式存储解决方案组成,带有MMC接口、NANDFlash以及MMC控制器,这些结构都被封装在一个小型BGA中。简单来说,eMMC=NAND Flash +MMC控制芯片+MMC标准接口。

EMMC的总线由11条信号线组成:DATA0、DATA1、DATA2、DATA3、DATA4、DATA5、DATA6、DATA7、CLK、CMD、DS(Data Strobe)数据选通信号线、共11根信号线。

其中CLK、CMD、DATA[0:7]这10根信号线要进行等长。等长控制在100mil。

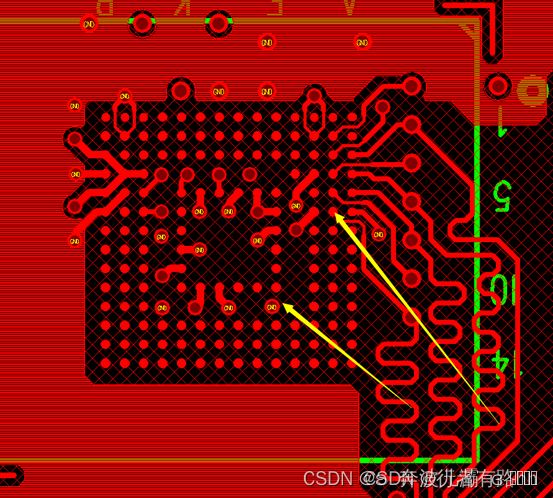

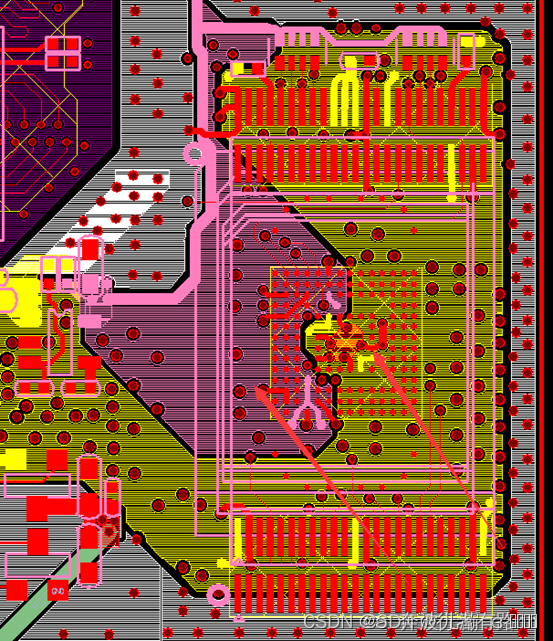

(1)emmc 芯片下方在敷铜时,焊盘部分要增加敷铜禁布框,避免铜皮分布不均影响散热,导致贴片虚焊。

(2)EMMC的两个电源3.3V、1.8V需要进行铺铜。

(3)emmc Flash走线要求整组包地,信号组内任意两根信号线的长度误差控制在100Mil以内,否则会导致高速模式下频率跑不高。(备注:不一定)

(4)走线可采用经过不用的eMMC引脚走线的方式降低对PCB制板间距的要求。

(5)NandFlash与 EMMC Flash可通过双Layout实现物料的切换。

(1)SPI Flash走线要求

SPIFlash由DATA0、DATA1、DATA2、DATA3、CS、CLK 6根信号线组成。

避免信号走线穿越电源分割区域,并保持信号参考平面完整;

SPICS和DATA 的线长以FSPI_CLK的线长为基准,误差控制在300mil以内。

封装+PCB信号长度不超过6inches(152.4mm)。

SPIFlash的速度较慢,一般不用等长。不等长也能满足300mil的要求。

11、PCIE2.0,PCIE3.0走线要求

PCIE2.0:

阻抗要求 Z=85ohm± 10ohm;

线对内两根信号的长度误差控制在 12mil以内;

最大走线长度不超过6000mil(15.24cm);

线对到线对间距≥4倍的线宽;尽可能增加线对之间的间距。

PCIE2.0到其它信号间距建议≥5倍的线宽;至少4倍的PCIE2.0线宽;

最大允许过孔数 ≤ 2 vias;

PCIE3.0:

阻抗要求 Z=85ohm± 10ohm;

线对内两根信号的长度误差控制在 12mil以内;

最大走线长度不超过6000mil(15.24cm);

线对到线对间距建议≥5倍的线宽;尽可能增加线对之间的间距。

PCIE2.0到其它信号间距建议≥5倍的线宽;

最大允许过孔数 ≤ 2 vias

————————————————

版权声明:本文为CSDN博主「行者有路hh」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/bhxc809751502/article/details/128545513

本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有涉嫌抄袭侵权的内容,请联系:hwhale#tublm.com(使用前将#替换为@)