目录

- 前言

- 整体文件结构

- 源码分析(保姆级讲解)

- 中断初始化部分

- 初始化GIC控制器

- 初始化中断向量表

- 设置中断向量表偏移

- 系统时钟初始化部分

- 使能所有的时钟部分

- led初始化部分

- beep初始化部分

- key初始化部分

- 按键中断初始化部分

-

- while循环部分

- 最终编译验证

- 结束语

前言

首先我们在使用开发板开发的过程中难免会碰到使用中断的场景(即判断是哪种中断,并且进入对应的中断服务函数),所以我们接下来开始学习这种机制。

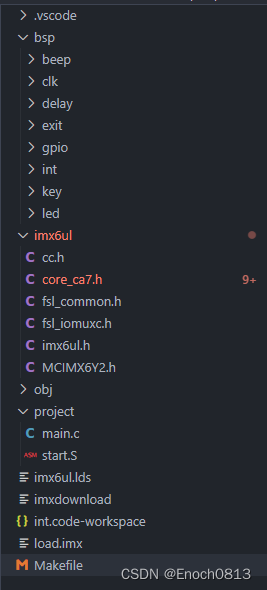

整体文件结构

源码分析(保姆级讲解)

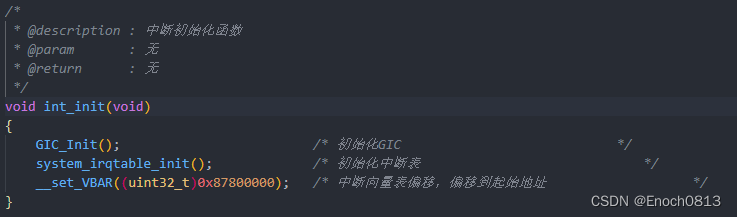

中断初始化部分

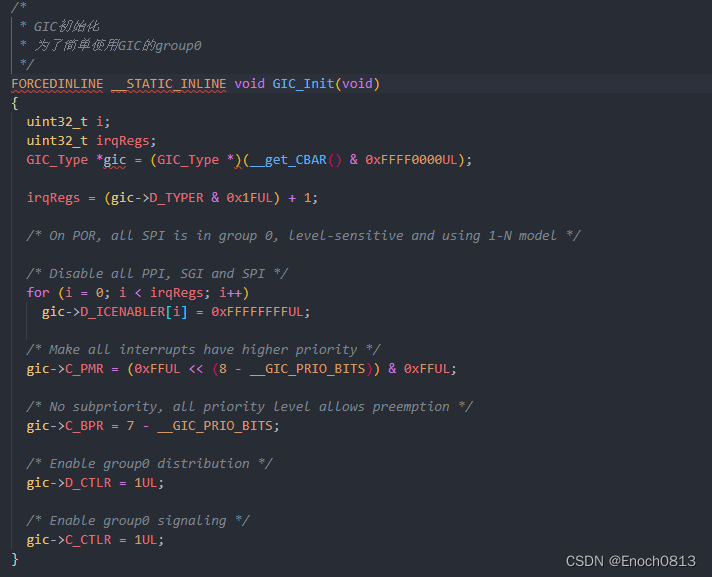

初始化GIC控制器

首先我们使用中断,需要先对中断进行初始化。

GIC_Init();

该函数讲解开始:

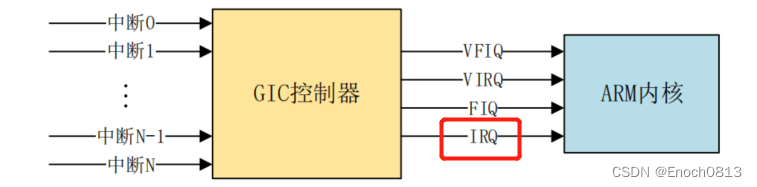

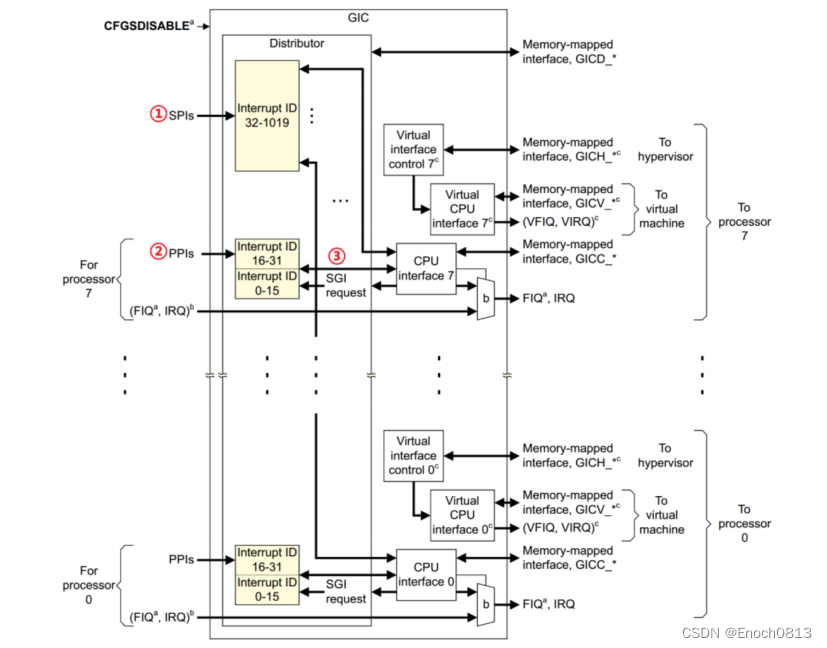

//这个函数主要对GIC进行初始化,那什么是GIC呢?我们在stm32的开发过程中配置中断会使用到NVIC这个中断管理机构,全称叫做 Nested Vectored Interrupt Controller,那么对应的在I.MX6U中的中断管理机构叫做GIC,全称是 general interrupt controller。当 GIC 接收到外部中断信号以后就会报给 ARM 内核,但是ARM 内核只提供了四个信号给 GIC 来汇报中断情况:VFIQ、VIRQ、FIQ 和 IRQ,如下图所示:

在这四个中断中,我们只会使用到一个中断即上图中的IRQ中断(外部中断)。

接下来我们就看看是如何对GIC这个中断管理机构进行配置的?

好!按照老样子,接下来开始详细讲解每行代码的用处,以及为什么这样写!

GIC_Type *gic = (GIC_Type *)(__get_CBAR() & 0xFFFF0000UL);

//结构体 GIC_Type 就是 GIC 控制器,列举出了 GIC 控制器的所有寄存器,可以通过结构体 GIC_Type 来访问 GIC 的所有寄存器。

其中GIC_Type结构体如下所示:

typedef struct

{

uint32_t RESERVED0[1024];

__IOM uint32_t D_CTLR;

__IM uint32_t D_TYPER;

__IM uint32_t D_IIDR;

uint32_t RESERVED1[29];

__IOM uint32_t D_IGROUPR[16];

uint32_t RESERVED2[16];

__IOM uint32_t D_ISENABLER[16];

uint32_t RESERVED3[16];

__IOM uint32_t D_ICENABLER[16];

uint32_t RESERVED4[16];

__IOM uint32_t D_ISPENDR[16];

uint32_t RESERVED5[16];

__IOM uint32_t D_ICPENDR[16];

uint32_t RESERVED6[16];

__IOM uint32_t D_ISACTIVER[16];

uint32_t RESERVED7[16];

__IOM uint32_t D_ICACTIVER[16];

uint32_t RESERVED8[16];

__IOM uint8_t D_IPRIORITYR[512];

uint32_t RESERVED9[128];

__IOM uint8_t D_ITARGETSR[512];

uint32_t RESERVED10[128];

__IOM uint32_t D_ICFGR[32];

uint32_t RESERVED11[32];

__IM uint32_t D_PPISR;

__IM uint32_t D_SPISR[15];

uint32_t RESERVED12[112];

__OM uint32_t D_SGIR;

uint32_t RESERVED13[3];

__IOM uint8_t D_CPENDSGIR[16];

__IOM uint8_t D_SPENDSGIR[16];

uint32_t RESERVED14[40];

__IM uint32_t D_PIDR4;

__IM uint32_t D_PIDR5;

__IM uint32_t D_PIDR6;

__IM uint32_t D_PIDR7;

__IM uint32_t D_PIDR0;

__IM uint32_t D_PIDR1;

__IM uint32_t D_PIDR2;

__IM uint32_t D_PIDR3;

__IM uint32_t D_CIDR0;

__IM uint32_t D_CIDR1;

__IM uint32_t D_CIDR2;

__IM uint32_t D_CIDR3;

__IOM uint32_t C_CTLR;

__IOM uint32_t C_PMR;

__IOM uint32_t C_BPR;

__IM uint32_t C_IAR;

__OM uint32_t C_EOIR;

__IM uint32_t C_RPR;

__IM uint32_t C_HPPIR;

__IOM uint32_t C_ABPR;

__IM uint32_t C_AIAR;

__OM uint32_t C_AEOIR;

__IM uint32_t C_AHPPIR;

uint32_t RESERVED15[41];

__IOM uint32_t C_APR0;

uint32_t RESERVED16[3];

__IOM uint32_t C_NSAPR0;

uint32_t RESERVED17[6];

__IM uint32_t C_IIDR;

uint32_t RESERVED18[960];

__OM uint32_t C_DIR;

} GIC_Type;

从上述代码中可知,该GIC寄存器中分为两部分,分别是分发器端和CPU接口端。比如我们想要访问C_CTLR该寄存器,相对于GIC基地址的偏移为0x2000,同样的,获取到GIC基地址之后只需要加上0x2000即可访问GIC的CPU接口段寄存器。那么问题来了,GIC控制器的寄存器基地址在哪里,这里我们就需要用到 Cortex-A 的 CP15 协处理器了。那什么是CP15协处理器?

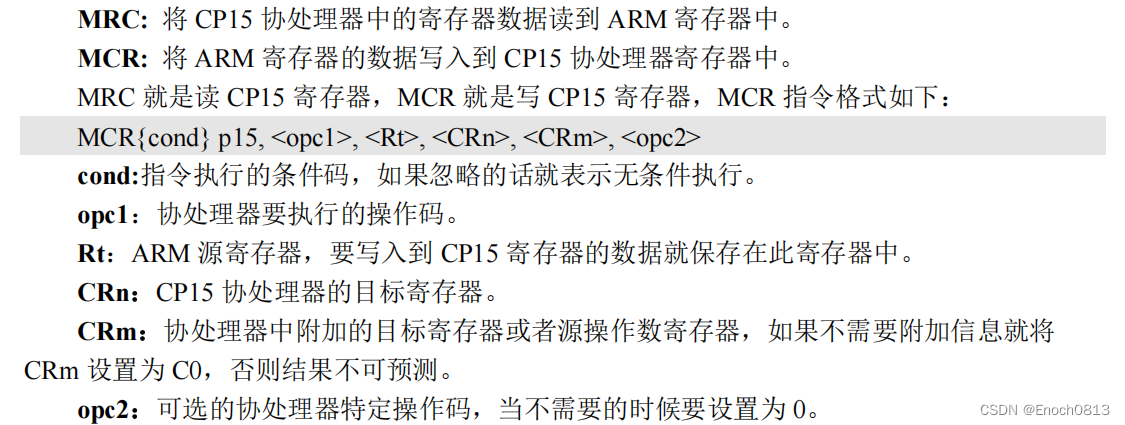

CP15 协处理器一般用于存储系统管理,但是在中断中也会使用到,CP15 协处理器一共有16 个 32 位寄存器。CP15 协处理器的访问通过如下另个指令完成

CP15协处理器有16个32位寄存器,c0~c15,由于我们在本例中使用到GPIO中断,所以我们暂时先看c0、c1、c12 和 c15 这四个寄

存器。具体怎么使用会结合着代码进行讲解。

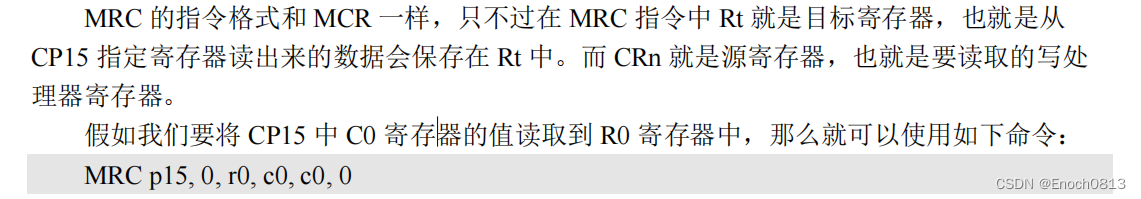

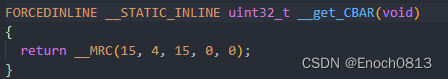

进入__get_CBAR()这个函数中:

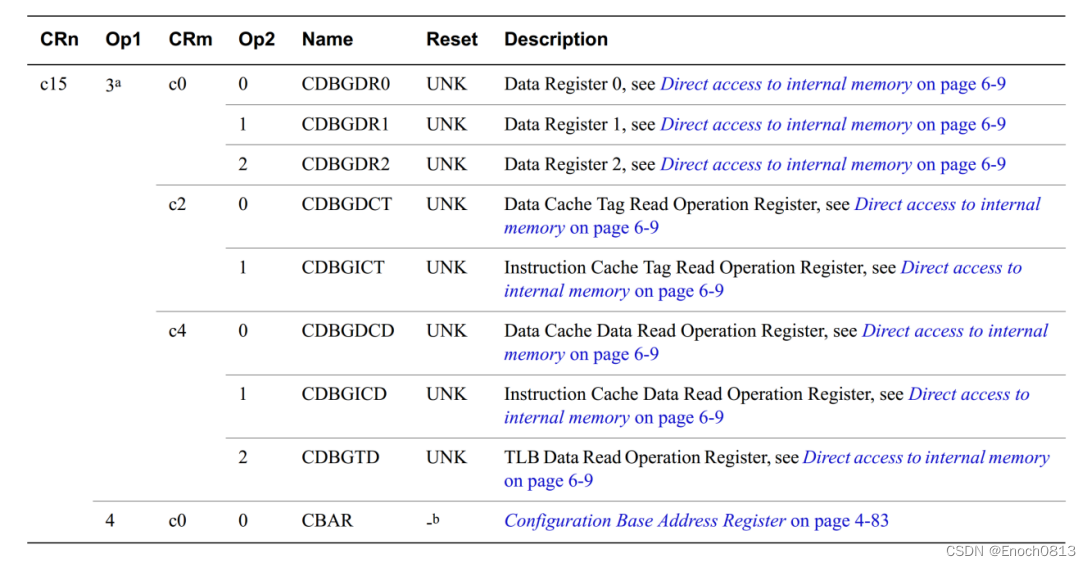

这个函数的作用为获取GIC的基地址,我们使用到c15这个寄存器,具体含义如下:

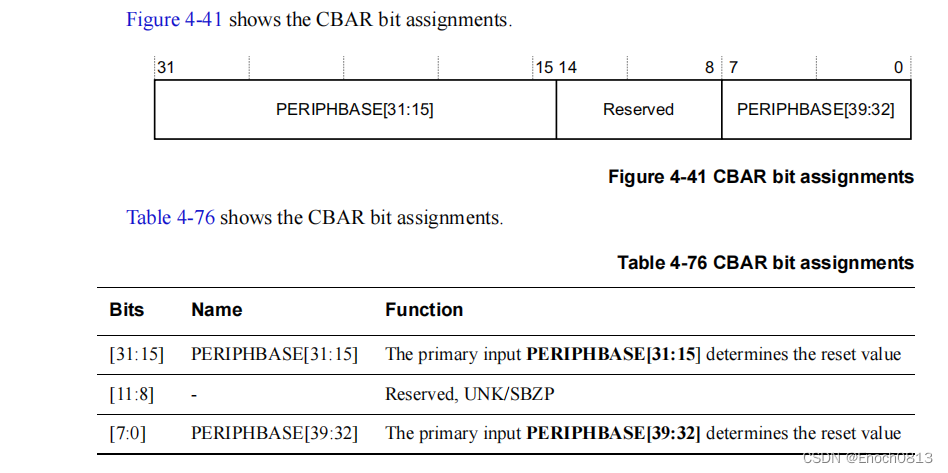

由上图可知,当

由上图可知,当op1 = 4 ,crm = c0,op2 = 0时,代表此c15寄存器为CBAR寄存器。

#define __MRC(coproc, opcode_1, CRn, CRm, opcode_2) \

({ \

uint32_t __dst; \

__ASM volatile ("MRC " __STRINGIFY(p##coproc) ", " __STRINGIFY(opcode_1) ", " \

"%0, " __STRINGIFY(c##CRn) ", " __STRINGIFY(c##CRm) ", " \

__STRINGIFY(opcode_2) \

: "=r" (__dst) ); \

__dst; \

})

CBAR寄存器如下图所示:

从上图可知,通过MRC设置c15为CBAR寄存器后,需要获取该寄存器的高16位,所以在代码中需要和0xFFFF0000UL进行“与”操作。

获取到GIC基地址后,使用gic指针指向该基地址。并且该指针的类型为GIC_Type。

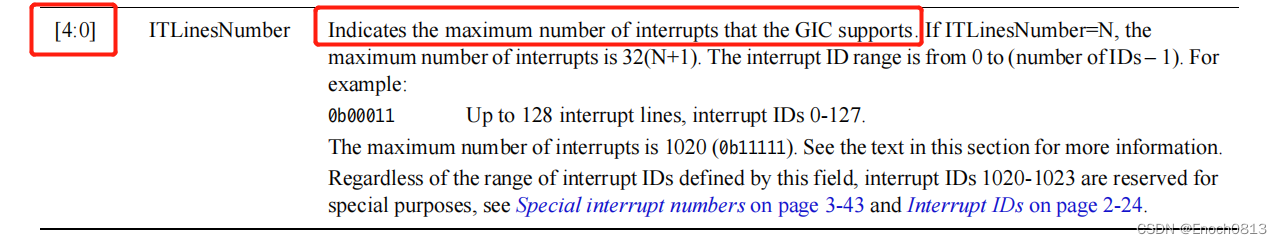

irqRegs = (gic->D_TYPER & 0x1FUL) + 1;

其中(gic->D_TYPER & 0x1FUL) 用来获取其中断数量,即获取该寄存器的低5位。具体寄存器如下:

加

加1是因为比如我们实际获取的中断数是128个,但是由于是从0开始计数,所以实际输出值为127,所以我们需要加1。

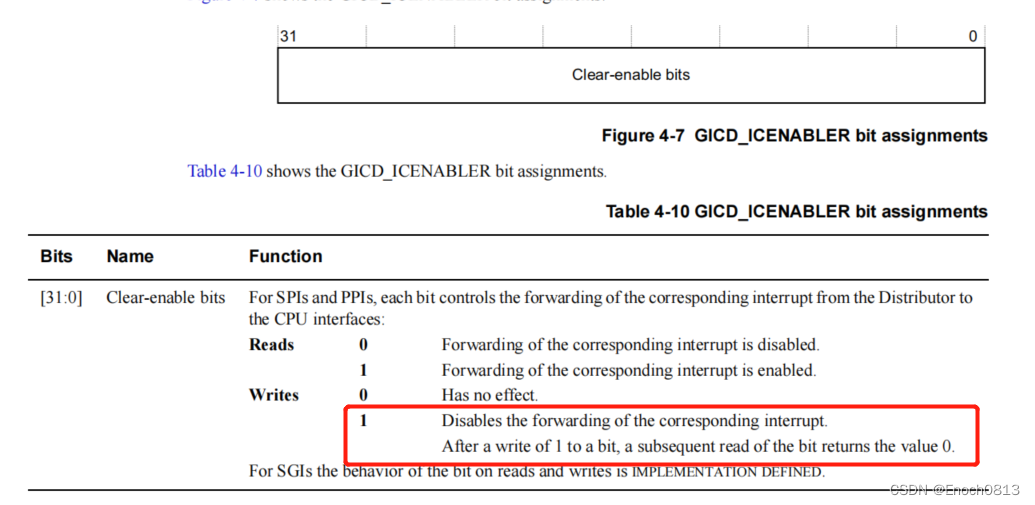

for (i = 0; i < irqRegs; i++)

gic->D_ICENABLER[i] = 0xFFFFFFFFUL;

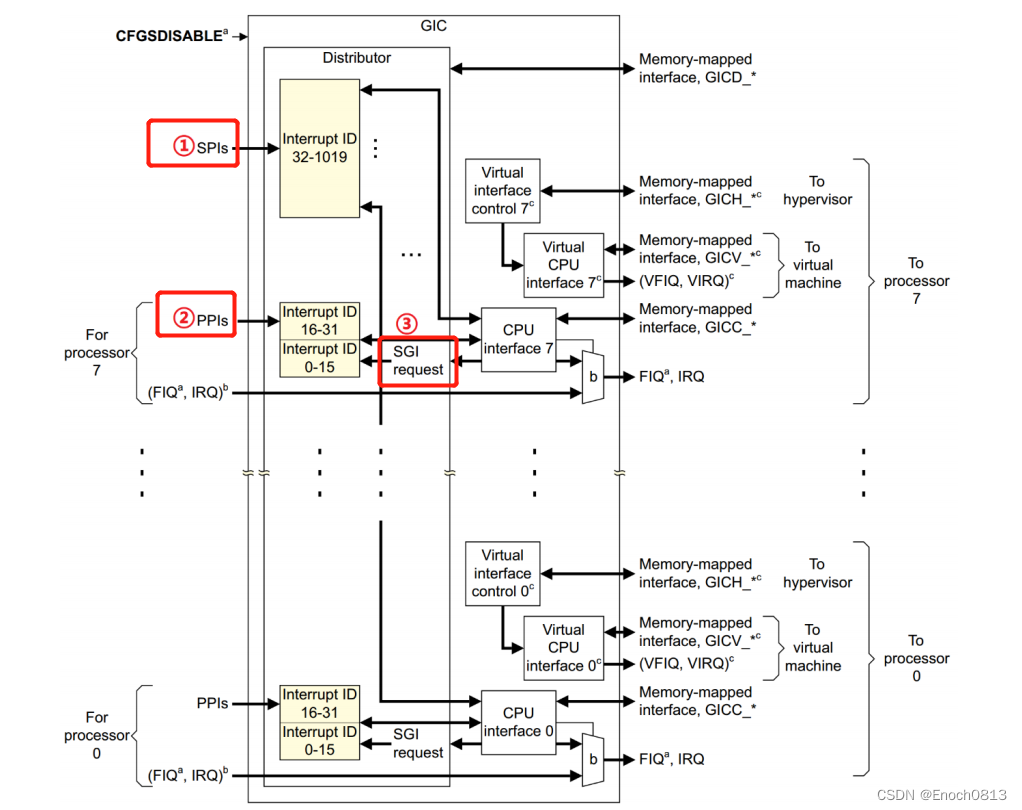

//我们家来需要看看实际情况的内部GIC控制器是什么样子的?

上图中的左侧部分是中断源,中间部分是

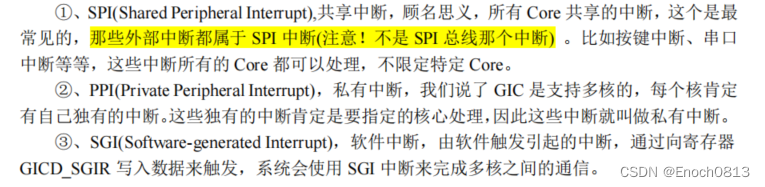

上图中的左侧部分是中断源,中间部分是GIC控制器,最右侧就是中断控制器向处理器内核发送中断信息。其中GIC将众多的中断源分为三类,并且已经在上图中用红框标出。

所以上述代码就是在对所有的PPI,SGI和SPI这三种中断源进行不使能操作。并且该寄存器如下图所示:

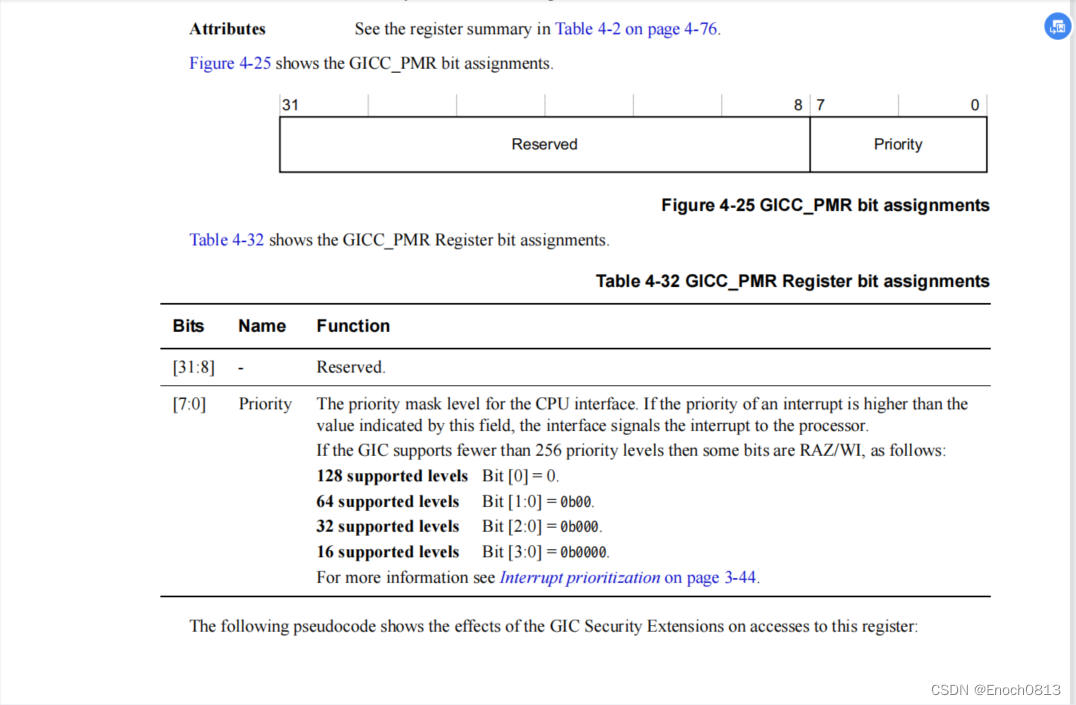

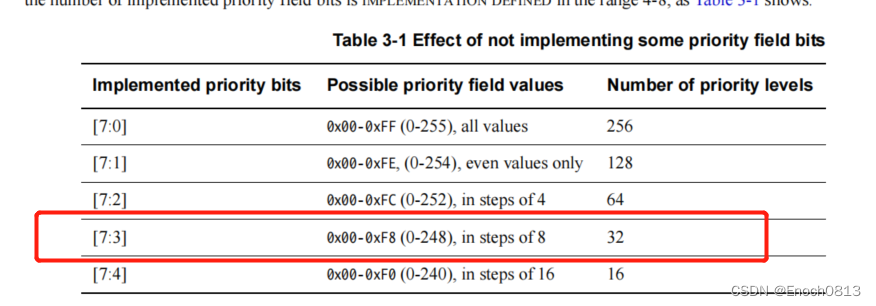

gic->C_PMR = (0xFFUL << (8 - __GIC_PRIO_BITS)) & 0xFFUL;

//其中

所以上述代码相当于

gic->C_PMR = (0xFFUL << 3) & 0xFFUL;

相当于

gic->C_PMR = 0xF8;

其中C_PWR寄存器具体配置如下图所示:

所以由上图可知,将优先级等级设置为32。

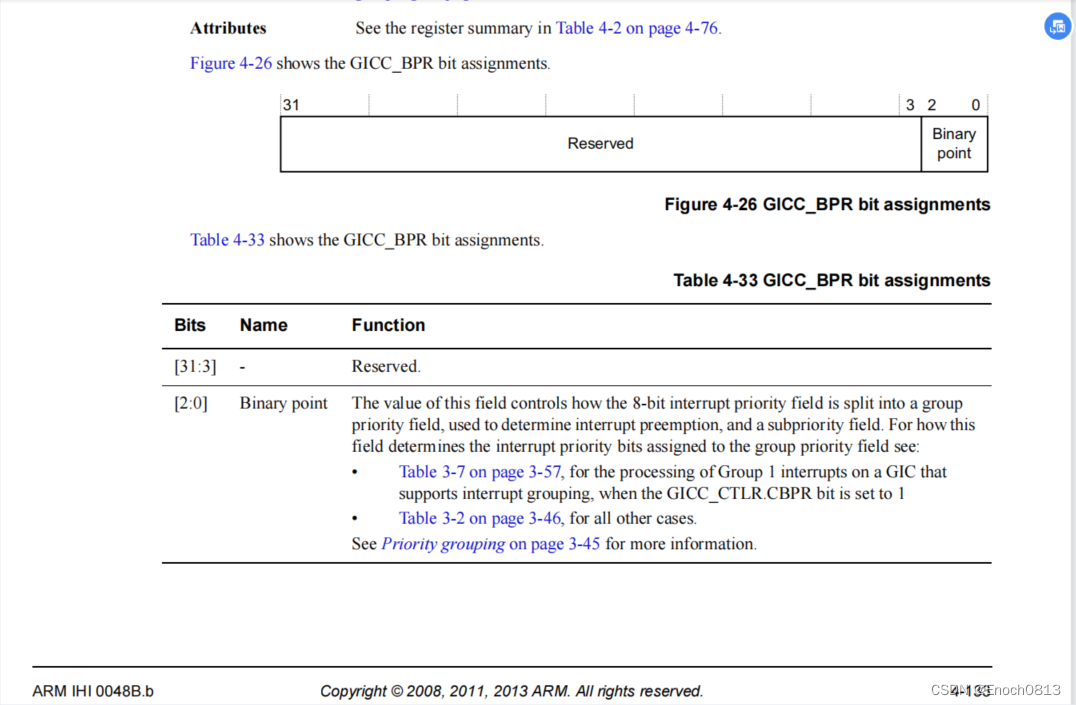

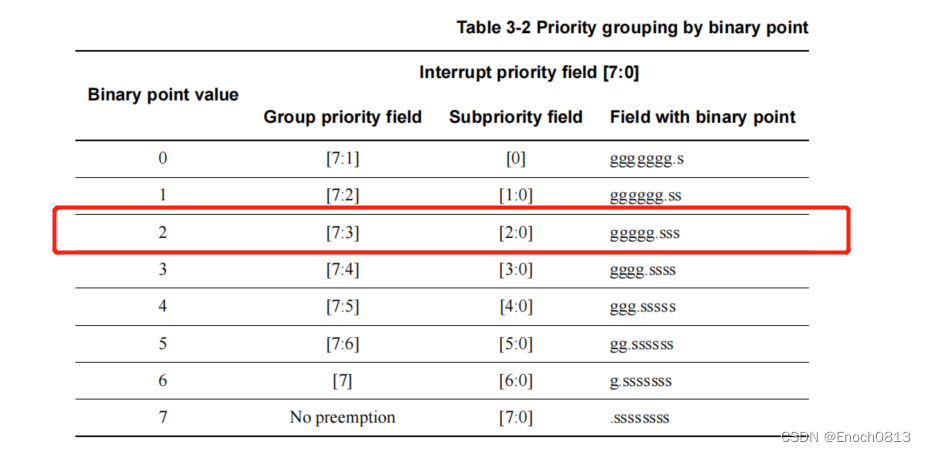

gic->C_BPR = 7 - __GIC_PRIO_BITS;

上述代码相当于

gic->C_BPR = 2;

并且该寄存器如下图所示:

即设置没有子优先级,所有优先级级别都允许抢占。

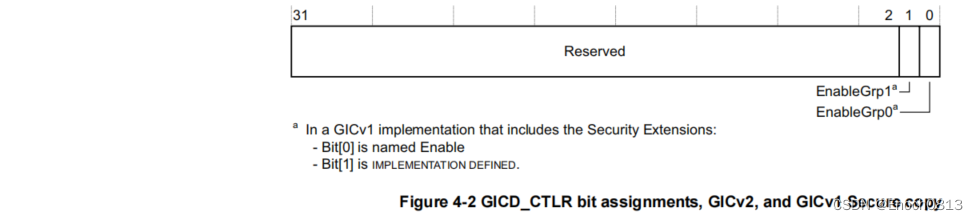

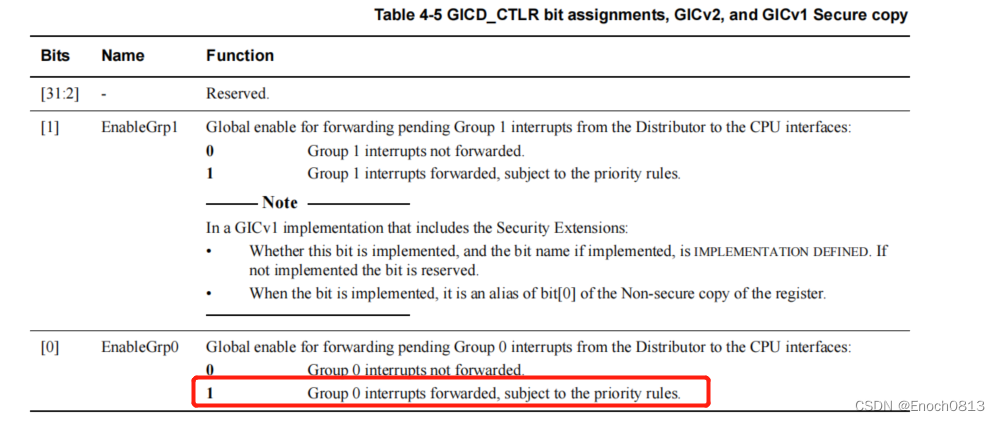

gic->D_CTLR = 1UL;

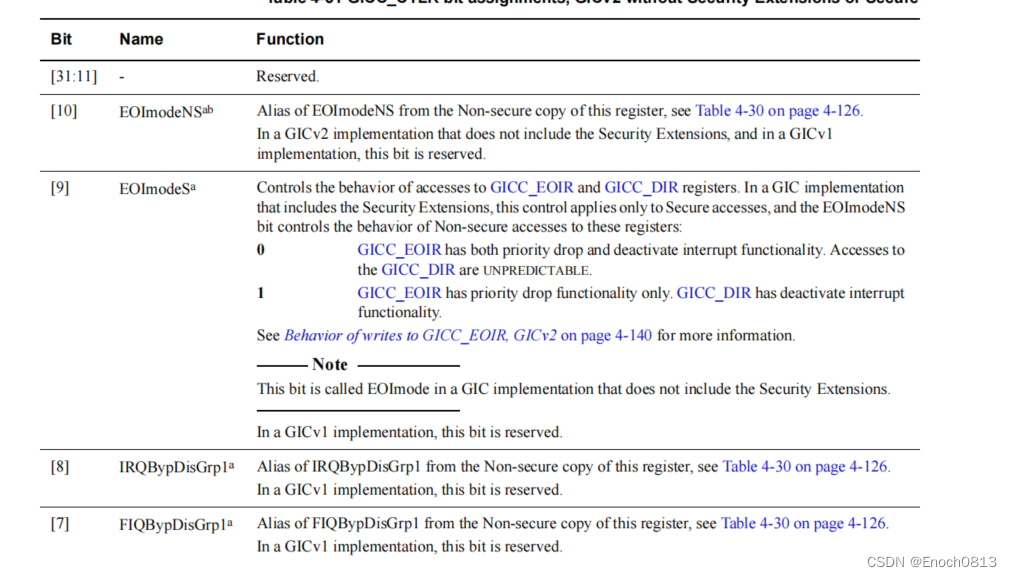

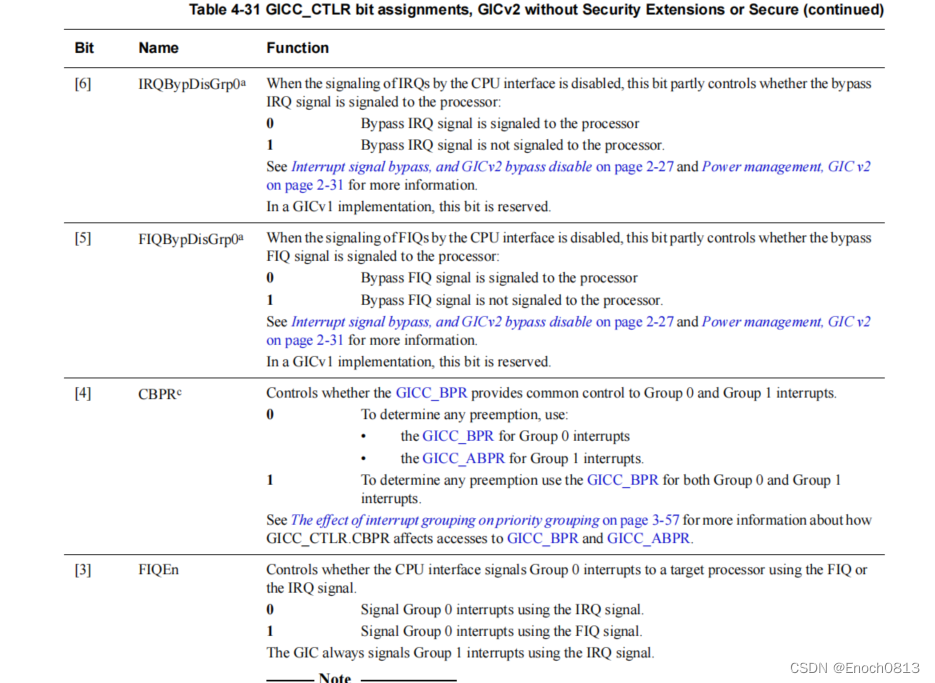

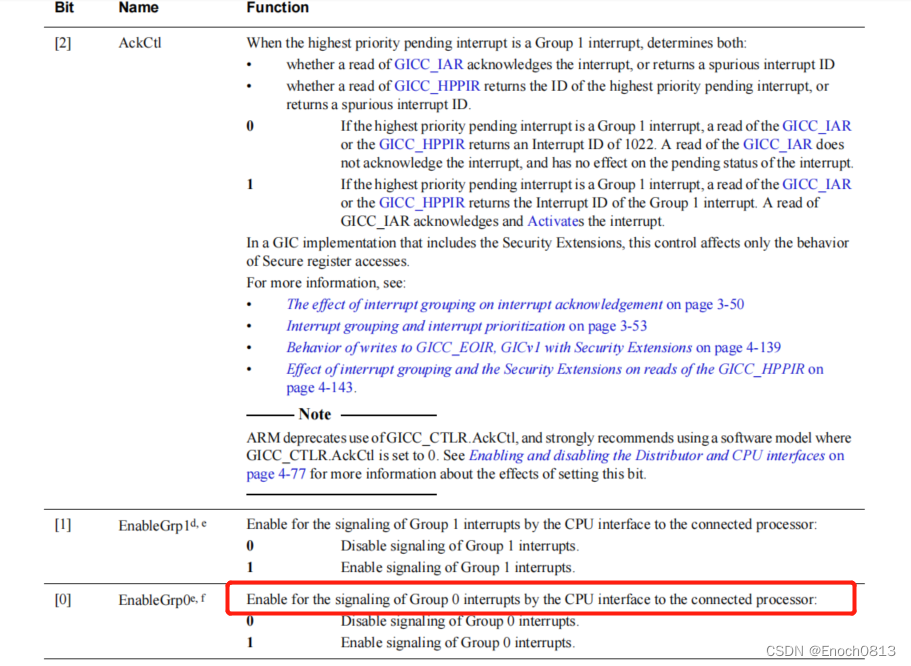

其中该寄存器具体配置如下所示:

启用group0分发器。

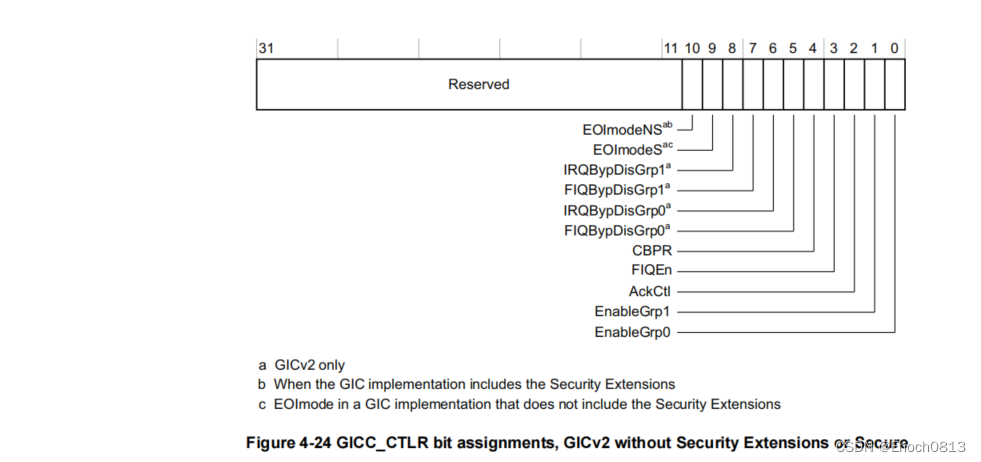

gic->C_CTLR = 1UL;

其中该寄存器具体配置如下所示:

启用group0接口端。

至此GIC_Init函数讲解完毕

初始化中断向量表

system_irqtable_init();

该函数讲解开始:

void system_irqtable_init(void)

{

unsigned int i = 0;

irqNesting = 0;

for(i = 0; i < NUMBER_OF_INT_VECTORS; i++)

{

system_register_irqhandler((IRQn_Type)i,default_irqhandler, NULL);

}

}

好!按照老样子,接下来开始详细讲解每行代码的用处,以及为什么这样写!

#define NUMBER_OF_INT_VECTORS 160

//这里为什么是160呢?

由上图GIC控制器可知,需要去处理很多中断源,为了区分这些不同的中断源肯定要给他们分配一个唯一 ID,这些 ID 就是中断 ID。每一个cpu最多支持1020个中断ID。中断 ID 号为 ID0~ID1019。这 1020 个 ID 包含了 PPI、SPI 和 SGI,那么这三类中断是如何分配这 1020 个中断 ID 的呢?这 1020 个 ID 分配如下:

ID0~ID15:这 16 个 ID 分配给 SGI。

ID16~ID31:这 16 个 ID 分配给 PPI。

ID32~ID1019:这 988 个 ID 分配给 SPI,像 GPIO 中断、串口中断等这些外部中断。

至于具体到某个 ID 对应哪个中断那就由半导体厂商根据实际情况去定义了。比如 I.MX6U 的总共使用了 128 个中断 ID,加上前面属于 PPI 和 SGI 的 32 个 ID,I.MX6U 的中断源共有 128+32=160个,所以设置为160个。

system_register_irqhandler((IRQn_Type)i,default_irqhandler, NULL);

void system_register_irqhandler(IRQn_Type irq, system_irq_handler_t handler, void *userParam)

{

irqTable[irq].irqHandler = handler;

irqTable[irq].userParam = userParam;

}

所以就需要针对每一个中断源进行配置。

该函数的参数主要有三个,分别是IRQn_Type irq,system_irq_handler_t handler和void *userParam。

IRQn_Type irq:其中IRQn_Type是关于160个中断源的结构体。irq是要注册的中断号。

system_irq_handler_t handler:其中system_irq_handler_t是一个中断服务函数形式。

void *userParam:中断服务处理函数参数

irqTable[irq].irqHandler = handler;

传入该函数的hander等于default_irqhandler

void default_irqhandler(unsigned int giccIar, void *userParam)

{

while(1)

{

}

}

由于只是初始化部分,所以该中断服务函数里面什么也不做。

irqTable[irq].userParam = userParam;

传入该函数的参数userParam等于NULL。

至此system_irqtable_init();函数讲解完毕

设置中断向量表偏移

__set_VBAR((uint32_t)0x87800000);

该函数讲解开始:

设置中断向量表的偏移,时期偏移到起始地址,即0x87800000,即程序起始运行地址。

系统时钟初始化部分

void imx6u_clkinit(void)

{

unsigned int reg = 0;

/* 1、设置ARM内核时钟为792MHz */

/* 1.1、判断当前ARM内核是使用的那个时钟源启动的,正常情况下ARM内核是由pll1_sw_clk驱动的,而

* pll1_sw_clk有两个来源:pll1_main_clk和tep_clk。

* 如果我们要让ARM内核跑到792M的话那必须选择pll1_main_clk作为pll1的时钟源。

* 如果我们要修改pll1_main_clk时钟的话就必须先将pll1_sw_clk从pll1_main_clk切换到step_clk,

* 当修改完pll1_main_clk以后在将pll1_sw_clk切换回pll1_main_clk。而step_clk的时钟源可以选择

* 板子上的24MHz晶振。

*/

if((((CCM->CCSR) >> 2) & 0x1 ) == 0) /* 当前pll1_sw_clk使用的pll1_main_clk*/

{

CCM->CCSR &= ~(1 << 8); /* 配置step_clk时钟源为24MH OSC */

CCM->CCSR |= (1 << 2); /* 配置pll1_sw_clk时钟源为step_clk */

}

/* 1.2、设置pll1_main_clk为792MHz

* 因为pll1_sw_clk进ARM内核的时候会被二分频!

* 配置CCM_ANLOG->PLL_ARM寄存器

* bit13: 1 使能时钟输出

* bit[6:0]: 66, 由公式:Fout = Fin * div_select / 2.0,792=24*div_select/2.0,

* 得出:div_select= 66

*/

CCM_ANALOG->PLL_ARM = (1 << 13) | ((66 << 0) & 0X7F); /* 配置pll1_main_clk=792MHz */

CCM->CCSR &= ~(1 << 2); /* 将pll_sw_clk时钟重新切换回pll1_main_clk */

CCM->CACRR = 0; /* ARM内核时钟为pll1_sw_clk/1=792/1=792Mhz */

/* 2、设置PLL2(SYS PLL)各个PFD */

reg = CCM_ANALOG->PFD_528;

reg &= ~(0X3F3F3F3F); /* 清除原来的设置 */

reg |= 32<<24; /* PLL2_PFD3=528*18/32=297Mhz */

reg |= 24<<16; /* PLL2_PFD2=528*18/24=396Mhz(DDR使用的时钟,最大400Mhz) */

reg |= 16<<8; /* PLL2_PFD1=528*18/16=594Mhz */

reg |= 27<<0; /* PLL2_PFD0=528*18/27=352Mhz */

CCM_ANALOG->PFD_528=reg; /* 设置PLL2_PFD0~3 */

/* 3、设置PLL3(USB1)各个PFD */

reg = 0; /* 清零 */

reg = CCM_ANALOG->PFD_480;

reg &= ~(0X3F3F3F3F); /* 清除原来的设置 */

reg |= 19<<24; /* PLL3_PFD3=480*18/19=454.74Mhz */

reg |= 17<<16; /* PLL3_PFD2=480*18/17=508.24Mhz */

reg |= 16<<8; /* PLL3_PFD1=480*18/16=540Mhz */

reg |= 12<<0; /* PLL3_PFD0=480*18/12=720Mhz */

CCM_ANALOG->PFD_480=reg; /* 设置PLL3_PFD0~3 */

/* 4、设置AHB时钟 最小6Mhz, 最大132Mhz (boot rom自动设置好了可以不用设置)*/

CCM->CBCMR &= ~(3 << 18); /* 清除设置*/

CCM->CBCMR |= (1 << 18); /* pre_periph_clk=PLL2_PFD2=396MHz */

CCM->CBCDR &= ~(1 << 25); /* periph_clk=pre_periph_clk=396MHz */

while(CCM->CDHIPR & (1 << 5));/* 等待握手完成 */

/* 修改AHB_PODF位的时候需要先禁止AHB_CLK_ROOT的输出,但是

* 我没有找到关闭AHB_CLK_ROOT输出的的寄存器,所以就没法设置。

* 下面设置AHB_PODF的代码仅供学习参考不能直接拿来使用!!

* 内部boot rom将AHB_PODF设置为了3分频,即使我们不设置AHB_PODF,

* AHB_ROOT_CLK也依旧等于396/3=132Mhz。

*/

#if 0

/* 要先关闭AHB_ROOT_CLK输出,否则时钟设置会出错 */

CCM->CBCDR &= ~(7 << 10); /* CBCDR的AHB_PODF清零 */

CCM->CBCDR |= 2 << 10; /* AHB_PODF 3分频,AHB_CLK_ROOT=132MHz */

while(CCM->CDHIPR & (1 << 1));/

* 等待握手完成 */

#endif

/* 5、设置IPG_CLK_ROOT最小3Mhz,最大66Mhz (boot rom自动设置好了可以不用设置)*/

CCM->CBCDR &= ~(3 << 8); /* CBCDR的IPG_PODF清零 */

CCM->CBCDR |= 1 << 8; /* IPG_PODF 2分频,IPG_CLK_ROOT=66MHz */

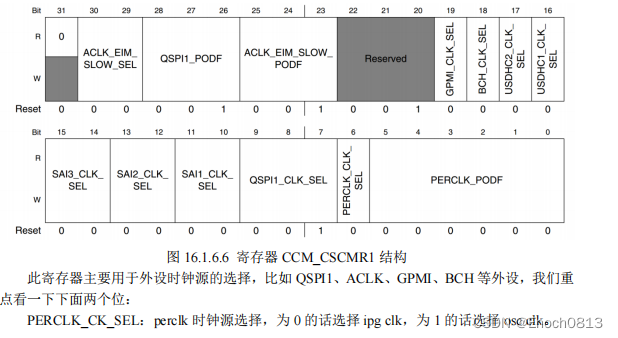

/* 6、设置PERCLK_CLK_ROOT时钟 */

CCM->CSCMR1 &= ~(1 << 6); /* PERCLK_CLK_ROOT时钟源为IPG */

CCM->CSCMR1 &= ~(7 << 0); /* PERCLK_PODF位清零,即1分频 */

}

好!按照老样子,接下来开始详细讲解每行代码的用处,以及为什么这样写!

unsigned int reg = 0;

//声明一个无整型变量reg,并且赋值为0。

if((((CCM->CCSR) >> 2) & 0x1 ) == 0) /* 当前pll1_sw_clk使用的pll1_main_clk*/

{

CCM->CCSR &= ~(1 << 8); /* 配置step_clk时钟源为24MH OSC */

CCM->CCSR |= (1 << 2); /* 配置pll1_sw_clk时钟源为step_clk */

}

CCM_ANALOG->PLL_ARM = (1 << 13) | ((66 << 0) & 0X7F); /* 配置pll1_main_clk=792MHz */

CCM->CCSR &= ~(1 << 2); /* 将pll_sw_clk时钟重新切换回pll1_main_clk */

CCM->CACRR = 0; /* ARM内核时钟为pll1_sw_clk/1=792/1=792Mhz */

//这一部分主要是设置ARM内核时钟的,那么ARM内核时钟是由什么来决定的呢?

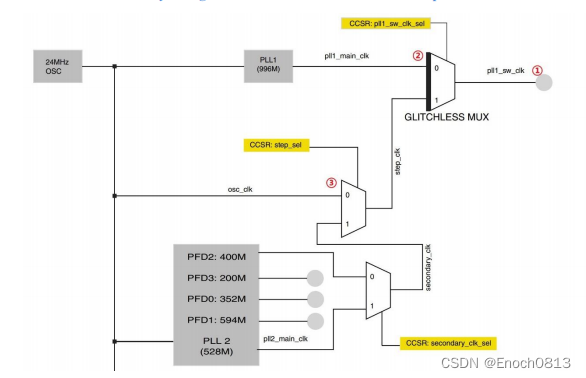

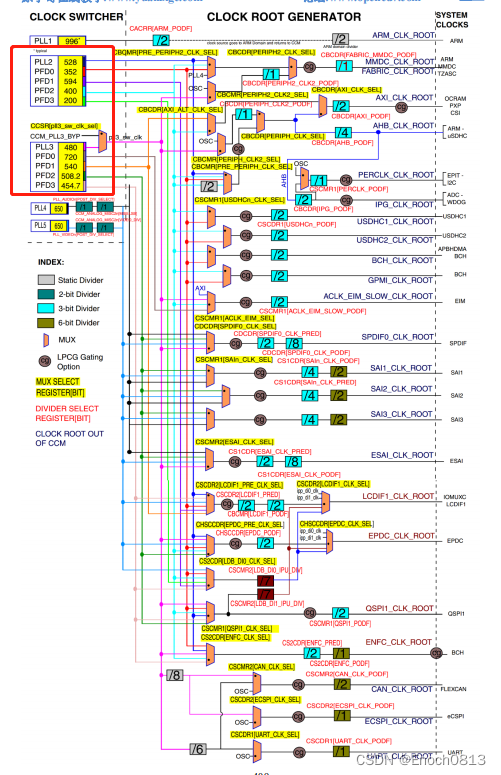

由上图可知,其内核时钟源来自于PLL1,此时PLL1为996MHz,然后经过分频操作后,最终就会配置到ARM上。

在本例中设置ARM内核时钟为792MHz,所以我们肯定要更改PLL1时钟频率,那么在修改之前,我们需要先将内核时钟源改为其他的时钟源,那么我们看一下可修改的时钟源有哪些?

①、pll1_sw_clk 也就是 PLL1 的最终输出频率。

②、此处是一个选择器,选择 pll1_sw_clk 的时钟源,由寄存器 CCM_CCSR 的PLL1_SW_CLK_SEL 位决定 pll1_sw_clk 是选择 pll1_main_clk 还是 step_clk。正常情况下应该选择 pll1_main_clk,但是如果要对 pll1_main_clk(PLL1)的频率进行调整的话,比如我们要设置

PLL1=1056MHz,此时就要先将 pll1_sw_clk 切换到 step_clk 上。等 pll1_main_clk 调整完成以后再切换回来。

③、此处也是一个选择器,选择 step_clk 的时钟源,由寄存器 CCM_CCSR 的 STEP_SEL 位来决定 step_clk 是选择 osc_clk 还是 secondary_clk。一般选择 osc_clk,也就是 24MHz 的晶振。

if((((CCM->CCSR) >> 2) & 0x1 ) == 0) /* 当前pll1_sw_clk使用的pll1_main_clk*/

{

CCM->CCSR &= ~(1 << 8); /* 配置step_clk时钟源为24MH OSC */

CCM->CCSR |= (1 << 2); /* 配置pll1_sw_clk时钟源为step_clk */

}

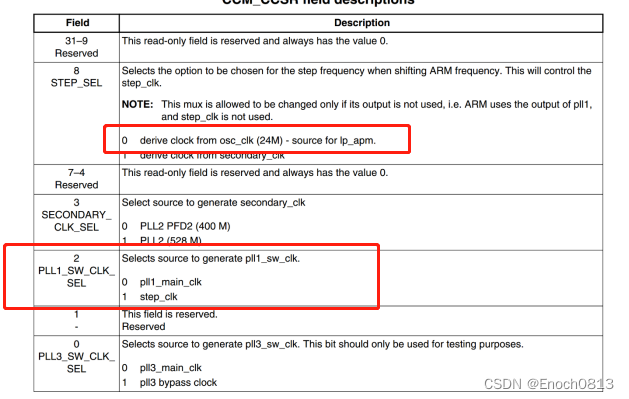

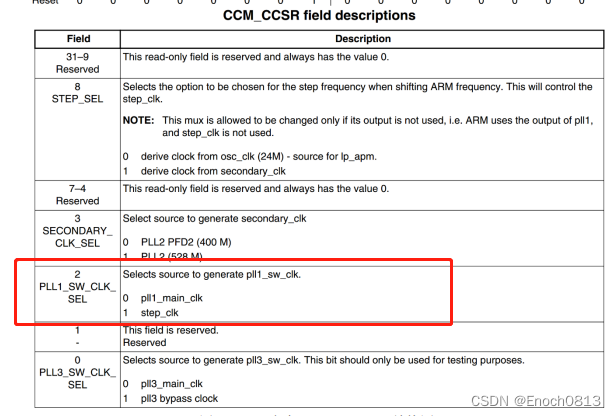

寄存器CCM_CCSR的配置如下所示:

由上图可知,PLL1_SW_CLK_SEL是第2位。所以要进行右移2位,然后变成最低位,如果是0,则代表是pll1_main_clk,如果是1,则代表是step_clk。所以如果判断是pll1_main_clk,我们则需要更改成step_clk。将step_clk的时钟源为24M的晶振。

CCM_ANALOG->PLL_ARM = (1 << 13) | ((66 << 0) & 0X7F); /* 配置pll1_main_clk=792MHz */

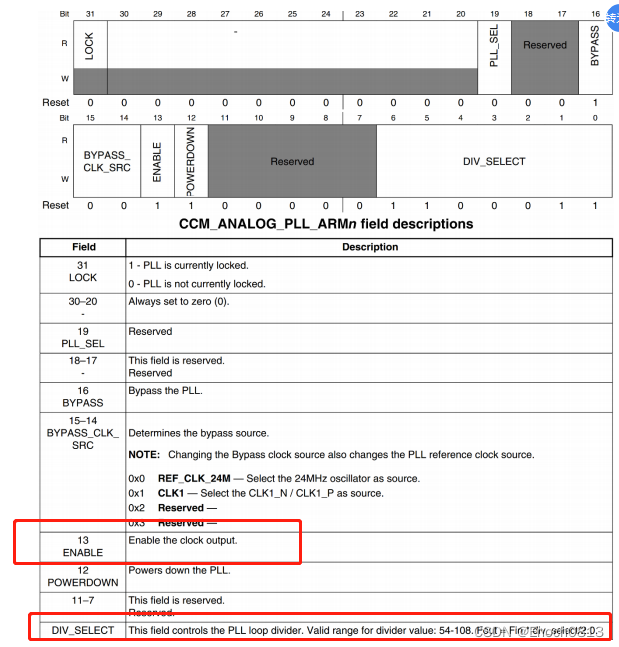

该寄存器的配置如下:

将第13位设置成1代表使能PLL1输出。

并且本例中设置ARM内核时钟为792MHz,即PLL1设置为792MHz,PLL1 CLK = Fin *div_seclec/2.0,Fin=24MHz,所以可以计算div_seclec为66。

CCM->CCSR &= ~(1 << 2); /* 将pll_sw_clk时钟重新切换回pll1_main_clk */

即将第2位设置成1即可。

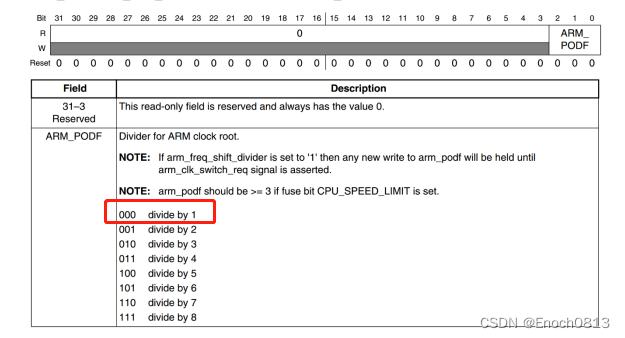

CCM->CACRR = 0; /* ARM内核时钟为pll1_sw_clk/1=792/1=792Mhz */

由于我们已经将PLL1设置成792MHz,那么我们只需要将分频系数设置为1即可。该寄存器配置如下图所示:

/* 2、设置PLL2(SYS PLL)各个PFD */

reg = CCM_ANALOG->PFD_528;

reg &= ~(0X3F3F3F3F); /* 清除原来的设置 */

reg |= 32<<24; /* PLL2_PFD3=528*18/32=297Mhz */

reg |= 24<<16; /* PLL2_PFD2=528*18/24=396Mhz(DDR使用的时钟,最大400Mhz) */

reg |= 16<<8; /* PLL2_PFD1=528*18/16=594Mhz */

reg |= 27<<0; /* PLL2_PFD0=528*18/27=352Mhz */

CCM_ANALOG->PFD_528=reg; /* 设置PLL2_PFD0~3 */

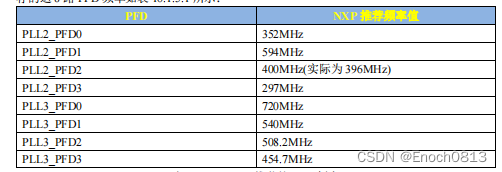

由上图可知,我们已经成功配置了PLL1时钟频率,那么接下来我们开始配置这PLL2和PLL3,其中由上图时钟树可知,PLL2有4路PFD时钟,PLL3有4路PFD时钟。

我们先设置PLL2的4路PFD时钟。

reg = CCM_ANALOG->PFD_528;

reg &= ~(0X3F3F3F3F); /* 清除原来的设置 */

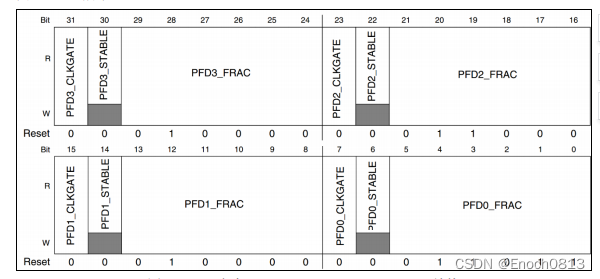

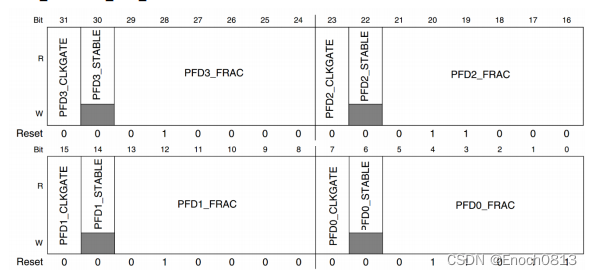

由上图可知,存器 CCM_ANALOG_PFD_528n 其实分为四组,分别对应PFD0~PFD3,每组 8 个 bit。

reg |= 32<<24; /* PLL2_PFD3=528*18/32=297Mhz */

reg |= 24<<16; /* PLL2_PFD2=528*18/24=396Mhz(DDR使用的时钟,最大400Mhz) */

reg |= 16<<8; /* PLL2_PFD1=528*18/16=594Mhz */

reg |= 27<<0; /* PLL2_PFD0=528*18/27=352Mhz */

CCM_ANALOG->PFD_528=reg; /* 设置PLL2_PFD0~3 */

我们就以 PFD0 为例,看一下如何设置 PLL2_PFD0 的频率。PFD0对应的寄存器位如下:

PFD0_FRAC: PLL2_PFD0 的分频数,PLL2_PFD0 的计算公式为 528*18/PFD0_FRAC,此为 可 设 置 的 范 围 为 12~35 。 如 果 PLL2_PFD0 的 频 率 要 设 置 为 352MHz 的 话PFD0_FRAC=528*18/352=27。

PFD0_STABLE: 此位为只读位,可以通过读取此位判断 PLL2_PFD0 是否稳定。

PFD0_CLKGATE: PLL2_PFD0 输出使能位,为 1 的时候关闭 PLL2_PFD0 的输出,为 0 的时候使能输出。

/* 3、设置PLL3(USB1)各个PFD */

reg = 0; /* 清零 */

reg = CCM_ANALOG->PFD_480;

reg &= ~(0X3F3F3F3F); /* 清除原来的设置 */

reg |= 19<<24; /* PLL3_PFD3=480*18/19=454.74Mhz */

reg |= 17<<16; /* PLL3_PFD2=480*18/17=508.24Mhz */

reg |= 16<<8; /* PLL3_PFD1=480*18/16=540Mhz */

reg |= 12<<0; /* PLL3_PFD0=480*18/12=720Mhz */

CCM_ANALOG->PFD_480=reg; /* 设置PLL3_PFD0~3 */

我们先设置PLL3的4路PFD时钟。

reg = 0; /* 清零 */

reg = CCM_ANALOG->PFD_480;

reg &= ~(0X3F3F3F3F); /* 清除原来的设置 */

reg |= 19<<24; /* PLL3_PFD3=480*18/19=454.74Mhz */

reg |= 17<<16; /* PLL3_PFD2=480*18/17=508.24Mhz */

reg |= 16<<8; /* PLL3_PFD1=480*18/16=540Mhz */

reg |= 12<<0; /* PLL3_PFD0=480*18/12=720Mhz */

CCM_ANALOG->PFD_480=reg; /* 设置PLL3_PFD0~3 */

寄存器 CCM_ANALOG_PFD_480n 和 CCM_ANALOG_PFD_528n

的结构是一模一样的,只是一个是 PLL2 的,一个是 PLL3 的。寄存器位的含义也是一样的,只是 频 率 计 算 公 式 不 同 ,

比 如 PLL3_PFDX=480*18/PFDX_FRAC(X=0~3) 。

如果PLL3_PFD0=720MHz的话,PFD0_FRAC=12;

如果 PLL3_PFD1=540MHz 的话,PFD1_FRAC=16;

如果PLL3_PFD2=508.2MHz 的话,PFD2_FRAC=17;

如果 PLL3_PFD3=454.7MHz的话,PFD3_FRAC=19。

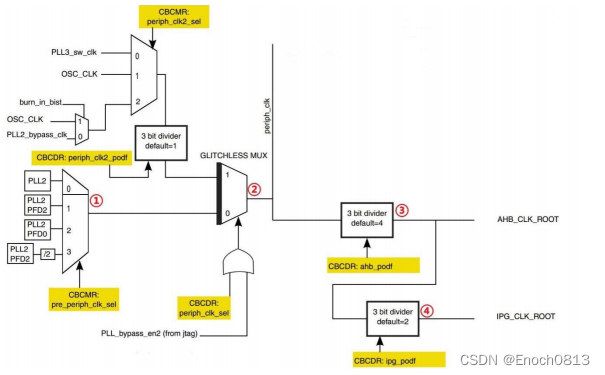

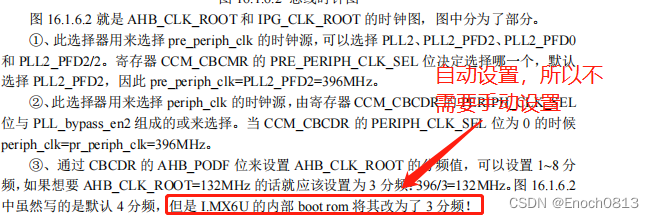

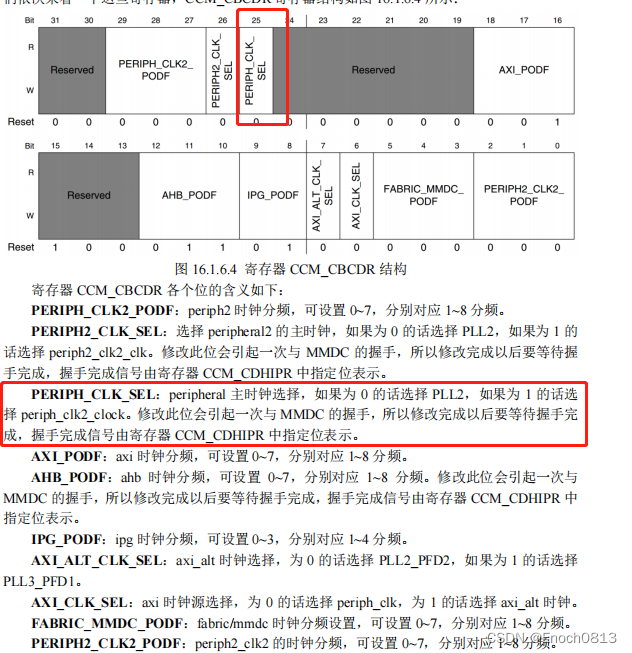

/* 4、设置AHB时钟 最小6Mhz, 最大132Mhz (boot rom自动设置好了可以不用设置)*/

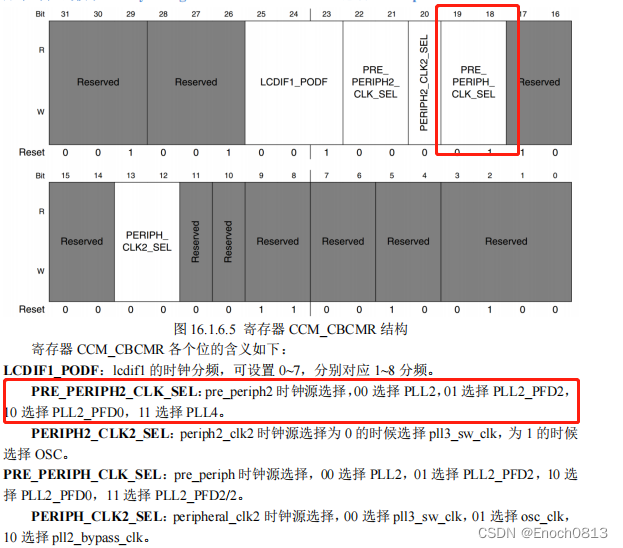

CCM->CBCMR &= ~(3 << 18); /* 清除设置*/

CCM->CBCMR |= (1 << 18); /* pre_periph_clk=PLL2_PFD2=396MHz */

CCM->CBCDR &= ~(1 << 25); /* periph_clk=pre_periph_clk=396MHz */

while(CCM->CDHIPR & (1 << 5));/* 等待握手完成 */

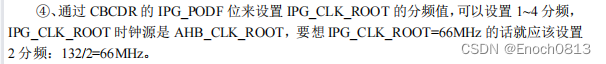

/* 5、设置IPG_CLK_ROOT最小3Mhz,最大66Mhz (boot rom自动设置好了可以不用设置)*/

CCM->CBCDR &= ~(3 << 8); /* CBCDR的IPG_PODF清零 */

CCM->CBCDR |= 1 << 8; /* IPG_PODF 2分频,IPG_CLK_ROOT=66MHz */

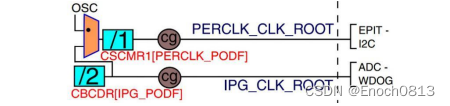

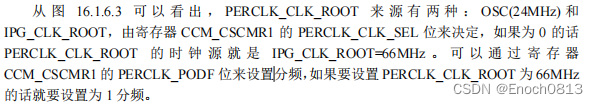

/* 6、设置PERCLK_CLK_ROOT时钟 */

CCM->CSCMR1 &= ~(1 << 6); /* PERCLK_CLK_ROOT时钟源为IPG */

CCM->CSCMR1 &= ~(7 << 0); /* PERCLK_PODF位清零,即1分频 */

其时钟结构图如下图所示:

从图中可以看出

使能所有的时钟部分

void clk_enable(void)

{

CCM->CCGR0 = 0XFFFFFFFF;

CCM->CCGR1 = 0XFFFFFFFF;

CCM->CCGR2 = 0XFFFFFFFF;

CCM->CCGR3 = 0XFFFFFFFF;

CCM->CCGR4 = 0XFFFFFFFF;

CCM->CCGR5 = 0XFFFFFFFF;

CCM->CCGR6 = 0XFFFFFFFF;

}

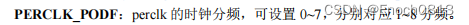

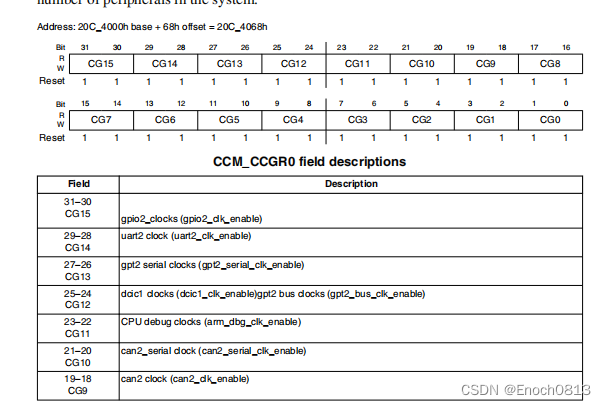

这里举CCGR0为例。

led初始化部分

led_init(); /* 初始化led */

这个部分在之前文章中已经讲过了

看完这篇文章你就彻底懂啦{保姆级讲解}-----(I.MX6U驱动LED灯《使用汇编语言编写》) 2023.4.17

看完这篇文章你就彻底懂啦{保姆级讲解}-----(I.MX6U驱动LED灯《使用C语言编写》) 2023.4.18

beep初始化部分

void beep_init(void)

{

/* 1、初始化IO复用,复用为GPIO5_IO01 */

IOMUXC_SetPinMux(IOMUXC_SNVS_SNVS_TAMPER1_GPIO5_IO01,0);

/* 2、、配置GPIO1_IO03的IO属性

*bit 16:0 HYS关闭

*bit [15:14]: 00 默认下拉

*bit [13]: 0 kepper功能

*bit [12]: 1 pull/keeper使能

*bit [11]: 0 关闭开路输出

*bit [7:6]: 10 速度100Mhz

*bit [5:3]: 110 R0/6驱动能力

*bit [0]: 0 低转换率

*/

IOMUXC_SetPinConfig(IOMUXC_SNVS_SNVS_TAMPER1_GPIO5_IO01,0X10B0);

/* 3、初始化GPIO,GPIO5_IO01设置为输出 */

GPIO5->GDIR |= (1 << 1);

/* 4、设置GPIO5_IO01输出高电平,关闭蜂鸣器 */

GPIO5->DR |= (1 << 1);

}

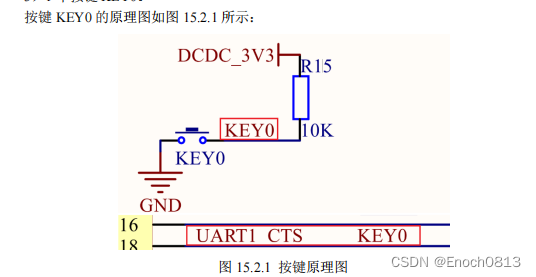

key初始化部分

void key_init(void)

{

gpio_pin_config_t key_config;

/* 1、初始化IO复用, 复用为GPIO1_IO18 */

IOMUXC_SetPinMux(IOMUXC_UART1_CTS_B_GPIO1_IO18,0);

/* 2、、配置UART1_CTS_B的IO属性

*bit 16:0 HYS关闭

*bit [15:14]: 11 默认22K上拉

*bit [13]: 1 pull功能

*bit [12]: 1 pull/keeper使能

*bit [11]: 0 关闭开路输出

*bit [7:6]: 10 速度100Mhz

*bit [5:3]: 000 关闭输出

*bit [0]: 0 低转换率

*/

IOMUXC_SetPinConfig(IOMUXC_UART1_CTS_B_GPIO1_IO18,0xF080);

/* 3、初始化GPIO */

//GPIO1->GDIR &= ~(1 << 18); /* GPIO1_IO18设置为输入 */

key_config.direction = kGPIO_DigitalInput;

gpio_init(GPIO1,18, &key_config);

}

按键中断初始化部分

void exit_init(void)

{

gpio_pin_config_t key_config;

/* 1、设置IO复用 */

IOMUXC_SetPinMux(IOMUXC_UART1_CTS_B_GPIO1_IO18,0); /* 复用为GPIO1_IO18 */

IOMUXC_SetPinConfig(IOMUXC_UART1_CTS_B_GPIO1_IO18,0xF080);

/* 2、初始化GPIO为中断模式 */

key_config.direction = kGPIO_DigitalInput;

key_config.interruptMode = kGPIO_IntFallingEdge;

key_config.outputLogic = 1;

gpio_init(GPIO1, 18, &key_config);

GIC_EnableIRQ(GPIO1_Combined_16_31_IRQn); /* 使能GIC中对应的中断 */

system_register_irqhandler(GPIO1_Combined_16_31_IRQn, (system_irq_handler_t)gpio1_io18_irqhandler, NULL); /* 注册中断服务函数 */

gpio_enableint(GPIO1, 18); /* 使能GPIO1_IO18的中断功能 */

}

IOMUXC_SetPinMux(IOMUXC_UART1_CTS_B_GPIO1_IO18,0); /* 复用为GPIO1_IO18 */

IOMUXC_SetPinConfig(IOMUXC_UART1_CTS_B_GPIO1_IO18,0xF080);

key_config.direction = kGPIO_DigitalInput;

key_config.interruptMode = kGPIO_IntFallingEdge;

key_config.outputLogic = 1;

gpio_init(GPIO1, 18, &key_config);

由上图可知,key所连接的接口为UART1_CTS,所以需要将UART1_CTS设置复用功能为GPIO功能。并且将其GPIO1_IO18 为下降沿触发中断。

GIC_EnableIRQ(GPIO1_Combined_16_31_IRQn); /* 使能GIC中对应的中断 */

调用函数 GIC_EnableIRQ来使能 GPIO_IO18 所对应的中断总开关,I.MX6U 中 GPIO1_IO16~IO31 这 16 个 IO 共用 ID99。

system_register_irqhandler(GPIO1_Combined_16_31_IRQn, (system_irq_handler_t)gpio1_io18_irqhandler, NULL); /* 注册中断服务函数 */

调用函数 system_register_irqhandler 注册 ID99 所对应的中断处理函数,其中GPIO1_Combined_16_31_IRQn为注册的中断号,gpio1_io18_irqhandler为注册的中断服务函数,当产生这个中断后,会自动进入gpio1_io18_irqhandler这个中断服务函数中。

gpio_enableint(GPIO1, 18); /* 使能GPIO1_IO18的中断功能 */

通过函数 gpio_enableint 使能 GPIO1_IO18 这个 IO 对应的中断。

按键中断服务函数部分

void gpio1_io18_irqhandler(void)

{

static unsigned char state = 0;

/*

*采用延时消抖,中断服务函数中禁止使用延时函数!因为中断服务需要

*快进快出!!这里为了演示所以采用了延时函数进行消抖,后面我们会讲解

*定时器中断消抖法!!!

*/

delay(10);

if(gpio_pinread(GPIO1, 18) == 0) /* 按键按下了 */

{

state = !state;

beep_switch(state);

}

gpio_clearintflags(GPIO1, 18); /* 清除中断标志位 */

}

调用函数 gpio_clearintflags 来清除 GPIO1_IO18 的中断标志位

while循环部分

while(1)

{

state = !state;

led_switch(LED0, state);

delay(500);

}

每隔500ms,led灯亮灭。

最终编译验证

按下 KEY 就会打开蜂鸣器,再次按下就会关闭蜂鸣器。LED0 会不断闪烁,周期大约 500ms。

结束语

如果觉得这篇文章还不错的话,记得点赞 ,支持下!!!

本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有涉嫌抄袭侵权的内容,请联系:hwhale#tublm.com(使用前将#替换为@)