说完DQ信号的读写测试,接下来,再来聊一聊命令及地址总线(CA Bus)的测试,由于CA bus只有一个信号流向,因此,只需要进行写操作的测试即可;

如下图所示,为JEDEC标准中定义的CA相关的测试参数,接下来,将对测试项逐一进行解析;

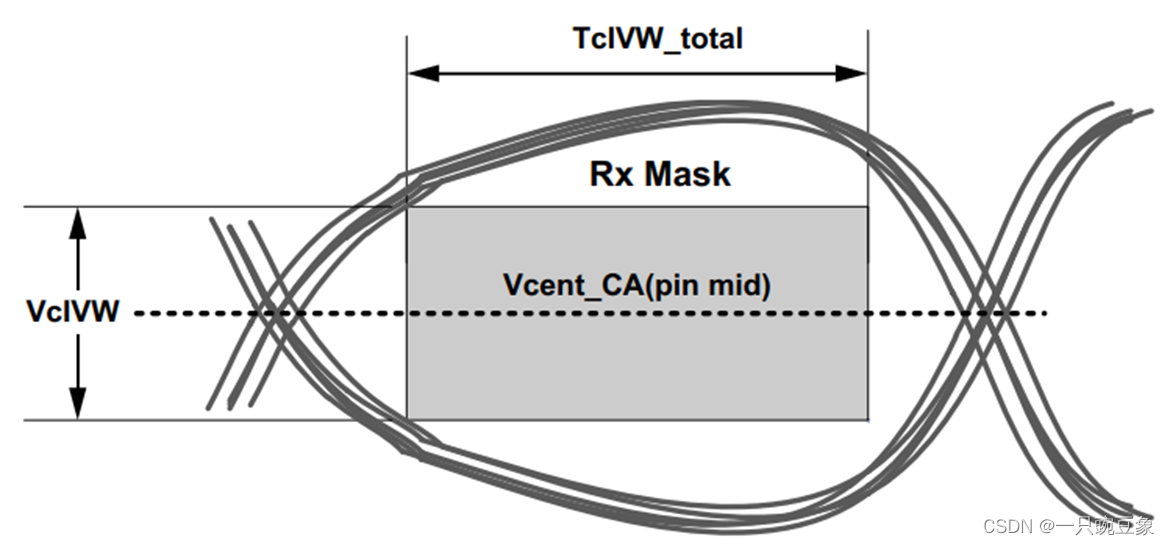

tCIVW和vCIVW的定义如下图所示,分别指的是CA信号眼图的时间宽度和电压幅度限制值,需要根据信号速率在上表中进行选择,这不是测试项,而是一个测试的固定参考值的选取;

如下图所示,为CA1眼图模板的实测波形,中间的灰色矩形框即由上述两个参数定义的眼图限制区域,测试时,信号眼睛要张开足够大,以避免碰触这一区域;

如下图所示:

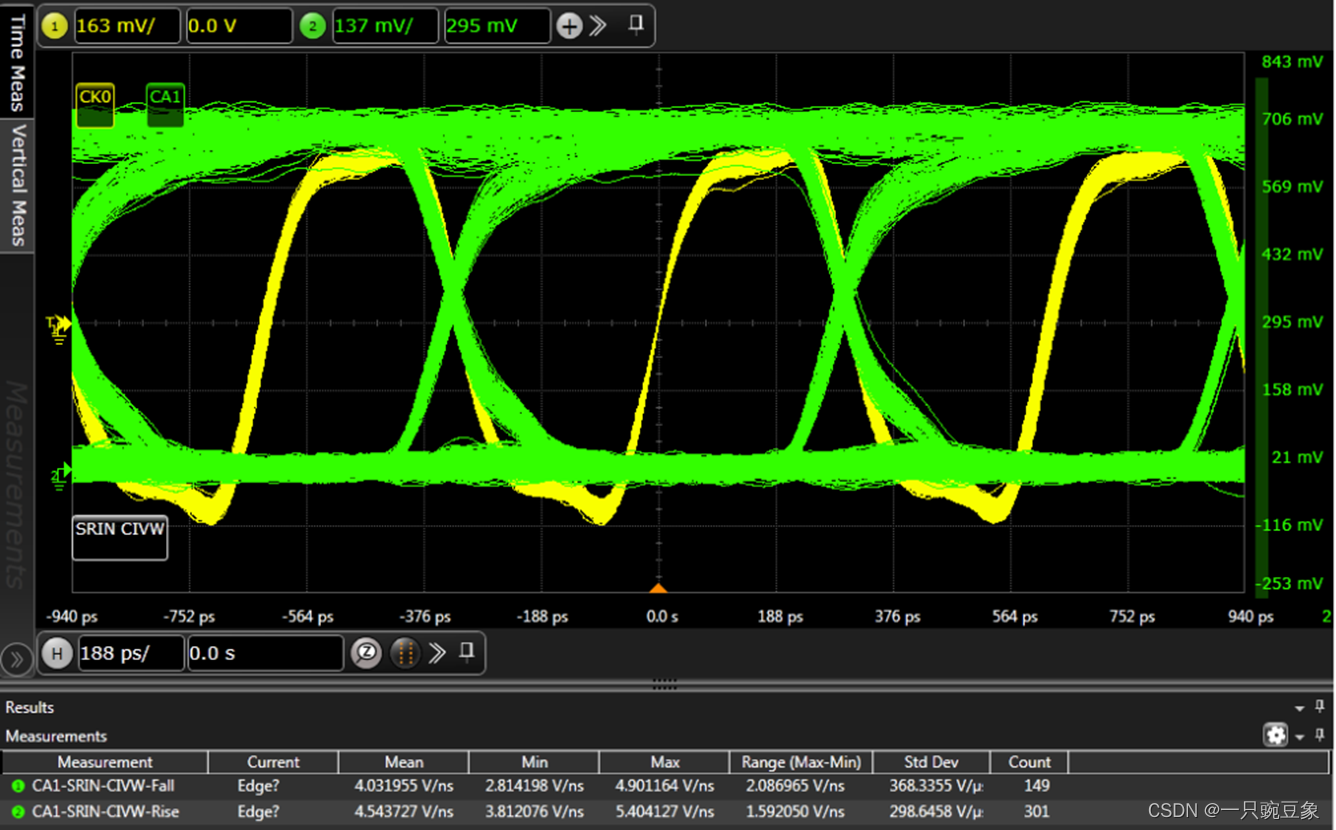

SRIN_cIVW,用于验证处于vCIVW电压区间内的信号边沿斜率,即下图中的tr和tf值;

tcIPW,用于验证在Vcent_CA上定义的最小CA输入脉冲宽度,也可以简单地理解为vCIVW的一半处;

如下图所示,为tcIPW的实测波形;

如下图所示,为SRIN_cIVW的实测波形;

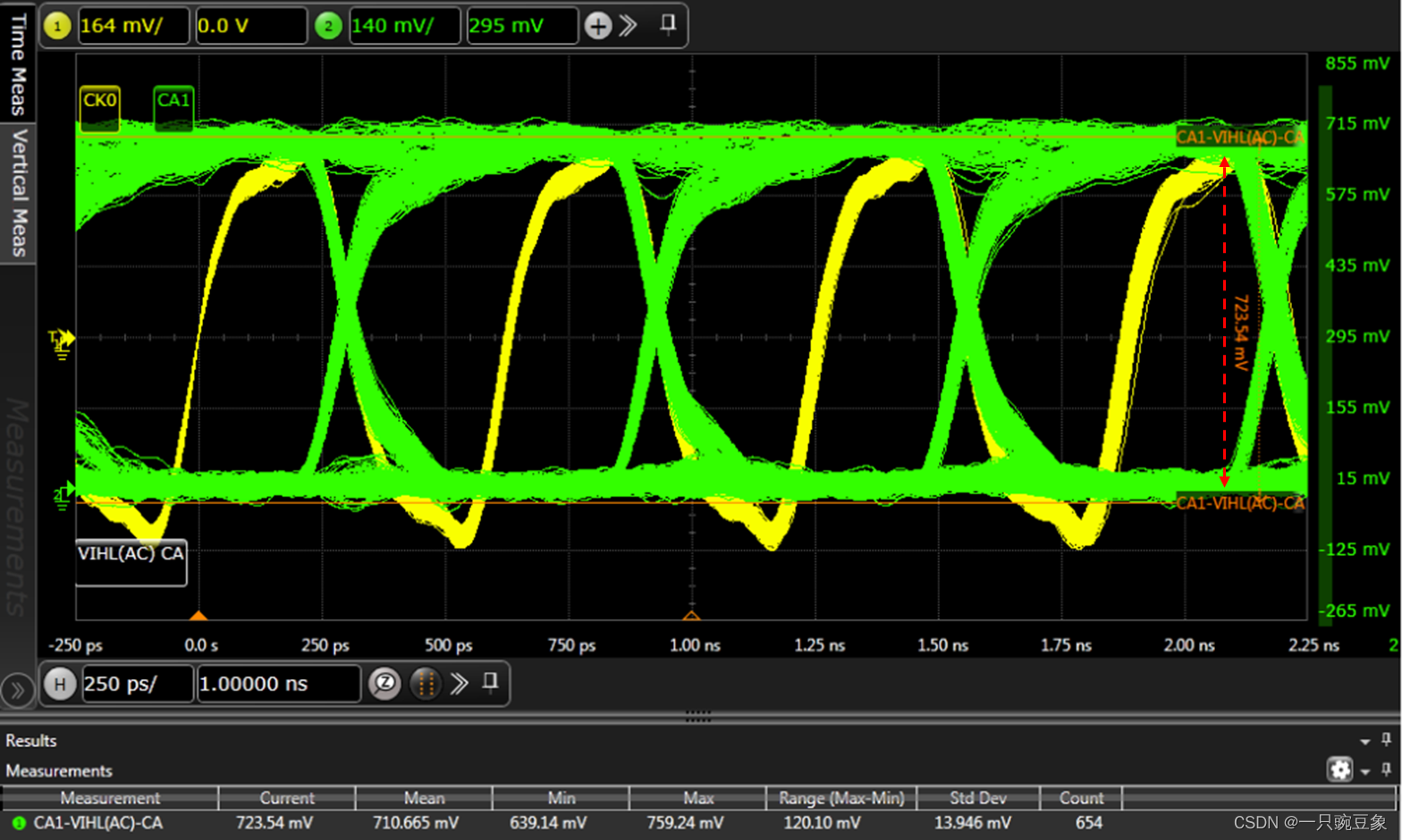

CA_VIHL_AC的定义如下图所示,用于验证以Vcent_CA为中心的峰峰值电压是否满足要求;

如下图所示,为CA_VIHL_AC的实测波形;

综上所述,相较于DQ信号,CA总线的时序测试项更少,并且,测试参数大同小异,因此,测试难度更低,总体来看,CK、DQS和DQ的时序是LPDDR4测试的重点,需要引起设计者足够的关注度。

扩展阅读:

LPDDR4 JEDEC标准测试实例解析--写操作_lpddr4测试_一只豌豆象的博客-CSDN博客

LPDDR4 JEDEC标准测试实例解析--读操作_一只豌豆象的博客-CSDN博客