带负载传输线

如果在传输线上有一个小的容性负载,信号会出现失真,上升时间也会降低。每个分立电容都会降低信号在其附近看到的阻抗。如果传输线上分布有多个容性负载(例如一个总线上每隔1.2inch有一个2pF的连接器残桩,或者一个内存总线上每隔0.8inch有一个3pF的封装和输入门电容),并且如果与上升时间的空间范围相比间距较短,那么每个容性不连续的反射可以忽略。这种情况下,看起来好像线路的特性阻抗已经降低了。具有均匀间隔电容分布的传输线就成为负载线。

每个不连续看起来就是一个低阻抗区域。当与电容之间的时间延迟相比上升时间较短时,每个不连续点对信号来说就像一个离散的不连续点。当上升时间比电容之间的时间延迟长时,低阻抗区域重叠,传输线的平均阻抗更低。

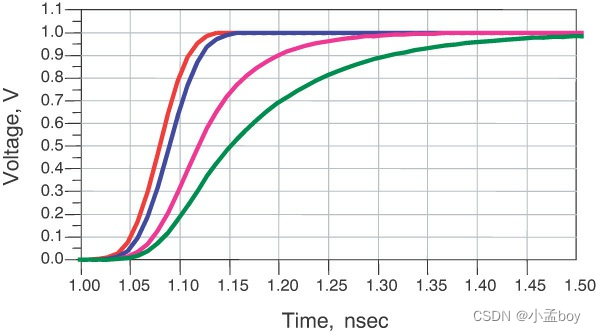

下图的例子中,50Ohm的传输线上间隔1inch有五个3pF的电容器,最后的10inch长度没有负载。每个电容器固有的10-90上升时间是2.2*0.5*50*3pF=150ps。尽管第一个例子中的初始上升时间为50ps,在第一个电容器之后,上升时间增加到150ps,并且经过每个电容器之后都会变的更长。

前几个电容器作为离散的不连续点是可见的,但是后面的电容器就会因为传输线较长的上升时间而被涂抹。当信号的上升时间比电容器不连续点之间的时延更长时,均匀分布的电容性负载会降低线路的表观特性阻抗。在这样的负载线上,传输线单位长度的电容会增加。单位长度的电容增加意味着更低的特性阻抗和更长的时延。

在一个均匀且无负载的传输线中,特性阻抗和时延与单位长度的电容和电感有关:

其中Z0是特性阻抗,LL是单位长度的电感,C0是无负载线单位长度的电容,Len是线长,TD0是传输时延。

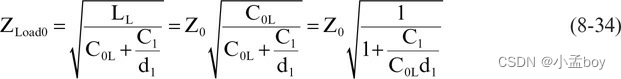

当存在均匀分布的负载时,例如以间距d1分布容值为c1的负载,那么单位长度的分布电容就增加了C1/d1,这就改变了传输线的特性阻抗和时延:

其中Z0表示无负载线的特性阻抗,Zloado表示负载线的特性阻抗,LL表示单位长度的电感,单位为pH/inch,CoL表示无负载线的单位长度电容,C1表示每个分立电容器的容值,d1表示每个分立电容器的间距,Len表示传输线长度,TD0表示无负载线的时延,TDload表示负载线的时延。

在50Ohm的传输线中,单位长度的电容大约3.4pF/inch,当添加的分布式电容负载与此相当时,特性阻抗和时间延迟可以显著改变。例如,如果3pF的负载按照1inch间距均匀分布在内存总线上,那么每inch额外增加的容性负载就是3pF/inch,负载特性阻抗下降到0.73*Z0,时延增加到1.37*TD0.

传输线的特性阻抗下降后,端接电阻也应该降低。或者,在分布式电容性负载所处的区域中,可以减小线宽,从而使空载阻抗更高。当连接负载时,负载线路阻抗将更接近阻抗的目标值。这种将离散电容添加到线路上以降低特性阻抗和增加时间延迟的效果正是过孔内部发生的情况。

焊盘中每层上的任何非功能焊盘,或者只是过孔穿过层间隙孔的额外电容,看起来都像是分立电容。这有助于降低通孔的阻抗,并会比预期的时间延时(基于通孔的长度和层压材料的介电常数Dk预期的时间延迟)更长。

这种情况下,等效Dk更高,能到8-15,原因就是过孔到平面的高分立负载电容。

感性不连续引起的反射

几乎每一个添加到传输线的串联连接都会有一些与之相关的串联环路电感。每个用于改变信号层的过孔、每个串联端接电阻器、每个连接器都会有额外的环路电感。信号会将这个环路电感视为传输线中的额外不连续性。

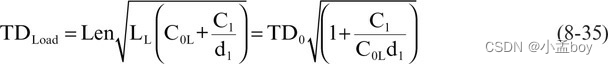

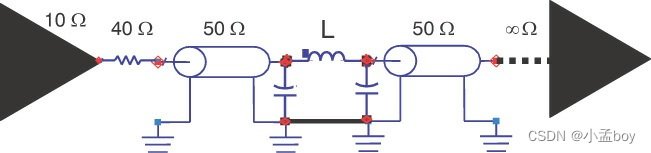

如果不连续性在信号路径中,则环路电感将由信号路径的部分自感主导,尽管与返回路径仍将存在一些部分互感。如果不连续性在返回路径中,则返回路径的部分自感将主导环路电感。在任何一种情况下,信号都对环路电感敏感,因为信号是沿着信号和返回路径之间的传输线传播的电流环路。对于入射的快速上升时间信号,较高的串联环路电感最初看起来像是较高的阻抗。这将导致对源端的正反射。下图显示了从均匀传输线测量的反射信号,该传输线在返回路径中经过一个小间隙。

均匀传输线的中间有一个感性不连续,这个感性不连续是由于返回路径的间隙导致的。上升时间大约50ps。

均匀传输线的中间有一个感性不连续,这个感性不连续是由于返回路径的间隙导致的。上升时间大约50ps。

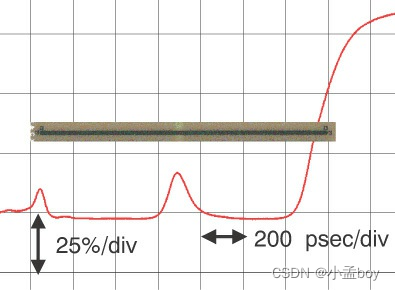

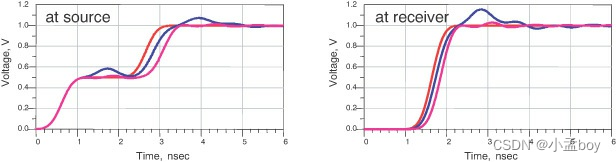

下图显示了不同电感不连续值的接收器和源处的信号。信号在近端的形状,先上升后下降,称为非单调性。信号并没有以稳定的上升速度单调地增加。此功能本身可能不会导致信号完整性问题。然而,如果有一个接收器位于近端,并且它接收到的信号增加超过50%,然后下降到50%以下,那么它可能会被错误地触发。但是,如果在近端有一个接收器,它接收到的信号先是增加到超过 50% 点,然后又下降到 50% 以下,它可能会被误触发。

如果失真发生在建立保持时间之外,信号的上升或下降边沿的失真并不会在接收端导致比特错误,但是如果时钟信号的边沿失真,则有可能导致时序错误,从而引起比特错误。需要尽可能避免非单调性出线,在远端,信号出现了过冲和时延。一般来说,电路中的最大电感是否可接受取决于电路的噪声余量和其他特性。这就需要对多种情况进行仿真。如果需要粗略估计最大可接受的电感,我们可以使用这个原则:当分立电感器的串联阻抗不连续超过了特性阻抗的20%时,我们认为电感过大,此时反射信号摆动达到了10%,通常是可接受的最大反射噪声。

如果电感的阻抗与特性阻抗相比很小,并且上升时间是线性斜坡,而上升时间正在通过它,我们可以通过以下方式近似估计电感的阻抗:

Zinductor表示电感的阻抗,L表示电感,RT表示信号的上升时间。

最大可接受的电感不连续性的估计值是通过将电感器的阻抗保持在线路阻抗的 20% 以下来设置的:

例如,如果50Ohm的传输线上信号上升时间是1ns,最大可接受的串联电感是Lmax=0.2*50*1ns=10nH。

粗略的估计:50Ohm的传输线中最大可接受的环路电感就是十倍的上升时间。反过来,如果某个不连续点存在一些环路电感,那么在反射噪声超过余量之前可接受的信号最小上升时间就是电感的十分之一。

如果连接器的环路电感是5nH,那么信号可接受的信号上升时间就是5nH/10=0.5ns。如果信号的上升时间是0.1ns,所有的感性不连续要保持小于10*RT=10*0.1=1nH。

基于这个估计,我们可以评估轴向引线电阻器和 SMT 终端电阻器的有用上升时间。轴向引线电阻器串联回路电感是10nH,所以可接受的上升时间就是10nH/10=1ns,SMT电阻器大约2nH,对应的上升时间就是2nH/10=0.2ns。

当上升时间处于纳秒状态时,轴向引线电阻器不是合适的部件,应避免使用。随着上升时间接近100psec,设计使用具有尽可能低的环路电感的SMT电阻器将变得越来越重要。

高性能SMT电阻器的两个最重要的设计特征是长度短和返回平面尽可能靠近表面。或者,集成到板或封装中的电阻器可以具有比2nH低得多的环路电感,并且可能是必需的。

感性不连续不仅会引起反射噪声,还会增加时延。当上升时间很短并且传输的上升时间主要由串联电感器决定,传输信号的10-90上升时间为:

TD10-90表示传输信号的10%-90%上升时间,L表示不连续点的串联环路电感,Z0表示传输线的特性阻抗,TDadder表示50%点的时延。

例如,一个10nH的感性不连续会增加10-90上升时间约10/50=0.2ns。增加的时延大约0.1ns。下图展示了1nH,5nH和10nH感性不连续下接收信号的传输时延。

补偿

有时候由于特定的连接器在电路中,不可避免的有串联环路电感。如果放任不管,可能会导致过度的反射噪声。一种称为补偿的技术被用来抵消一些这种噪声。

这个想法是试图欺骗信号,使其看不到大的电感不连续性,而是让它看到与线路特性阻抗匹配的传输线部分。毕竟,理想的传输可以近似为一阶,作为LC网络的单个部分。在这种情况下,线路任何部分的特性阻抗由下式给出:

LL表示传输线单位长度电感,L表示传输线任意部分的总电感,CL是传输线单位长度的电容,C表示传输线任意部分的总电容。

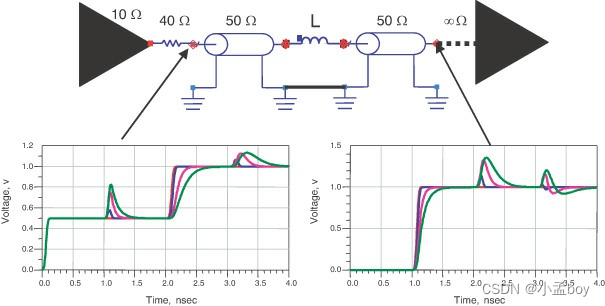

我们可以通过在任意一侧添加一个小电容器,将电感不连续性转化为传输线段,如图8-36所示。在这种情况下,电感器的表观特性阻抗为:

为了使反射噪声最小化,我们需要找到电容器的值,以便连接器的表观特性阻抗Z等于电路其余部分的特性阻抗Z。使用上述关系,要添加的电容为:

C1是要添加的总的电容补偿,L1是不连续电感。

例如,如果传输线特性阻抗50Ohm,电感10nH,需要补偿的总的电容就是10/(50*50)=0.004nF=4pF。为了获得最佳补偿,4pF的电容可以分成两个2pF放在电感器的两侧。

下图显示了无连接器、无补偿连接器和同一连接器补偿的三种情况下的反射和传输信号。根据系统的上升时间,反射噪声有时可以减少75%以上。

该技术也适用于所有电感不连续性,例如过孔和电阻器。根据焊盘中电容的相对量和串联电感,实际的不连续性可能看起来是电容性的或电感性的。

设计互连的目标是设计焊盘和其他特征,使结构看起来像一段均匀的传输线。通过这种方式,可以使一些电感不连续性,例如连接器,几乎消失。