ICC布局规划

Floorplan是ICC设计流程中非常重要的一环,Floorplan的好坏直接影响到设计的timing和布线布通率,

很多时候流程中反复主要发生在这步。

在ICC student lab中,对floorplan这么描述:

A floorplan defines: IO, filler and corner pad locations, or pin locations around the periphery; size

and shape of standard cell core or placement area; placement of macro cells; placement and

routing blockages; the power grid, which includes all pre-routed VDD/VSS metal, including core

and periphery rings, vertical and horizontal straps, and standard cell rails.

即Floorplan阶段主要内容:

·确定芯片的尺寸,形状

·IO单元、填充和角落pad的位置

·宏单元的放置和blockages的规划

·电源地网络的分布

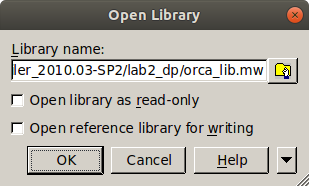

GUI>File>Open library GUI>File>Open Design

此时所有的宏单元(图中蓝色块)及标准单元(图中紫色块)都被摆放在坐标原点。

·读入管脚约束文件(逻辑网表中无physical only cells,如P/G pad cells VDD VSS、CORNER等,需要手动创建)

通常情况下,chip-level的floorplan由Core Area和Pad Area组成。Core区域用于摆放Macro和标准单元。

管脚约束文件需根据设计师的设计自己编写,摆放pad/pin的位置。根据上图所示的标准。side代表边,order定义每边的位置。

约束文件的内容实例如图所示,该文件用的是tcl格式。若使用tdf文件,read tdf文件只能识别

set_pad/pin_physical_constraints 命令而无法识别create_cell命令

set_pad_physical_constraints -pad_name stringpad_name objects

[-side side_number]

[-order order_number]

[-offset offset_distance]

[-orientation reflect | optimizeReflect]

[-min_left_iospace min_space_left]

[-min_right_iospace min_space_right]

icc_shell> source -echo scripts/pad_cell_cons.tcl 通过source tcl脚本输入管脚约束。

·创建布局规划

初始化floorplan,ICC2013后的版本不使用initial_floorplan,而是用create_floorplan

GUI>floorplan>create floorplan

Aspect ratio模式可以指定高宽比以及Core区域利用率 Width/Height可指定Core区域的高宽度

以及能够指定Pad area 和Core area之间的间隔。

(核利用率(Core Utilization)是指所有标准单元和宏单元面积与核面积的百分比,该值的大小决定了芯片的面积。

Horizontal row表示row为水平方向,选择Double back、Start first row、Flip first row表示第一行开始row是翻转

且背靠背,目的是便于相邻两行的标准单元的电源地线进行共享以减小芯片面积。)

初始化后即为定义好pad位置的pad area和设定好大小的core area,标准单元和宏单元都均匀摆放在外侧。

·插入pad fillers

IO pad之间可能存在空隙,加入pad fillers 是为了连接两个相邻的IO pad,实现从衬底到各层金属的相连,为IO内部

电路形成电源地供电环路。也就是说,在所有IO pad间插入pad fillers后,皆与P/G相连,其本身形成电源环,即pad ring。

GUI: Finishing -> Insert Pad Filler

在“pin/block cells”中填写library中pad fillers的cell名。填写时注意,后面的数字一般代表该filler的宽度,按照从大到小

的顺序进行填写,软件会按照从前到后的顺序插入pad filler。

icc_shell> insert_pad_filler -cell "pfeed10000 pfeed05000 pfeed02000 pfeed01000 pfeed00500 pfeed00200 pfeed00100 pfeed00050 pfeed00010 pfeed00005"

IO之间的摆放间距取决于封装厂的封装水平,在打线和封装能实现的情况下,IO之间可以挨着放不留间隙,不插入IO fillers。

·电源/地逻辑连线

GUI>Preroute>Derive PG connection

将标准单元和宏单元的电源/地端口、IOpad与电源线、地线之间进行逻辑相连,无物理布线。

Icc_shell>derive_pg_connection -power_net VDD -power_pin VDD -ground_net VSS -ground_pin VSS

/derive_pg_connection -power_net VDDO -power_pin VDDO -ground_net VSSO -ground_pin VSSO

/derive_pg_connection -power_net VDDQ -power_pin VDDQ -ground_net VSSQ -ground_pin VSSQ

Icc_shell>derive_pg_connection -power_net VDD -ground_net VSS -tie

·创建pad电源环

GUI: Preroute-> Create Pad Rings

在插入pad fillers后,pad本身已形成电源环。当不使用填充单元且并非所有pad都邻接,或者如果填充单元没有P / G引脚,

则需要创建一个pad ring以确保P / G的连续性。

·预先放置宏单元

对于Floorplan而言,人们更倾向于靠自己的经验去摆放Macro,摆放它们时不仅要考虑面积、互联线长等传统问题,还需要考虑Place阶段,Macro的摆放对于Place的影响。因为Macro从本质上讲就是一个巨型的标准单元,很多Macro也存在于各个模块内,在Floorplan阶段并不能和模块对等的考虑。对于这个问题,人们根据实际生活中的经验,提出一种边缘摆放(edgeplace)的方法。

几个原则设计:

1.macro尽量在core四周摆放。对于存储单元来说,存在数据端口和存储端口,并且周围需要有一些可测性电路。这使得这些单元引线众多且功耗巨大。将它们贴边放置,不仅有利于这些单元的供电,而且防止这些单元过多的引脚对其他单元的布线造成影响。

此外,对于大型的Macro,他们不仅仅需要与芯片内部的其他Macro或者标准单元进行数据交换,还需要与芯片外部的器件进行通信。这种数据交换就是靠IOpad进行的,因此摆放在离相应的数据端口附近,有利于减少互联线长度,减少线上延迟,并节约布线资源。

2.macro的pin的方向,尽量不要挡住port 的布线

要根据端口的连接关系与互连模块的位置来决定。如前面原理图中存储模块的端口方向朝向中央,因为中间的标准单元需要与存储模块进行数据交换,存在互连关系。使用后续所说的flylines及hierarchy工具查看逻辑连接关系

3.macro 之间要有margin,并且设置place blockage 。Macro与Macro之间要留有一定空隙,给予布线资源。特别是在Macro的间隙有端口的时候更是如此,设计者可以通过相邻Marco边界上端口的多少来决定留有多大的间隙比较合适,这样才不至于出现Pin Access的问题。

在ICC中这被称为Keepout Margin(避开圈),是blockage的一种,只是比较特殊,它会随着cell一起移动。

Keepout Margin有hard和soft之分,hard区域不允许任何Cell放置在该区域,当几个Macro之间有congestion问题时,可以添加一些Keepout Margin,阻碍buffer, inverter的插入。soft则在coarse place的时候不允许任何Cell放入其内,但是在optimization以及legalization的时候是允许Cell放入其内的,也就是只允许Buffer加入其中。Keepout Margin并不是独立存在的,而是依附于Macro周围,可随Macro移动的。所以它是专门用来控制Macro和其他单元之间距离的一种功能。

4.尽量让STD cell 的区域是完整的,不要有窄沟道。

标准单元在布局时,按照Row所划定的高度一排一排的摆放。在给各个器件供电时,可以使用横向的电源线将处于同一高度的器件连接在一起统一供电。若是将标准单元都摆放在芯片区域的中心,而大的Macro摆放在四周,就可以使标准单元方便的只用一条电源线连接在一起,而不会被高度不统一的Macro打断。对电源网格的设计提供了巨大便利。

lab中介绍了一种使用飞线(Flylines)的方法来设计macro的摆放

首先,GUI>Select>Cells>by types>选择Macro>ok,再选择工具栏中的Flylines

然后,Show flylines>Selected to IO>Apply

设计上会显示出Macro和IO的逻辑连接关系,而我们手动摆放与IO有逻辑连接的Macro的位置,减少线延迟

设置blockage,GUI>Placement>Set Keepout Margin

Icc_shell>set_keepout_margin -type hard -all_macros -outer {10 10 10 10}

通过View Setting>Cell>Keepout Margin 可以看到设置的keepout

如果宏单元较多,可以让工具先摆放一遍。

Icc_shell>set_fp_placement_strategy \

-auto_grouping high \ #将Macro进行分组

-macros_on_edge on \ #将宏单元置于尽可能接近芯片的边缘

-sliver_size 10 \ #设置macro之间的间隔为10

-virtual_IPO on #打开虚拟IPO以模仿时序优化(并防止不必要的布局优化)

Icc_shell>set_fp_macro_options -legal_orientation {W E} [get_cells I_ORCA_TOP/I_PCI \_TOP/I_PCI_WRITE_FIFO/PCI_FIFO_RAM_*] #限制某些RAM的合法布局方向

然后使用命令

Icc_shell>create_fp_placement –timing_driven -no_hierarchy_gravity 进行自动放置

–timing_driven表示时序驱动 -no_hierarchy_gravity表示“无层次结构”(即无逻辑地粗略放置,“逻辑层次结构”不会影响此非层次结构或平面布局的放置)

此时宏单元和标准单元均已摆放好。但是在floorplan阶段,我们只关心宏单元的位置,标准单元的摆放在后续的place阶段完成,所有可以通过命令将标准单元移除。

Icc_shell>remove_placement -object_type standard_cell

在摆放好所有的macro后,将所有的macro锁定(设置为dont_touch属性),因为在布局阶段的命令会使其移动。并且在检查拥塞(congestion)的时候软件会报错。

所以,使用命令将macro都fix住。Icc_shell>set_dont_touch_placement [all_macro_cells]

左侧点击宏单元,选中的宏单元上出现叉号,同时属性栏中is_fixed为true,表示已被锁定。(q可查看完整属性)

·检查拥塞(congestion)

首先先介绍一下拥塞的概念。Congestion通常指绕线阻塞,即局部或者整体绕线资源不够的现象。

拥塞代表一个GRC(Global Routing Cell)边界上需要的布线资源与可用布线资源的比值,当所需布线资源大于可用布线资源时,就会存在拥塞。关于GRC的详细解释在Route阶段的Global Routing进行介绍。

Floorplan阶段的预估congestion是通过Global Route进行判断,仅仅只是虚拟的走线判断走线资源是否满足,没有实际布线。

GRC每条边可用于布线的布线通道(track)的数目(Capacity),以及布线需要的布线通道的数目(Demand)。图中画出了一个GRC,边上的数值即为Demand/Capacity。Demand – Capacity即为溢出(Overflow)的数目,如果存在Overflow,则Congestion Map中就会将GRC的那条边进行高亮,Overflow越大,则颜色越偏向于暖色调(即红色)。

ICC中查看Congestion Map的方法是GUI>Route>Global Route Congestion Map

Icc_shell>report_congestion -grc_based -by_layer -routing_stage global

同时可以查看关于congestion的报告

max overflow代表至少有一个GRC边界要额外走13条线,可是却没有额外的布线资源来供它进行布线。总共的GRC overflow是2.73%,意味着设计中所有GRC的边界大约有2.73%存在着overflow。

根据经验,一般最大的Overflow如果超过10基本上这个设计就无法布通了,最好不要超过3~5。另外如果总共的overflow超过2%,也可以认为设计在后边很难绕通。这些说明Floorplan不是很好,需要修改Floorplan或者重新进行Floorplan。

该阶段,如果出现很大的拥塞,问题可能在于宏单元之间的摆放,由其是Memory,多个Memory的数据线和地址线在狭窄的空间内无法找到足够的布线通道,通常会发生Congestion。其次是宏单位周围是否放置Placement Blockage,使得其与标准单元太近。宏单元的摆放规则和出pin方向也有很大的影响。

·电源地网络设计

电源地网络并不是布的越多越好。过多的电源地会占用大量的布线资源,此外,在placement阶段我们常常设置在电源地下方摆放标准单元的密度或是不摆放标准单元以防止出现拥塞。当电源地太多时,设计的利用率会大大降低。

其中,Core ring和straps可以手动创建,也可以使用ICC的Synthesize Power Network(SPN)创建。这个稍后再介绍,首先先介绍Macro ring。

lab中关于设置Macro ring的命令在scripts/macro_pg_rings.tcl脚本中。

首先是选择你要创建Macro ring的Macro group所在的区域,GUI>Preroute>Power Network Constraints>Region Constraints

选择第二项Set specified region,在layout windows上选择区域 选择ok,图中红边框区域即为选中的创建macro ring的区域。

icc_shell>set_fp_rail_region_constraints -polygon {undefined{378.610 1296.850} {378.610 951.725} {614.420 951.725} {614.420 1296.850}}

使用以下命令为所创建的macro ring设置属性

icc_shell>create_fp_group_block_ring -nets {VDD VSS}

-horizontal_ring_layer METAL5 -horizontal_ring_offset 0.78 -horizontal_ring_width 3

-vertical_ring_layer METAL4 -vertical_ring_offset 0.73 -vertical_ring_width 3

-horizontal_strap_layer METAL5 -horizontal_strap_width 3 -vertical_strap_layer METAL4 -vertical_strap_width 3

此时layout windows上会显示出软件设计的macro pg ring的方案,你可以通过勾选METAL层来修改方案。

然后使用命令icc_shell>commit_fp_group_block_ring 即可以生成macro ring

icc_shell>set_fp_rail_region_constraints -remove 移除设置的区域,进行下一组的创建

接着是Synthesize Power Network(SPN)。在设计库中已经指定了TLU+文件的情况下,设计师对功耗、电压降、金属层次、宽度等给出相应的约束,软件就会给出一个尽量满足要求的电源地规划方案。

对布strap金属层进行尺寸设置, GUI>Preroute>Power Network Constraints>Strap Layers Constraints

在Layer中选择要设置的层次。Direction选择方向,一般是库中默认。设置Max/Min strap、Max/Min width、PG spacing 后点击Set,相应的命令为:

Icc_shell>set_fp_rail_constraints -add_layer -layer METAL5 -direction horizontal -max_strap 24 -min_strap 2 -min_width 2 -max_width 4 -spacing 0.6

set_fp_rail_constraints -add_layer -layer METAL4 -direction vertical -max_strap 24 -min_strap 2 -min_width 2 -max_width 4 -spacing 0.6

对Core ring的创建进行属性设置,GUI>Preroute>Power Network Constraints>Ring Constraints

设置Core ring的Horizontal/Vertical layers Max/Min ring width 并设置straps延伸至core ring, 相应命令:

Icc_shell>set_fp_rail_constraints -set_ring -horizontal_ring_layer { METAL3 } -vertical_ring_layer { METAL2 } -ring_max_width 12 -ring_min_width 10 -extend_strap core_ring

此外,在之前为macro group创建macro ring时,若有单独的block没有添加macro ring,在这一步也可以进行添加。

GUI>Preroute>Power Network Constraints>Block Rings Constraints ,同样对其进行属性设置。

icc_shell>set_fp_block_ring_constraints -add

-horizontal_layer METAL5 -horizontal_width 3 -horizontal_offset 0.600

-vertical_layer METAL4 -vertical_width 3 -vertical_offset 0.600

-block_type instance -block {I_CLOCK_GEN/I_PLL_PCI} -net {VDD VSS}

最后进行全局的布电源地的设置,设置电源布线不经穿过Macros

GUI>Preroute>Power Network Constraints>Global Constraints

Icc_shell>set_fp_rail_constraints -set_global -no_routing_over_hard_macros

到此,对SPN的设置完成,可以进行SPN。GUI>Preroute>Synthesize Power Network

Icc_shell>synthesize_fp_rail -nets {VDD VSS} -voltage_supply 1.32 -synthesize_power_plan -power_budget 350 -pad_masters { pv0i pvdi }

在设置了TLU+文件后,对功耗,工作电压进行设置,并且设置目标IR-Drop不得高于10%的工作电压,软件会给出如图中所示的电源地规划方案,并且在layout window右侧产生生成方案的IR-Drop分析,如果最差情况(即红色区域)能够满足目标小于10%工作电压,则满足要求。则通过命令:

Icc_shell>commit_fp_rail 软件自动产生满足规则的PG strap和Core ring

同样说一下手动创建Core ring的方法:GUI>Preroute>Create Rings 选择“Rectangular”,表示以矩形方式创建。另一选项“Rectilinear”表示以线条方式创建,该选项可以创建非矩形形状的环。对于Core PG Rings的创建一般用矩形来创建,所以选择“Rectangular”。

在Nets中选择需要创建电源地环的Nets,在Around中选择创建的区域/模块。可以为Core区域,同时也可以选择macro生成macro rings。在side栏中可以选择创建环的边、宽度width、层次layer以及偏移offset,包括相对与core的绝对偏移或是满足DRC间距的偏移。

在电源环和strap都创建好了之后,我们需要将IO、宏的电源地连接到CorePG Rings上:

GUI>Preroute>Preroute Instances icc_shell>preroute_instances

接着为电源地Rail布线(给标准单元供电的电源和地线),GUI>Preroute>Preroute Standard Cells

Icc_shell>preroute_standard_cells -fill_empty_rows -remove_floating_pieces

因为某些Row上面可能没有放置标准单元,所以需要选择fill_empty_rows,填充这些空的Row。

电源地网络的创建完成

·IR-Drop的分析

无论是手动创建或是软件自动生成的电源地网络,都需要进行IR-Drop的分析,只有满足条件才能继续后面的设计。与进行SPN后的分析相同,Icc_shell>analyze_fp_rail -nets {VDD VSS} -voltage_supply 1.32 -power_budget 350 -pad_masters { pv0i pvdi}

分析最大IR-Drop与voltage_supply是否满足条件。

floorplan阶段的设计完成,标准单元的摆放只是虚拟的摆放,没有实际物理意义,

Icc_shell>remove_placement -object_type standard_cell移除标准单元

Icc_shell>save_mw_cel -as floorplan_complete 保存设计

Icc_shell>write_def -version 5.6 -placed -all_vias -blockages -routed_nets -specialnets -rows_tracks_gcells -output design_data/ORCA.def输出包含floorplan信息的def格式文件 用作后续placement