- 解决办法:把mif文件放在根目录下,和文件夹db同一级,File name就会直接显示这个文件名字

- 总结主要问题应该还是出在文件路径

- 主要参考这篇博客 FPGA的ROM-IP核配置问题 https://blog.csdn.net/weixin_41059920/article/details/89841835

- 参考博客 modelsim仿真ROM IP核没有输出数据问题如何解决https://blog.csdn.net/weixin_44939178/article/details/111928005

module ROM(clk, rst_n, q);

input clk;

input rst_n;

output [7:0] q;

wire [7:0]addr;

//控制地址变化

addr_ctrl addr_ctrl_dut(

.clk(clk),

.rst_n(rst_n),

.addr(addr)

);

//IP核:ROM

rom_8x256 my_rom_dut(

.address(addr),

.clock(clk),

.q(q)

);

endmodule

module addr_ctrl(clk, rst_n, addr);

input clk;

input rst_n;

output reg [7:0] addr; //控制ROM的地址变化(0~255)

always@ (posedge clk,negedge rst_n)begin

if(rst_n == 1'b0)

addr <= 8'd0;

else if(addr <= 8'd255)

addr <= addr + 8'd1;

else

addr <= 8'd0;

end

endmodule

`timescale 1ns/1ns

module tb_ROM();

reg clk;

reg rst_n;

wire [7:0] q;

initial

begin

clk = 1'b1;

rst_n <= 1'b0;

#10

rst_n <= 1'b1;

end

always #10 clk = ~clk;

ROM ROM_inst

(

.clk(clk),

.rst_n(rst_n),

.q(q)

);

endmodule

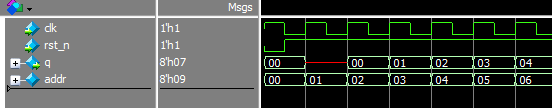

- 存在两个触发器,数据出现比地址出现晚了 2 个时钟周期

-

踩坑记录点

-

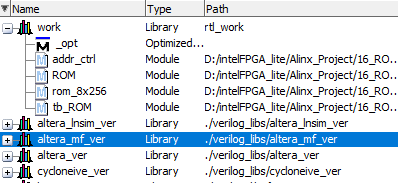

没有altera_mf文件仿真库,在modelsim中确实没看见这个仿真库,但有alter_mf_ver应该就行了

-

我在这个安装目录下看到是有这个文件的 \17.1\quartus\eda\sim_lib\altera_mf.v

-

看mif文件是否加载进来可以直接点击Memory List选项卡,双击查看是否有数据

-

我试了这个改路径方法不太行 modelsim仿真ROM IP核遇到无法读取mif文件的解决方法 https://blog.csdn.net/huhangf362/article/details/86539478

-

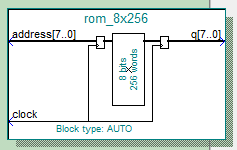

查看rom_8x256文件可以看出mif文件在project文件夹中

-

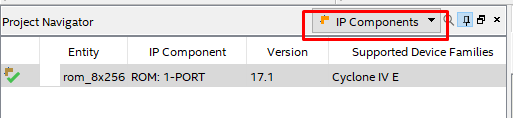

另外修改IP核的方法,把选项卡切到IP Components双击IP核即可

本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有涉嫌抄袭侵权的内容,请联系:hwhale#tublm.com(使用前将#替换为@)