一、PCB布局要求

1、可制造性设计(DFM):可装配性(DFA)、可维修性(DFS)、可测试性(DFT)

2、电气性能实现:ccc、fcc、ce认证,EMC\SI\PI及散热要求

3、合理的成本:层数也多成本越高

4、美观度

二、布局的一般原则

1、元件最好单面摆放,双面摆放时底层贴片;

2、合理安排接口元件方向;

3、高、低压之间电气隔离;

4、电气连接紧密的元件最好摆放一起;

5、对于易产生噪声的元件,时钟发生器和晶振等高频元件,布局时尽量靠近CPU时钟输入。

6、电源和芯片周围尽量摆去耦电容和滤波电容

7、主要芯片布局:限高、安装、操作、散热、高频信号

8、布线通道和电源通道:芯片的物理位置和层叠设计,考虑大电流输出的电源模块靠近主用电芯片。

9、元件的编号紧靠元件的边框位置

10、EMC\SI\散热设计

三、布局的准备

1、库路径的加载:user preference editor中选择paths-library-value,devpath是devices的路径,padpath焊盘的路径设置,psmpath是symbol的路径。

2、绘制板框:outline,route keepin,package keepin

3、导入netlist网络表:

4、叠层设置:cross-section

5、进入pcb布局

四、手动摆放相关窗口及摆放元件

1、摆放元件类型

components by refdes网络表中的元件包含元件编号列表、

components by net group包含网络群组、

module instances原理图中定义的module、

module definition、

package symbols封装库符号、

mechanical symbols机械符号、

format symbols过滤器,在过滤器选择器件

2、selection filters

match:输入元件编号

Property value:元件属性及标值显示

room:区域

Part#:part number

net:网络名称

Schematic page number:元件所在原理图页面显示元件

Place by refdes:元件类型进行摆放

Number of pins元件管脚数

3、进入摆放模式

五、元件摆放常用操作

1、移动元件edit-move(快捷键shif+F6):旋中元件拖动到位置单击,再去选择其他元件,也可以框选元件进行move。

说明:move命令下的option选项,ripup etch移动元件会自动删除与元件连接的走线;

Slide etch移动元件连接线一直保持,走线也被拖长,但是只会平滑移动;

Stretch etch移动元件时与元件连接的走线会一直保存连接关系,移动元件其相连的走线也被拖长;

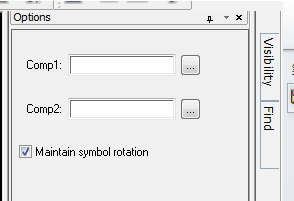

2、移动(move)命令中的旋转元件:move命令中,单击元件后右键选择rotate进行旋转。

说明option选项中

type选择旋转方式:absolute表示元件逆时针旋转一个固定角度,incremental表示元件以一定角度增量旋转;

angle对角度进行设置;

point选项选择旋转中心:sym origin表示按照符号的原点旋转,bady center表示元件中心旋转,user pick鼠标点击点,sym pin#按照某引脚中心旋转。

3、尚未摆放时设置旋转:从placement对话框摆放到工作区域,尚未摆放,右侧options选项卡进行旋转,设置好参数后放置角度就会变化。

4、修改默认元件摆放的旋转角度:setup -design parameter editor命令,在弹出的对话框中symbol选项设置angle

5、一次进行多个元件旋转:框选元件

6、镜像已经摆放的元件:edit-mirror进行镜像,原来在top层,翻转到bottom层。

7、摆放过程中镜像元件:元件悬于鼠标上,选择option中的mirror,进行镜像操作

8、右键mirror镜像元件:选择元件,右键进行镜像操作。

9、默认元件摆放镜像:setup -design parameter editor命令,勾选mirror选项

10、元件对其操作

11、元件位置交换swap命令:place-swap-components命令,进行元件交换

12、highlight和dehighlight:右键进行操作

六、quick place窗口

1、place by property/value:按元件属性及标值选择可摆放的元件;

2、place by room:按照room属性进行摆放;

3、place by part number:按照料号进行摆放;

4、place by net name:选择设计网络名称进行摆放;

5、place by schematic page number:原理图页进行摆放;

6、place all components:摆放所有元件;

7、place by refeds :元件类型;

8、place by partition:利用design entry HDL绘制原理图,按照分割来摆放;

9、by user pick:摆放元件与用户单击位置;

10、around package keepin :摆放元件于允许摆放区域;

11、place components from modules :摆放模块元件;

12、unplace symbols count:未摆放的元件数量;

13、edge:top、bottom、left、right;

14、board layer:top顶层,bottom底层;

七、按room摆放元件

基本步骤给元件添加room属性,在电路板中创建room区域,其值与元件room值相同,然后执行命令。

1、给元件赋予room属性:

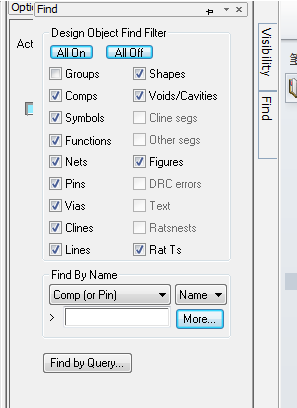

Edit-property命令,通过右侧find选项卡,find by name栏comp(or pin),然后单击more进入find by name or property对话框

选好器件,点击apply

找到room属性,进行value进行设置,点击apply

2、按room摆放元件:

摆放room outline,选择setup-outline-room outline命令,弹出对话框进行设置

画出room区域后,进行quickplace,place by room进行放置

八、原理图同步按room摆放元件

在原理图上设置好,room属性,导入网表。

1、原理图上选择器件,右键edit property,进入属性编辑

2、filter by :cadence-allegro,找到room属性进行赋值

3、赋值完成后,选择current properties,查看当前属性

4、点击apply保存后,进入tools-create netlist

5、导入网络表,绘制room区域,再进行quickplace

九、按照原理图页面摆放

1、选择DSN项目,edit-browser-part

2、选择列表中的元件,点击edit-properties命令,弹出browser spreadsheet对话框,单击new,弹出new property,在name文本框中输入属性名称page,value中输入page1,单击ok。

3、进入create netlist的setup

点击edit

文本编辑,添加PAGE=YES

4、allegro导入的网络表,进行quickplace

十、capture和allegro交互摆放

1、同时打开原理图和pcb图,在原理图中option-preferences,打开miscellaneous,勾选intertool communication选项中enable intertool communication

2、这样allegro进入放置模式时,在原理图中选择元件,allegro中鼠标自动悬挂元件;在pcb中选中元件,在原理图中也会高亮显示。

十一、飞线rats的显示与关闭

1、工具栏操作显示与关闭

2、display下的show rats、blank rats

3、X显示,可以让电源类的飞线以x形式显示Logic-identify dc net

十二、swap pin 和function功能

1、swappin是用来交换一个元件内部相同pingroup的元件引脚

2、元件同一个PinGroup中的引脚可以进行互换,在原理图的lib元件库进行设置,设置好元件库替换,然后生成新的网络表,导入allegro。

3、function swap用来交换同一个芯片内部不同gate模组

十三、元件相关其他操作

1、导出元件库file-export-libraries

勾选 no library dependencies,表示导出的文件不依赖源文件位置

2、更新元件

设计过程中有可能删除或修改元件丝印及引脚焊盘,这时需要updata symbols。

点击place下的updata symbols,配置好选项点击refresh

3、元件布局的导出和导入

十四、焊盘的更新、修改和替换

十五、阵列过孔

十六、模块复用