CMOS时序模型基础

大多数简化的时序模型基于以下公式:

D

e

l

a

y

o

f

a

c

e

l

l

=

I

n

t

r

i

n

s

i

c

d

e

l

a

y

+

t

r

a

n

s

i

t

i

o

n

d

e

l

a

y

+

s

l

o

p

e

d

e

l

a

y

\large \color{blue} Delay \ of \ a \ cell = Intrinsic \ delay + transition \ delay + slope \ delay

Delay of a cell=Intrinsic delay+transition delay+slope delay

分别解释如下:

- 当一个单元由另一个相同的无负载单元驱动时,单元的本征延迟(Intrinsic delay)被定义为无负载单元的传播延迟。驱动单元和被驱动单元都应该是无负载的,即要求驱动单元间接驱动被驱动单元。

-

转换延迟(transition delay)被定义为驱动电容性负载的单元的额外延迟(除了固有延迟),但由另一个相同的无负载单元驱动。发生这种转换延迟的原因是,由于单元必须驱动电容性负载,其输出斜率与无负载情况相比变得不那么陡峭(即上升和下降时间增加)。

-

斜率延迟(slope delay)是由具有转换延迟的相同单元驱动的无负载单元的额外延迟(除了固有延迟和可能的转换延迟)。驱动单元驱动电容性负载(因此它表现出转换延迟),因此驱动单元的输出斜率比没有负载电容的驱动单元的输出斜率要小,较缓的坡度会导致被驱动单元的额外延迟。

线性延时模型

在该模型中,转换延迟被建模为与负载电容成线性比例,而斜率延迟被建模为与驱动波形的转换延迟成线性关系:

t

r

a

n

s

i

t

i

o

n

d

e

l

a

y

=

o

u

t

p

u

t

r

e

s

i

s

t

a

n

c

e

×

l

o

a

d

c

a

p

a

c

i

t

a

n

c

e

s

l

o

p

e

d

e

l

a

y

=

s

l

o

p

e

s

e

n

s

i

t

i

v

i

t

y

×

t

r

a

n

s

i

t

i

o

n

d

e

l

a

y

o

f

i

n

p

u

t

w

a

v

e

f

o

r

m

\large \color{blue} transition \ delay = output \ resistance \times load \ capacitance \\ slope \ delay = slope \ sensitivity \times transition \ delay \ of \ input \ waveform

transition delay=output resistance×load capacitanceslope delay=slope sensitivity×transition delay of input waveform

例如,对于一个反相器来讲:

rising transition delay = rising output resistance × load capacitance

falling transition delay = falling output resistance × load capacitance

rising slope delay = fall slope sensitivity × fall transition delay of input waveform

falling slope delay = rise slope sensitivity × rise transition delay of input wavefor

这里输出电阻(output resistance)被定义为当电压刺激施加到节点上时,电流变化相对于电压变化的导数。在 Synopsys 工具使用的线性模型中,输入和输出引脚的每个组合都有一对单独的上升和下降电阻值。即使对于同一个输出引脚,电阻也可能因哪个输入引脚触发输出转换而不同。同样,intrinsic delay 和 slope sensitivities 也会因不同时序路径的组合而不同。

时序约束

对于时序单元,不仅需要确定延迟,还需要一些时间约束,例如:

- 建立和保持时间(setup and hold times)

- 恢复和撤销时间(recovery and removal times),即在有效时钟边缘前后必须经过的时间量,直到异步信号被停用(例如,复位信号的恢复时间是在时钟关闭之前必须解除异步复位信号的时间量)。

- 最小和最大时钟脉冲宽度

其中最重要的是建立时间。建立时间定义为在有效的锁存时钟边沿到来之前输入信号不再发生变化(已经是期望的输入值)的最小时间要求。

下图是一个上升沿触发的Flip-Flop的建立时间示意图:

对于一个高电平有效的锁存器(Latch)建立时间示意图如下:

保持时间(hold time)是指在时钟有效沿之后,数据输入端信号必须保持稳定的最短时间,确保新数据不会在触发器稳定输出初始数据之前过早到达D端而覆盖其初始数据。

输入电容

功耗计算工具(用于测量动态功耗)和延迟(速度)计算工具都要用到输入电容(Input capacitance)值。电容与电容器两端的电压和积累的电荷有关:

C

=

Q

/

V

=

I

∆

t

/

V

\large \color{blue} C = Q/V = I ∆t/V

C=Q/V=I∆t/V

对于逻辑单元输入引脚的输入电容,可以通过向输入引脚施加激励(0V 到 VDD 上升脉冲或 VDD 到 0V下降脉冲),然后测量流入(或流出)引脚的电荷量来实现。流入引脚的电荷量取决于其他输入和输出的状态。一个精确的模型可能是通过模拟所有可能的情况来提供三种情况,最好的、平均的和最差的。

NLDM与CCS

前面介绍的线性延迟模型在亚微米工艺下就不太准确了,因此目前大多数 lib 库使用更复杂的模型,例如非线性延迟模型(non-linear delay model)。

NLDM

nldm(non linear delay model)是最早引入的单元延时表征技术。在65nm以及之前,一直是一种可靠的迅速得到单元延时的方法。

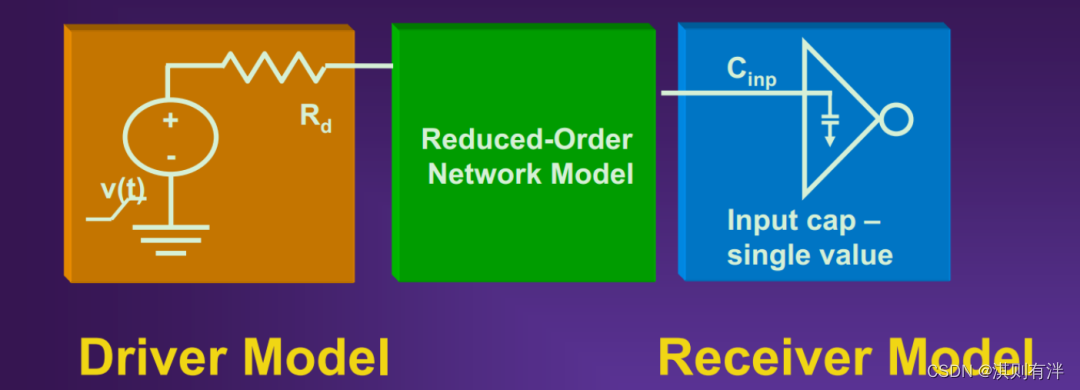

nldm包括 nldm driver model 和 nldm receiver model

nldm 表征的是单元的输入到输出的 delay 值以及输出的 transition time。

对于电压波形,nldm 是通过三个点进行取样。三个点分别为 delay threshold,transition threshold (upper & lower)。一个 delay threshold 指的是电压到 50% VDD的位置。而 transition threshold,取值可能有所不同,有的用的是30% 70%,有的是20% 80% 。如果.lib用的组合不同,工具会自动进行换算。

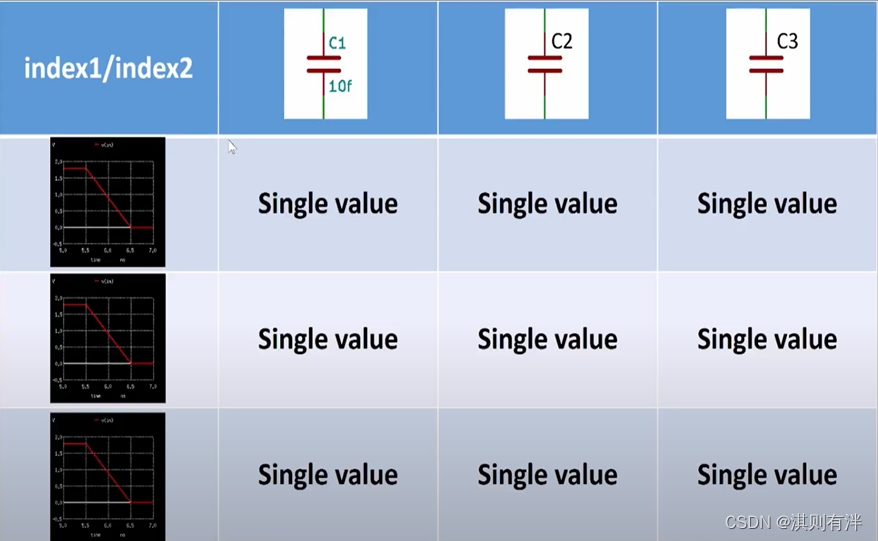

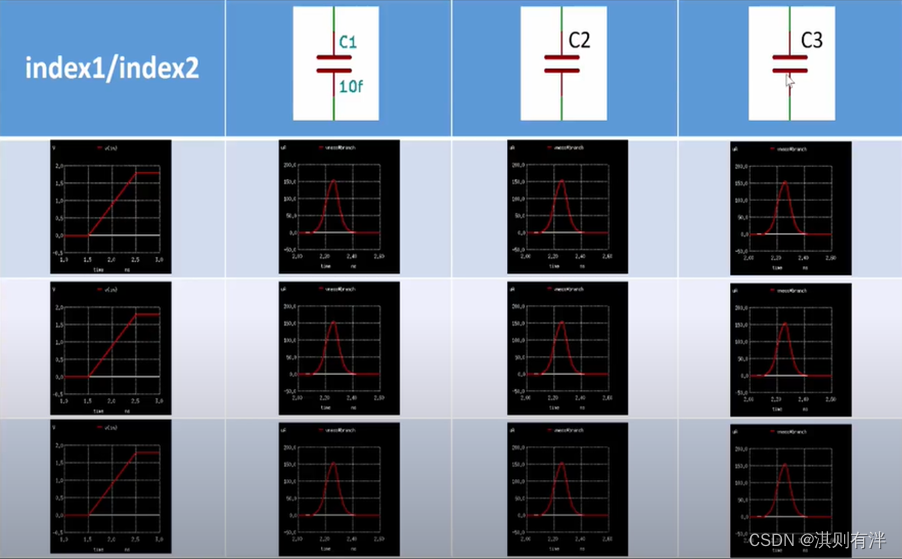

在.lib文件中,nldm 是一个二维查找表。这个查找表的两个 index 分别代表的是 input transition,output load,如图所示。

lib 文件中的延时模型模板:

lu_table_template(delay_template_3x3) {

variable_1 : input_net_transition;

variable_2 :total_output_net_capacitance;

index_1 ("1000, 1001,1002");

index_2 ("1000, 1001,1002");

}/* The input transition and the output capacitance can be in either order,

that is, variable_1 can be the output capacitance.

However, these designations are usually consistent across all templates in a library. */

上面的查找表模板指定表中的第一个行索引变量是input transition time,第二个列索引变量是output capacitance。索引值(1000, 1001, 1002)只是模板,会被实际索引值覆盖。

实际如下:

pin(OUT) {

max_transition : 1.0;

timing() {

related_pin : "INP1";

timing_sense : negative_unate;

cell_rise(delay_template_3x3) {

index_1 ("0.1, 0.3, 0.7");/* Input transition */

index_2 ("0.16, 0.35,1.43"); /* Output capacitance */

values ( /* 0.16 0.35 1.43 */

/* 0.1 */ "0.0513, 0.1537, 0.5280",

/* 0.3 */ "0.1018, 0.2327, 0.6476",

/* 0.7 */ "0.1334, 0.2973, 0.7252");

}

cell_fall(delay_template_3x3) {

index_1 ("0.1, 0.3, 0.7");/* Input transition */

index_2 ("0.16, 0.35,1.43"); /* Output capacitance */

values ( /* 0.16 0.35 1.43 */

/* 0.1 */ "0.0617, 0.1537, 0.5280",

/* 0.3 */ "0.0918, 0.2027, 0.5676",

/* 0.7 */ "0.1034, 0.2273, 0.6452");

}

在65nm之前,NLDM相对准确。但是随着工艺尺寸的减少。NLDM 模型暴露出如下缺点:

- 仅通过3个输出点来评估延时,线性度不够精确;

- NLDM 的 driver model 是个内阻恒定的电压源,即输出电压是时间的线性函数V(t),当65nm节点以下时,驱动线网的电阻将大得可观,模型会失真。

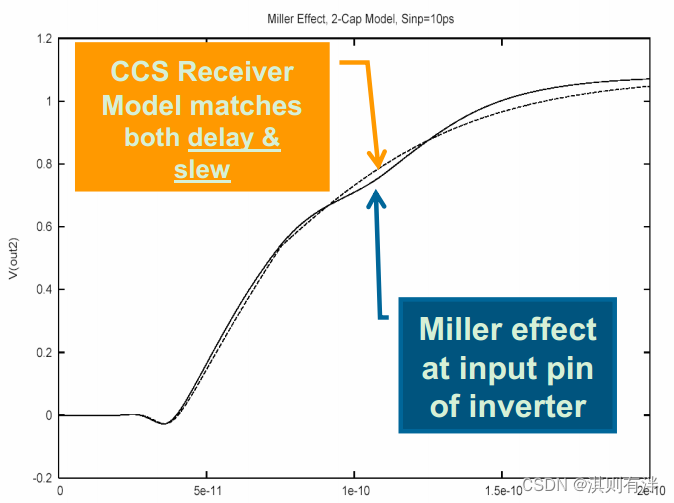

- NLDM 的 receiver model 是单一的 input cap,不能捕获 Miller 效应,对于很小的阻抗网络,Miller 效应决定了延迟。

CCS

CCS(composite current source)model 很好的解决了NLDM存在的这些问题。

同样,CCS也包括了 CCS driver model 和 CCS receiver model。

CCS deiver model 表征的是流入 load cap 的电流值。其参数同样是输入的 transiton time 以及输出的load。

CCS描述的是一个内部无限的电流源,因此,即使net的电阻非常大的情况,它也可以非常精确。

在.lib中,对应于不用的 input transition 以及 output load,表中的值也不再是一个定值,而是电流的波形。

为了更精确的反应 miller 电容效应。model 中用两个电容 C1 和 C2 来进行描述。在 receiver 的电压波形到达 delay thereshold(50% vdd)之前时,用 C1 的值,而在到达 delay threshold 之后,则采用 C2 值。

与 spice 相比的拟合精度:

从精度上来说,NLDM模型跟SPICE模型的误差在正负5%左右,而CCS模型跟SPICE模型的误差能达到正负2%。

为了提供准确的电流矢量模型,CCS会存储波形,且每个波形存储10个电流值和10个时间值,共20个数字。NLDM对于每个输入转换和输出负载存储2个数字。因此,与NLDM模型相比,CCS模型大小将增加10倍。

CCS lib/db 里,可以同时含 timing/power/noise 信息。CCS lib 里会看到有 ccsn_first_stage /ccsn_last_stage group,分别是最前/后级管子受 noise 的影响。

STA基础

静态时序分析(Static Timing Analysis,STA)是验证数字集成电路时序是否合格的一种方法。在综合工具(DC/Genus 等)、布局布线工具(ICC2/Innovus 等)、时序分析工具(PrimeTime/Tempus 等)中都嵌入了不同的STA引擎,这些引擎往往在时间和精度方面有一些折衷,但是目的就是以尽量小的误差去模拟物理器件和绕线的SPICE模型,从而更接近芯片生产出来后真实的性能。

为什么需要STA呢,目前的芯片晶体管已经上亿了,如果用 spice 仿真的话计算量非常巨大,仿真时间难以忍受。STA 与时序仿真相比有以下优点:

- 第一点是激励波形,STA是不需要的激励波形的,但是需要 SDC(Synopsys Design Constraint,时序约束),而时序仿真时严重依赖激励波形;

- 第二点是完整度,STA能够对数字电路中所有的时序路径进行全面的检查,而时序仿真在覆盖率上有一定限制;

- 第三点是效率,STA比较简单,速度更快,而生成仿真需要的激励,建立仿真环境可能费时费力;

- 第四点是鲁棒性,STA能够考虑到电路中串扰噪声以及OCV(On Chip Violation,片上偏差)的影响,提高芯片制成后的良率,而时序仿真做不到这一点。

当然STA也有局限性:

- STA针对的是数字电路,和模拟电路相关的路径无法通过STA验证

- 数字电路中产生的不定态在STA不会验证,这个需要通过仿真进行仔细检查确认

- 电路中不同状态机之间的同步需求不能通过STA来验证

- 对时钟生成电路的验证无法通过STA完成

- 时序约束中会有例外情况,需要人工处理

参考:

https://blog.csdn.net/u011075954/article/details/121229023

https://blog.csdn.net/graymount/article/details/106010388

https://blog.csdn.net/u011075954/article/details/121229023