目录

1. MUX2to1

2. MUX3to1

3. MUX4to1

作为写过很多代码的程序员应该知道什么是函数的调用,例如下面的代码中,main函数调用了add函数对两个数值进行相加的操作:

int add(int a, int b) {

return a + b;

}

int main() {

int a = 1, b = 2;

int sum = add(a, b);

}

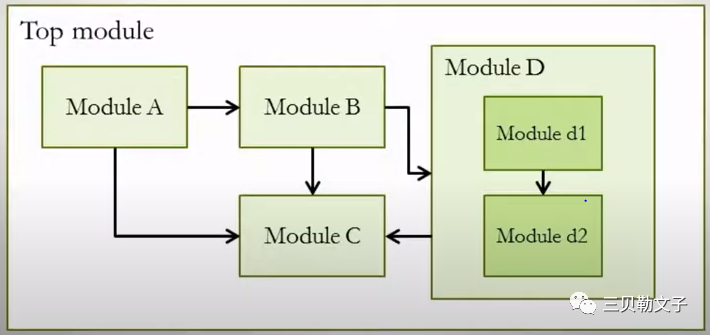

其实,在编写verilog的过程中也有类似的操作,叫做module的调用,在整个verilog工程中有一个主要的module,叫做top module,top module可以调用其他的子module,关系图如下:

module的调用语法有两种方法:

By name: module类型 module名称(.PortA(WireA), .PortB(WireB), ...);

In Order: module类型 module名称(WireA, WireB, ...)

假设我们已经定义了一个MUX2to1的module:

1. MUX2to1

module mux2to1(a, b, c, sel);

input [2:0] a;

input [2:0] b;

input sel;

output [2:0] c;

reg c;

always@(a or b or sel)

begin

if(sel)

c = a;

else

c = b;

end

endmodule

2. MUX3to1

module mux3to1(a,b,c,sel1,sel2, outputdata);

input [2:0] a;

input [2:0] b;

input [2:0] c;

input sel1;

input sel2;

output [2:0] outdata;

wire[2:0] data;

MUX2to1 mux21_dut1(

.a(a),

.b(b),

.c(data),

.sel(sel1)

);

MUX2to1 mux21_dut2(

.a(data),

.b(b),

.c(outdata),

.sel(sel2)

);

endmodule

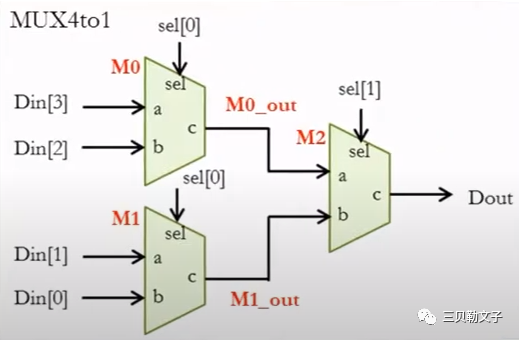

3. MUX4to1

module MUX4to1(Din, sel, Dout);

input [3:0]Din;

input [1:0]sel;

output Dout;

wire M0_out, M1_out;

MUX2to1 M0(.a(Din[3]),

.b(Din[2]),

.sel(sel[0]),

.c(M0_out)

);

MUX2to1 M1(.a(Din[1]),

.b(Din[0]),

.sel(sel[0]),

.c(M1_out)

);

MUX2to1 M2(.a(M0_out),

.b(M1_out),

.sel(sel[1]),

.c(Dout)

);

endmodule