2 ZYNQ PL开发

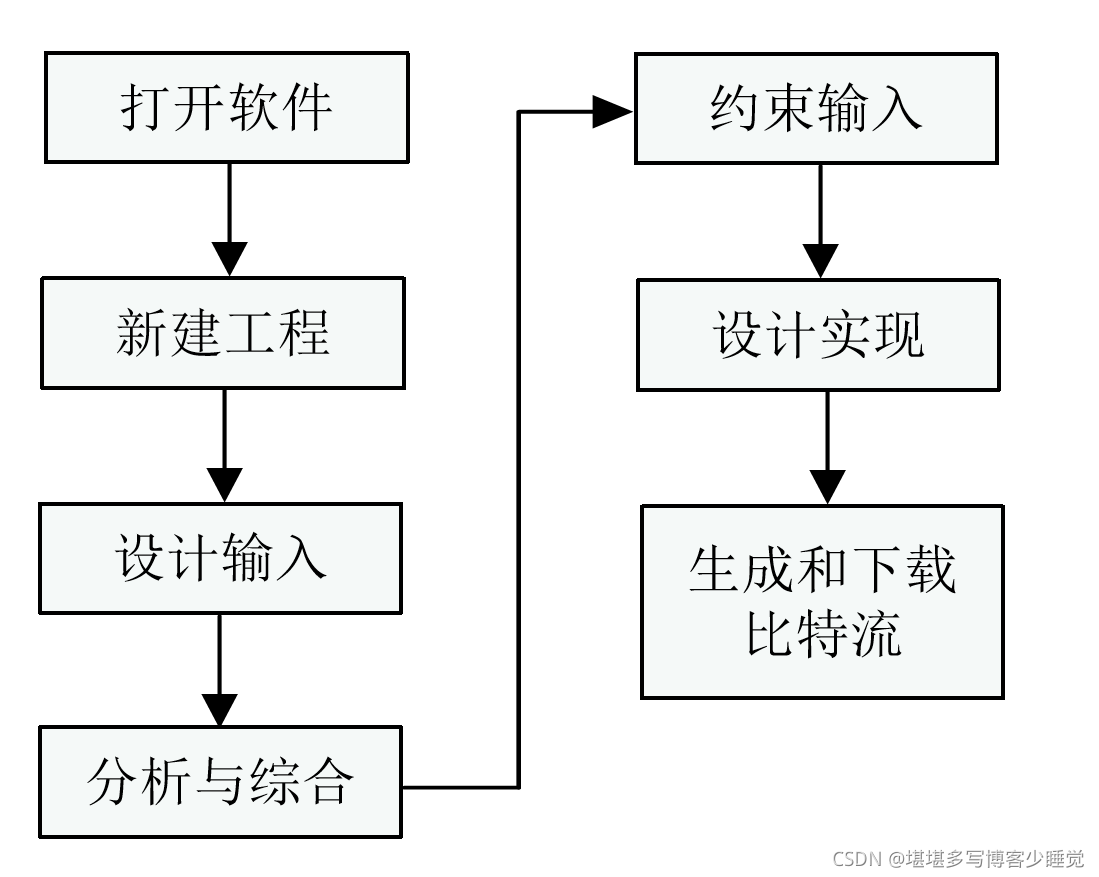

开发流程

开发使用vivado,流程如下

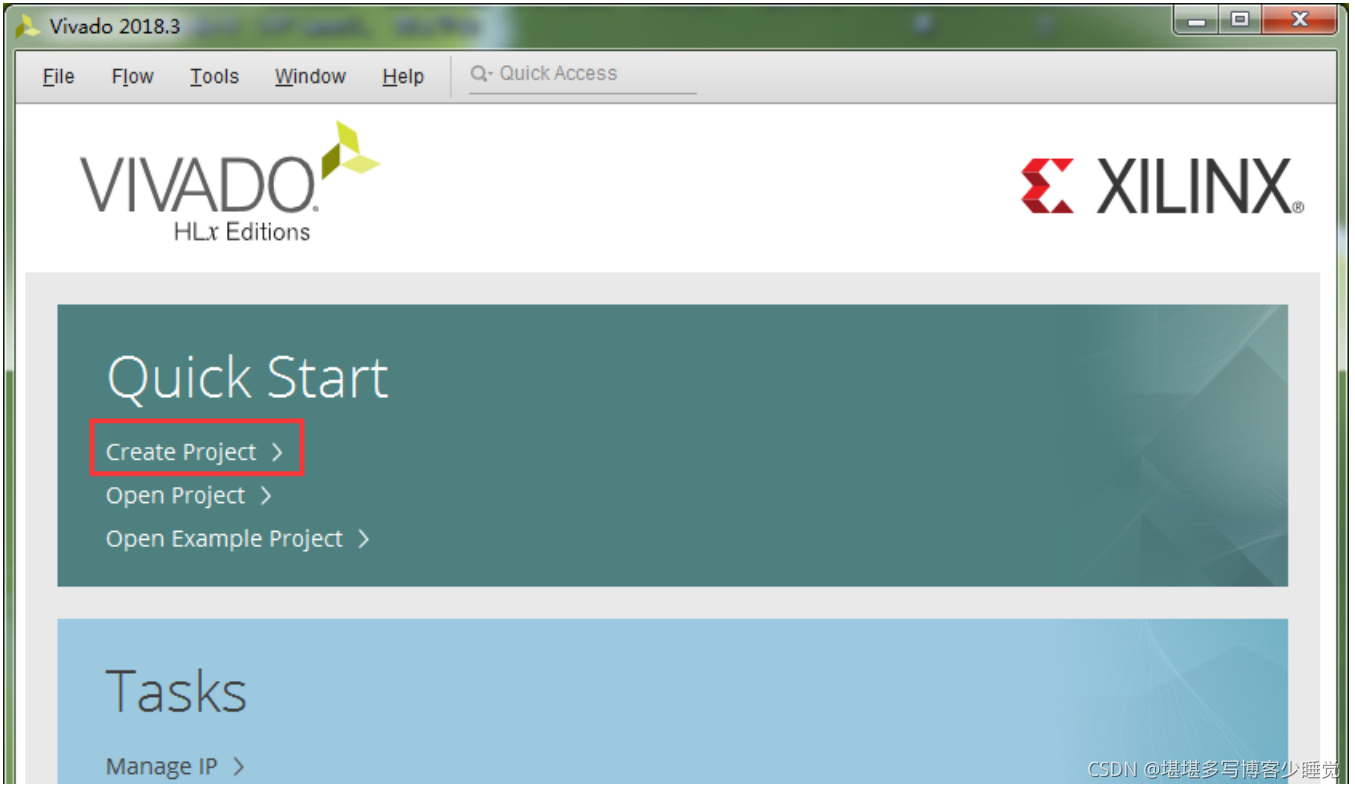

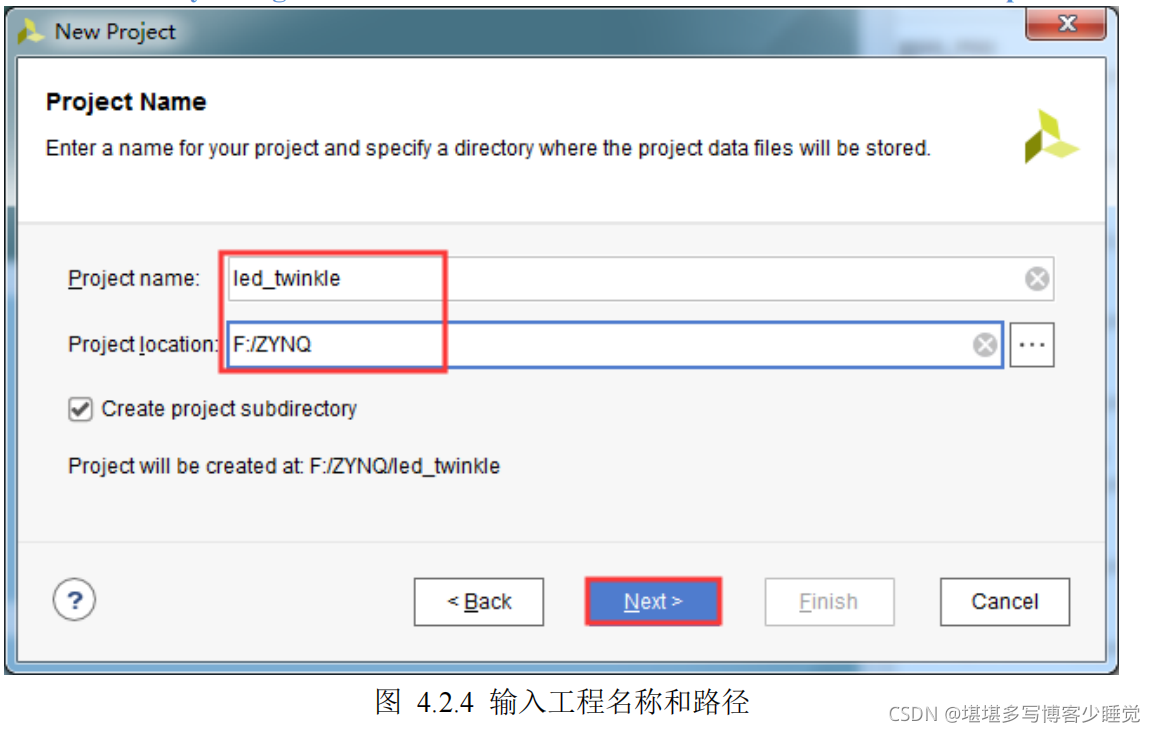

1.新建工程

工程项目含义

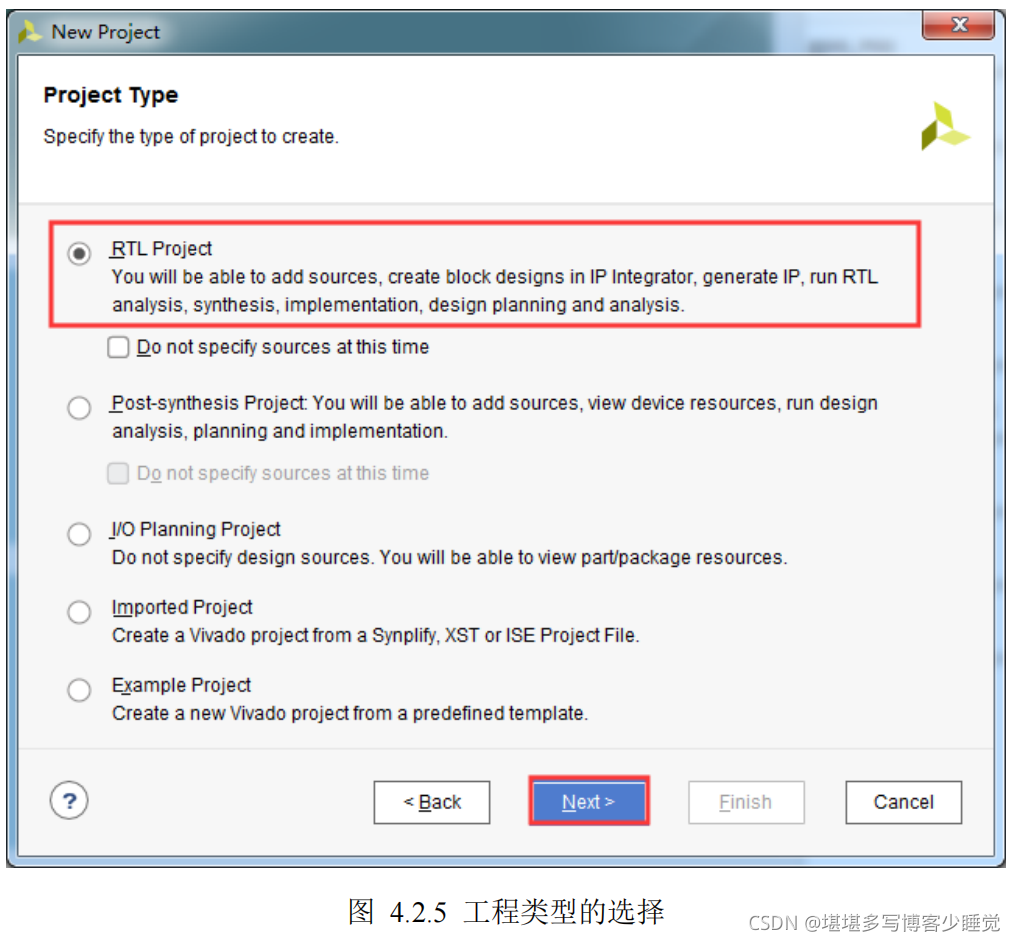

这里简单介绍下各个工程类型的含义。“RTL Project”是指按照正常设计流程所选择的类型,这也是常用的一种类型

“RTL Project”下的“Do not specify sources at this time”用于设置是否在创建工程向导的过程中添加设计文件,如果勾选后,则不创建或者添加设计文件;

“Post-synthesis Project”在导入第三方工具所产生的综合后网表时才选择;

“I/O Planning Project”一般用于在开始 RTL 设计之前,创建一个用于早期IO 规划和器件开发的空工程;

“Imported Project” 用于从 ISE、XST 或 Synopsys Synplify 导入现有的工程源文件;

“Example Project”是指创建一个 Vivado 提供的工程模板。

这个可以加也可以跳过

这个可以加也可以跳过

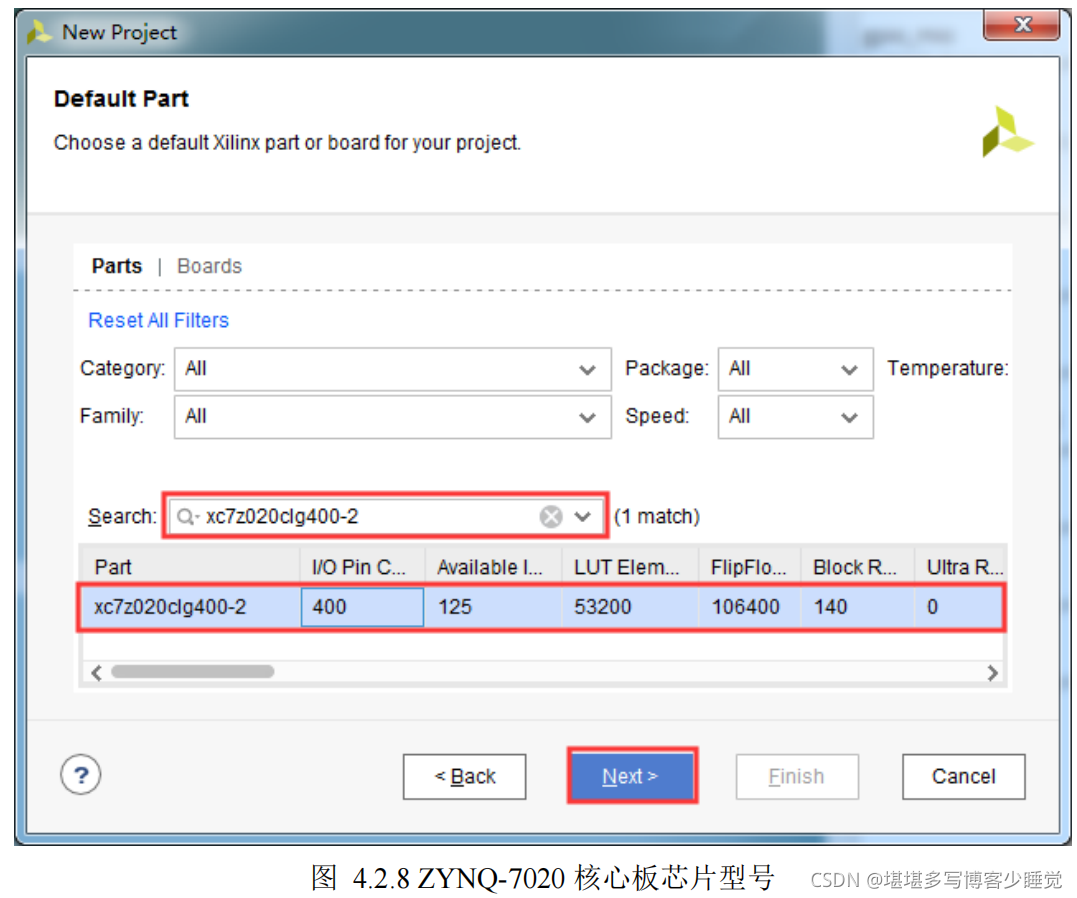

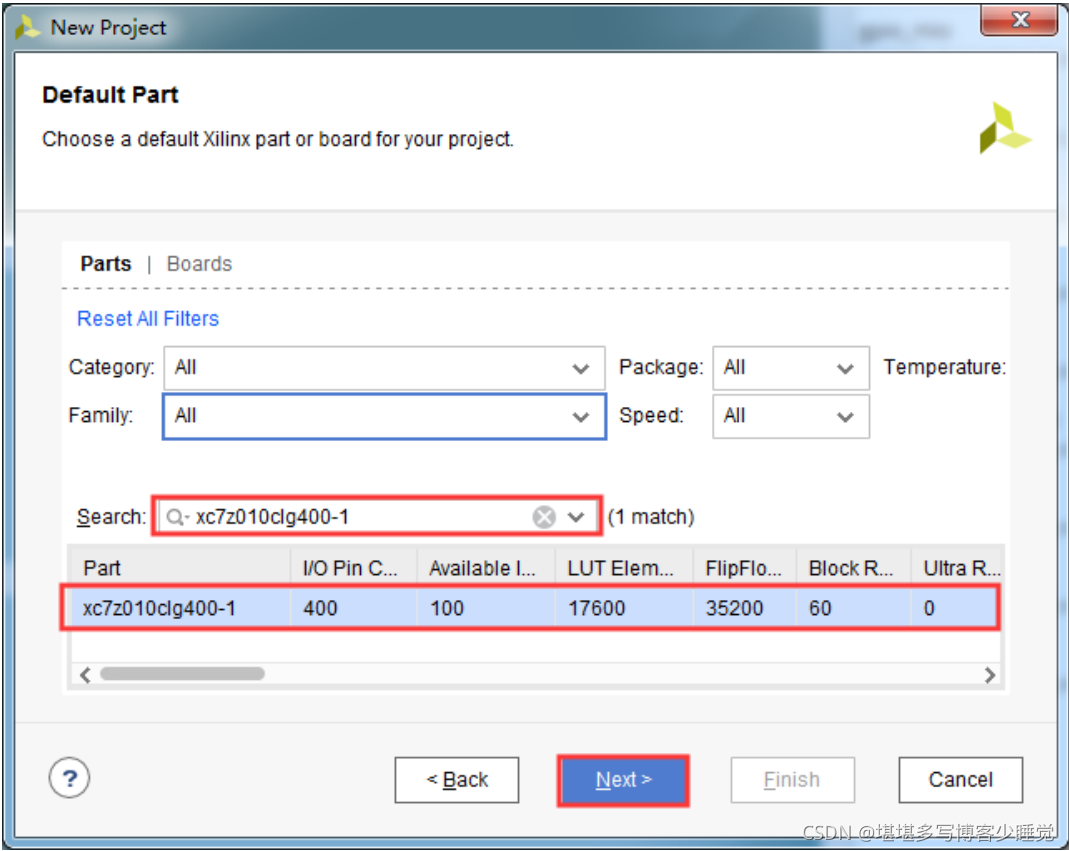

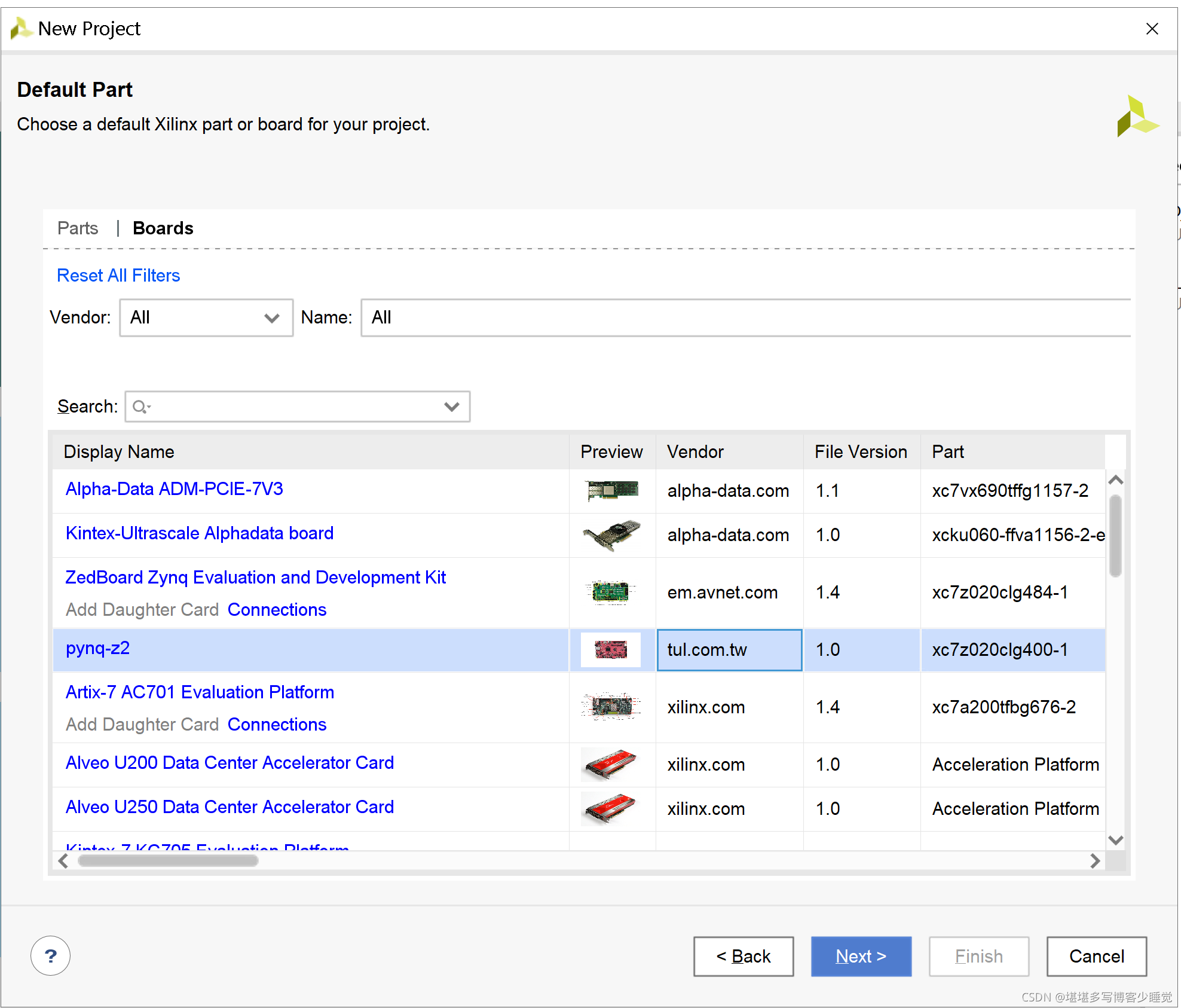

对应型号选择板卡,我用的是pynq-z2,直接选择xilink集成好的板卡

如何添加pynq-z2板文件看这一篇博客

如何添加PYNQ-Z2板文件到Vivado

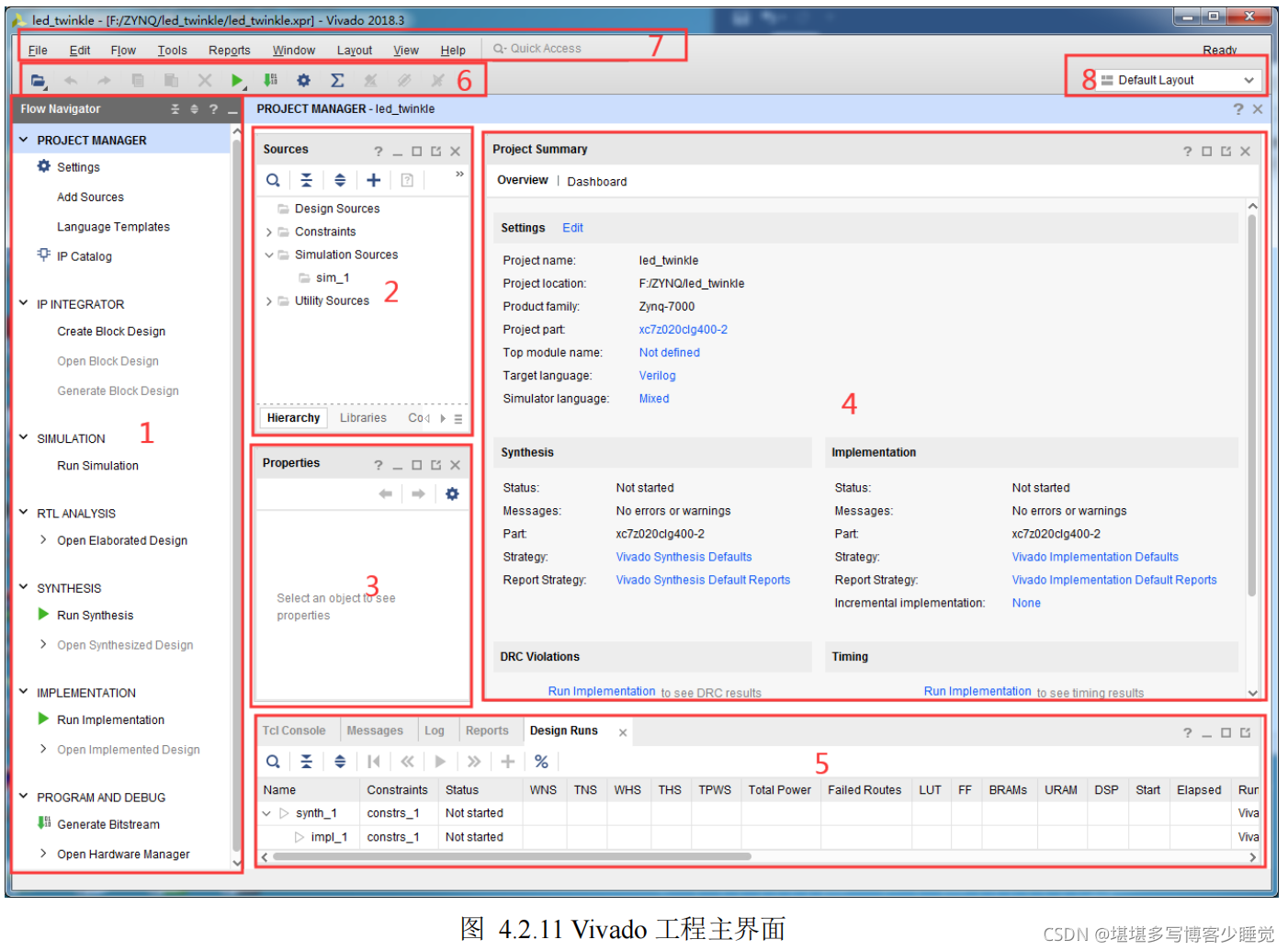

(1)Flow Navigator。Flow Navigator 提供对命令和工具的访问,其包含从设计输入到生成比特流的整个过程。 在点击了相应的命令时,整个 Vivado 工程主界面的各个子窗口可能会作出相应的更改。

(2)数据窗口区域。默认情况下,Vivado IDE 的这个区域显示的是设计源文件和数据相关的信息。

• Sources 窗口:显示层次结构(Hierarchy)、IP 源文件(IP Sources)、库(Libraries)和编译顺序(Compile Order)的视图。

• Netlist 窗口:提供分析后的(elaborated)或综合后的(synthesized)逻辑设计的分层视图。

(3)Properties 窗口:显示有关所选逻辑对象或器件资源的特性信息。

(4)工作空间(Workspace):工作区显示了具有图形界面的窗口和需要更多屏幕空间的窗口,包括:

• Project Summary。提供了当前工程的摘要信息,它在运行设计命令时动态地更新。

• 用于显示和编辑基于文本的文件和报告的 Text Editor。

• 原理图(Schematic)窗口。

• 器件(Device)窗口。

• 封装(Package)窗口。

(5)结果窗口区域:在 Vivado IDE 中所运行的命令的状态和结果,显示在结果窗口区域中,这是一组子窗口的集合。在运行命令、生成消息、创建日志文件和报告文件时,相关信息将显示在此区域。默认情况下,此区域包括以下窗口:

• Tcl Console:允许您输入 Tcl 命令,并查看以前的命令和输出的历史记录

• Messages:显示当前设计的所有消息,按进程和严重性分类,包括“Error”、“Critical Warning”、“Warning”等等

• Log:显示由综合、实现和仿真 run 创建的日志文件。

• Reports:提供对整个设计流程中的活动 run 所生成的报告的快速访问。

• Designs Runs:管理当前工程的 runs。

(6)主工具栏:主工具栏提供了对 Vivado IDE 中最常用命令的单击访问。

(7)主菜单:主菜单栏提供对 Vivado IDE 命令的访问。

(8)窗口布局(Layout)选择器:Vivado IDE 提供预定义的窗口布局,以方便设计过程中的各种任务。

布局选择器使您能够轻松地更改窗口布局。或者,可以使用菜单栏中的“Layout”菜单来更改窗口布局。

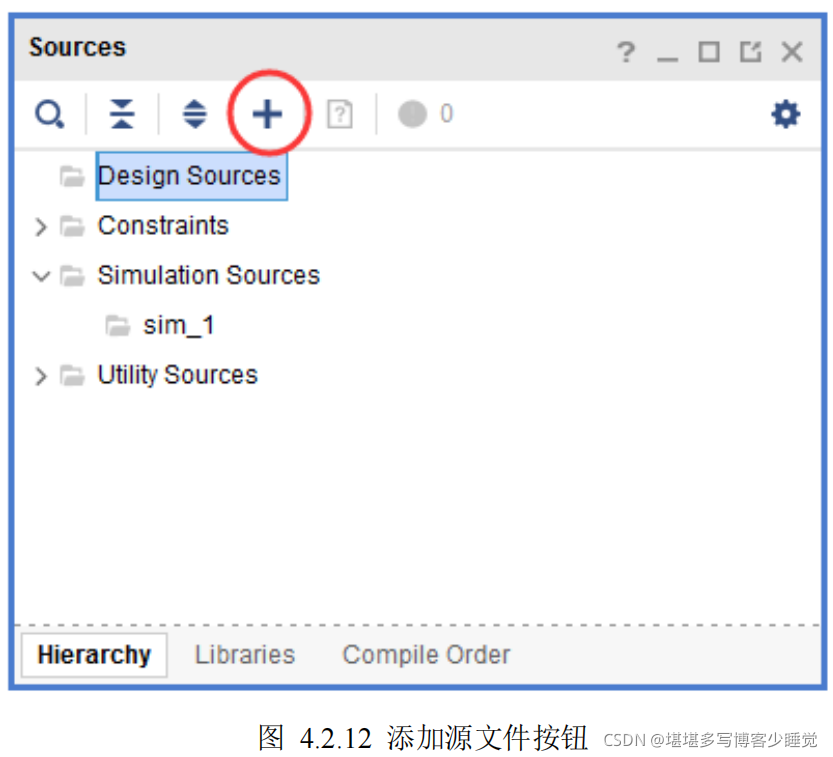

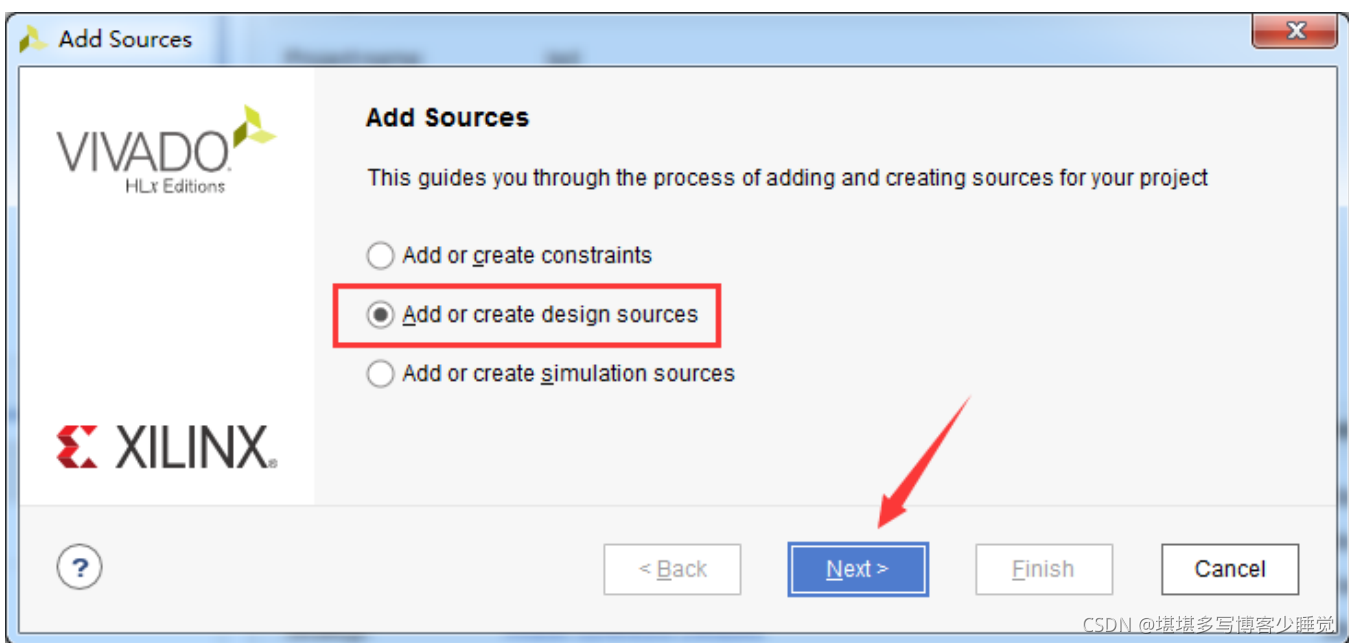

2设计输入

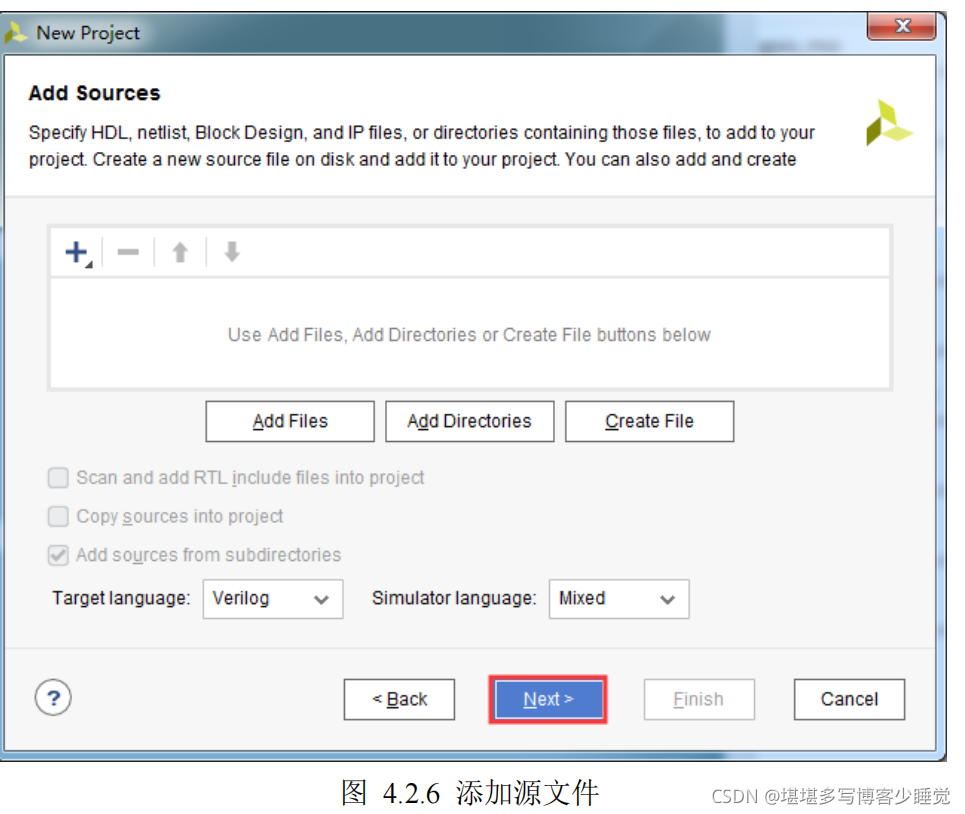

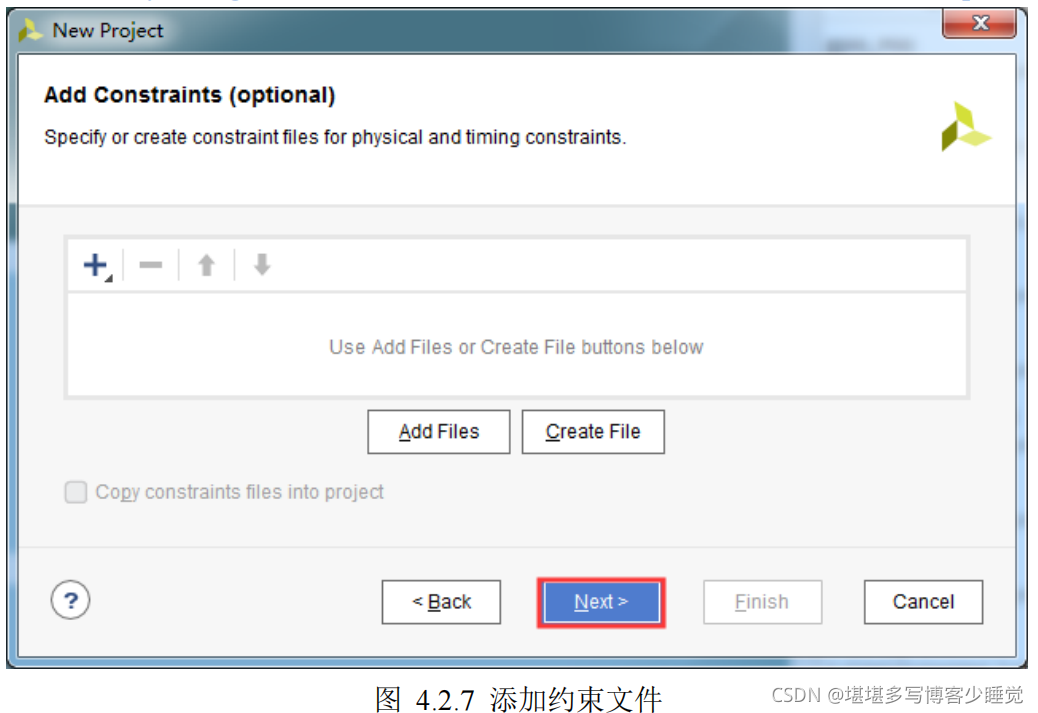

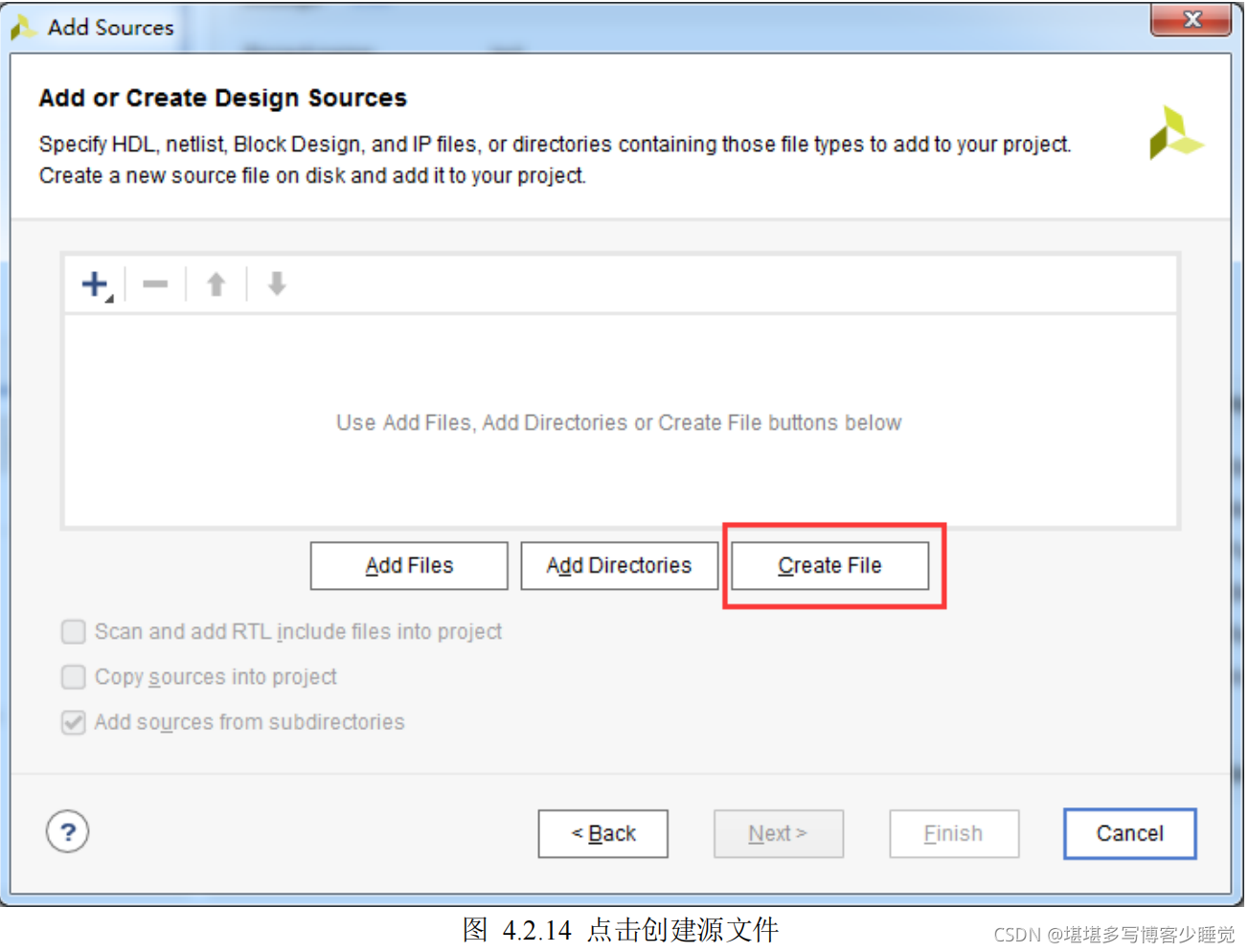

如果事先有编写好的代码,可以点击“Add Files”按

钮来添加文件;如果没有,则点击“Create File”创建一个新的设计文件。由于我们事先没有编写好的设计

文件,这里点击“Create File”来创建一个新的设计文件,如下图所示:

输入点灯代码

module led_twinkle( 2 input sys_clk , //系统时钟

input sys_rst_n, //系统复位,低电平有效

output [1:0] led //LED 灯 6 );

//reg define

reg [25:0] cnt ;

//*****************************************************

//** main code

//*****************************************************

//对计数器的值进行判断,以输出 LED 的状态

assign led = (cnt < 26'd2500_0000) ? 2'b01 : 2'b10 ;

//计数器在 0~5000_000 之间进行计数

always @ (posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

cnt <= 26'd0;

else if(cnt < 26'd5000_0000)

cnt <= cnt + 1'b1;

else

cnt <= 26'd0;

end

endmodule

3.分析和综合

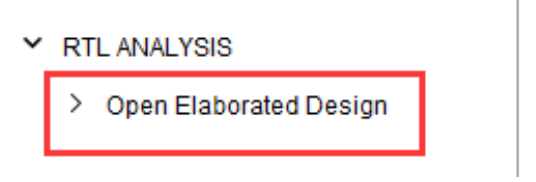

分析

代码输入完毕之后,就可以对设计进行分析(Elaborated)了。点击“Flow Navigator”窗口中的“Open Elaborated Design”按钮

此时,Vivado 会编译 RTL 源文件并进行全面的语法检查,并在 Messages 窗口中给出相应的“Error”和“Warning”。如果出现“Error”,则分析失败,用户必须修改设计文件,并重新编译源文件来取消“Error”。如果出现“Warning”,用户也可逐一查看,以确定哪些是设计缺陷,哪些是可以忽略的。打开分析后(Elaborated)的设计,Vivado 会生成顶层原理图视图,并在默认 view layout 中显示设计

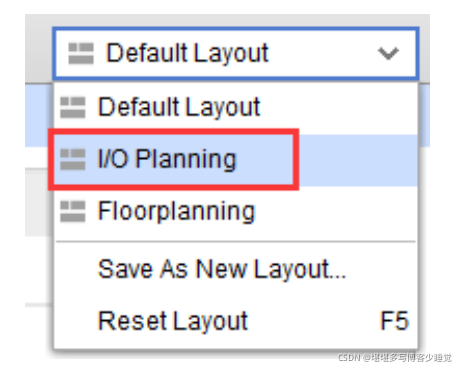

引脚分配

此时,窗口布局会打开 IO 相关的子窗口,在下方的“I/O Ports”窗口中,就可以进行 IO 的分配了。这里我们暂时不分配,先对设计进行综合,综合之后再统一输入时序约束和 IO 引脚的物理约束

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-lEIHaZWM-1630417069784)(C:\Users\Liu Junyong\AppData\Roaming\Typora\typora-user-images\image-20210830225421225.png)]](https://img-blog.csdnimg.cn/3a24d07f845240f7a61f3ffa1ce9e00d.png?x-oss-process=image/watermark,type_ZHJvaWRzYW5zZmFsbGJhY2s,shadow_50,text_Q1NETiBA5aCq5aCq5aSa5YaZ5Y2a5a6i5bCR552h6KeJ,size_20,color_FFFFFF,t_70,g_se,x_16)

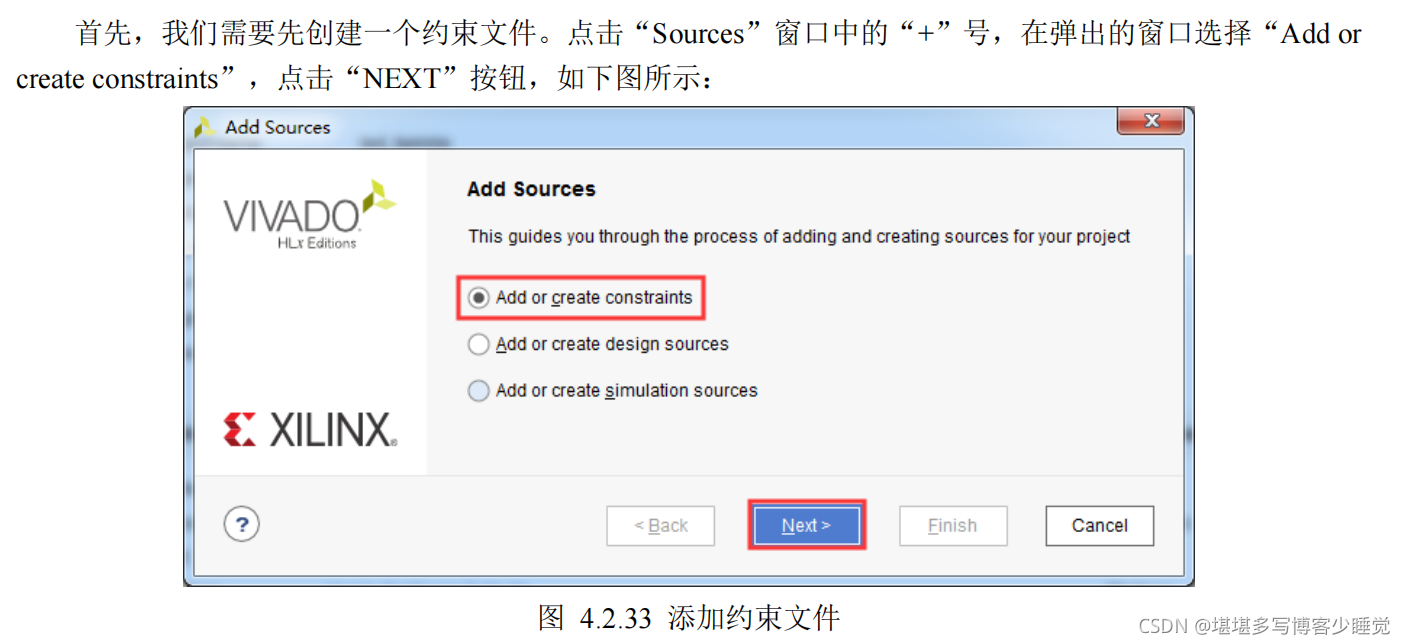

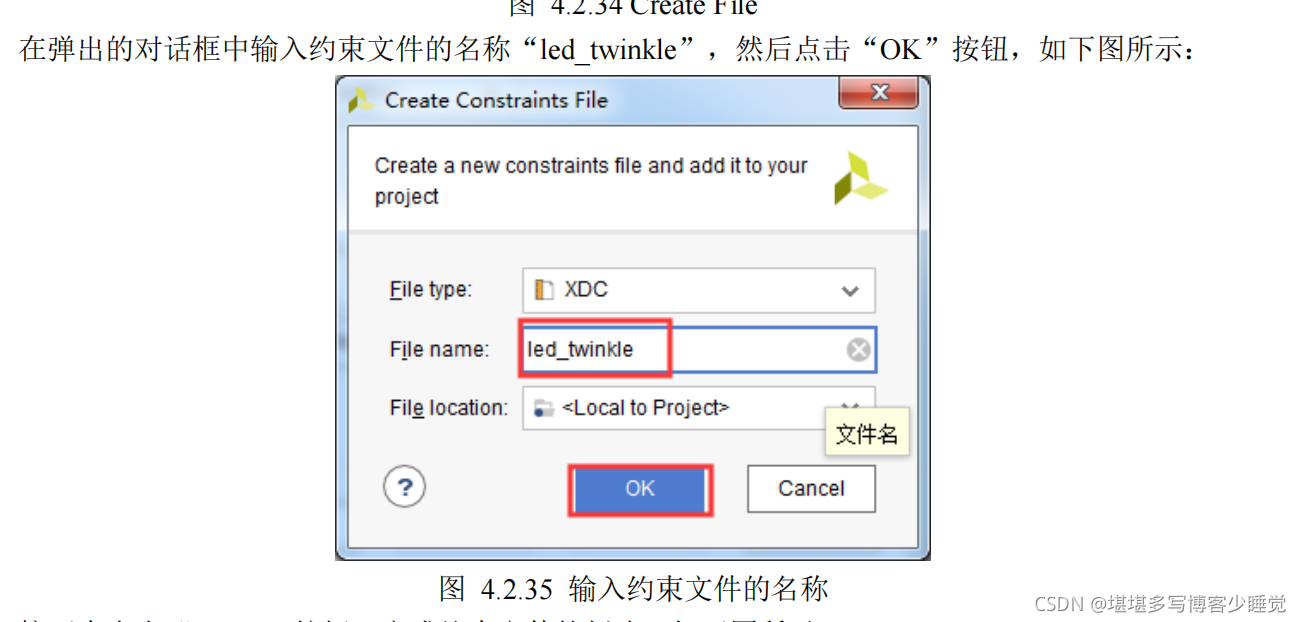

4.约束输入

#IO 管脚约束

set_property -dict {PACKAGE_PIN U18 IOSTANDARD LVCMOS33} [get_ports sys_clk]

set_property -dict {PACKAGE_PIN J15 IOSTANDARD LVCMOS33} [get_ports sys_rst_n]

set_property -dict {PACKAGE_PIN J18 IOSTANDARD LVCMOS33} [get_ports {led[0]}]

set_property -dict {PACKAGE_PIN H18 IOSTANDARD LVCMOS33} [get_ports {led[1]}]

第一行以“#”号开头,表示这是一条注释语句,每一条注释也单独占用一行。第二行是有效的约束命令,每一个约束命令单独占用一行,命令的结尾不需要像 verilog 代码一样,添加分号“;”结束符号。命令的第一个关键字代表该命令的名称,其后的所有字段都是该命令的参数列表。IO 管脚约束是对端口的引脚位置和电平标准进行约束,例如第二行命令是对系统时钟的管脚进行约束,“set_property”是命令的名称;“PACKAGE_PIN U18”是引脚位置参数,代表引脚位置是 U18;“[get_ports sys_clk]”代表该约束所要附加的对象是 sys_clk 引脚;“IOSTANDARD LVCMOS33”代表该引脚所使用的电平标准是 LVCMOS33。 IO管脚约束比较好理解,就是我们的程序所驱动的IO和ZYNQ芯片的IO对应起来。而时序约束(Timing Constraints)用来描述设计人员对时序的要求,比如时钟频率,输入输出的延时等,以满足设计的时序要求。

约束语句如下:

#时钟周期约束

create_clock -name clk -period 20 [get_ports sys_clk ]

“create_clock”是该命令的名称,它会创建一个时钟;其后的“-name clk”、“-period 20”、“[get_ports sys_clk ]”都是该命令的各个参数,分别表示所创建时钟的名称是“clk”、时钟周期是 20ns、时钟源是 sys_clk 端口,一般只对输入的时钟做周期的约束。对时钟的约束最简单的理解就是,设计者需要告诉 EDA 工具设计中所使用的时钟的频率是多少;然后工具才能按照所要求的时钟频率去优化布局布线,使设计能够在要求的时钟频率下正常工作。本次实验sys_clk 的时钟频率为 50MHz,周期为 20ns,在做约束时可以等于这个值或者略低于这个值,不建议周期设置的太小,否则软件在布局布线时很难满足这个要求。其实对于比较简单的设计,可以不对工程做时序约束,即使不进行时序约束,也不影响最终的功能。 而当设计变得复杂起来,或者输入的时钟频率比较高的时候,如果不添加时序约束,那么就有可能在验证设计结果的时候出现一些意料之外的情况。

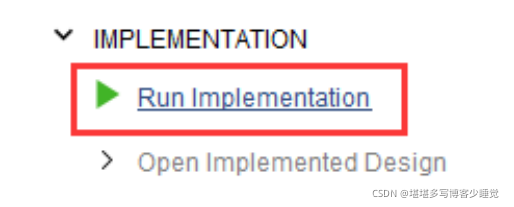

5.设计实现

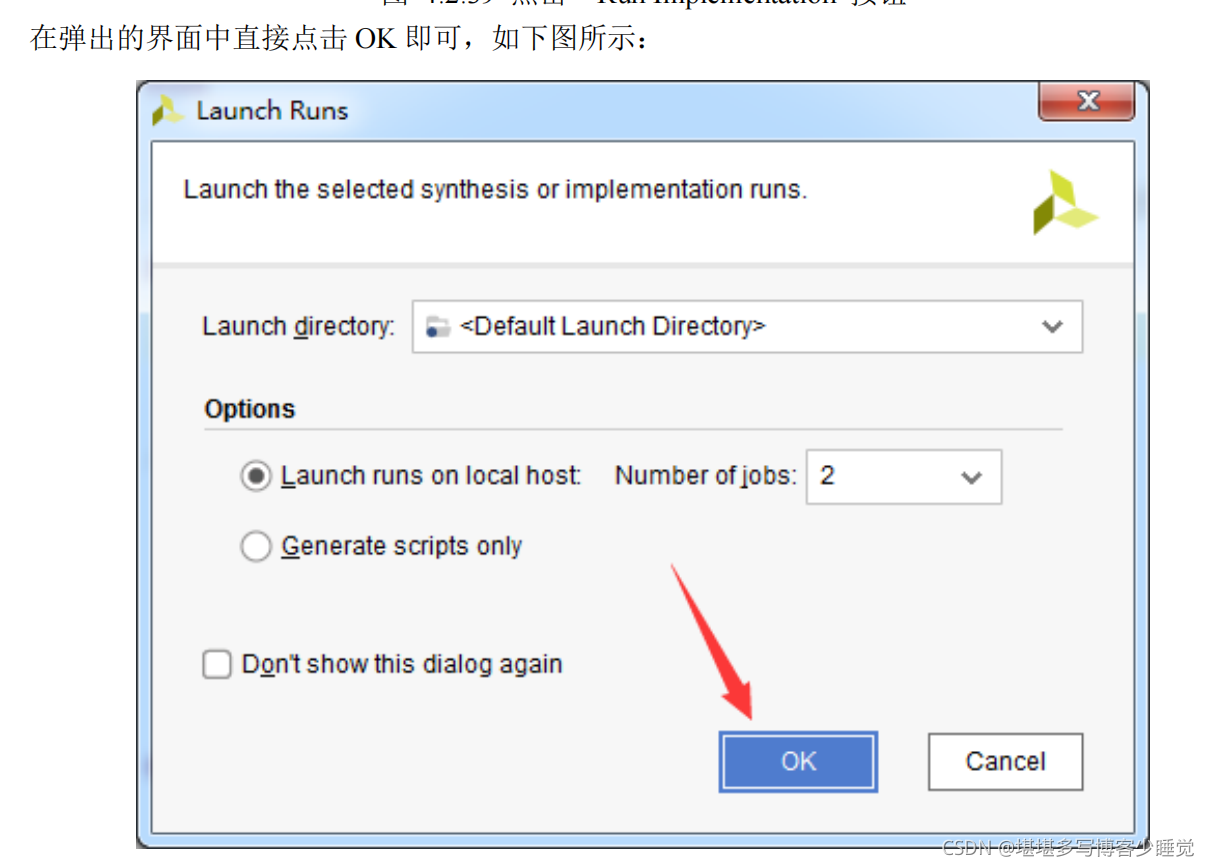

约束输入完毕之后,就可以开始实现设计了。我们点击“Flow Navigator”窗口中的“Run Implementation”按钮,如下图所示

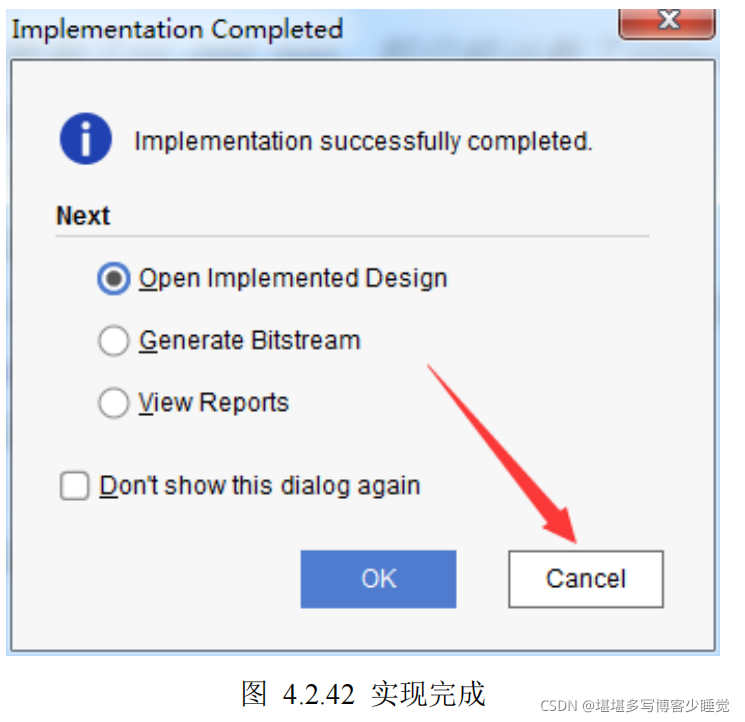

实现完成后会弹出提示窗口,我们直接点击取消来关闭窗口,如下图所示:

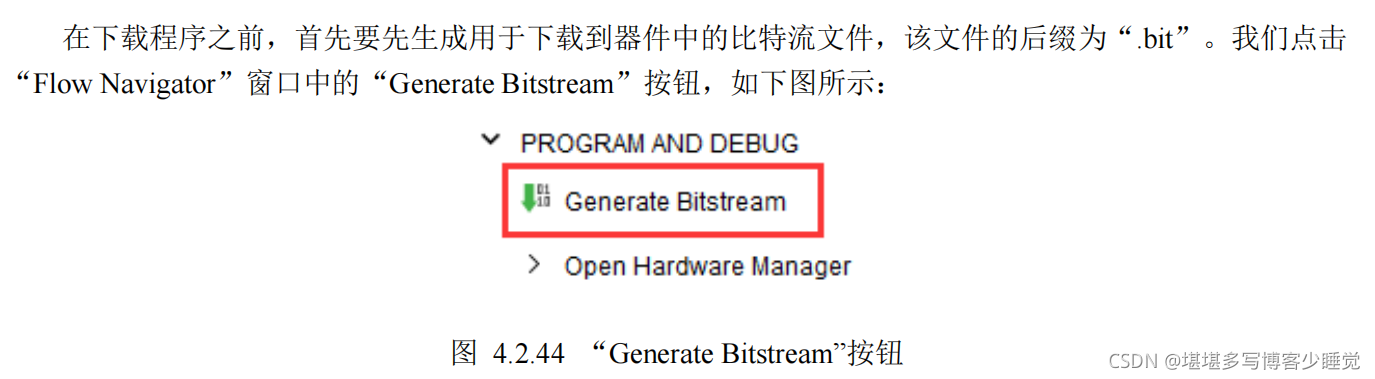

6.下载bit流

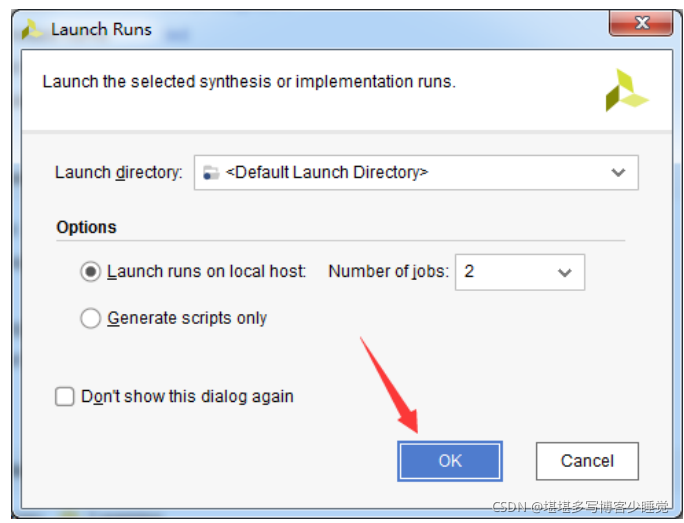

在弹出的窗口中直接点击 OK

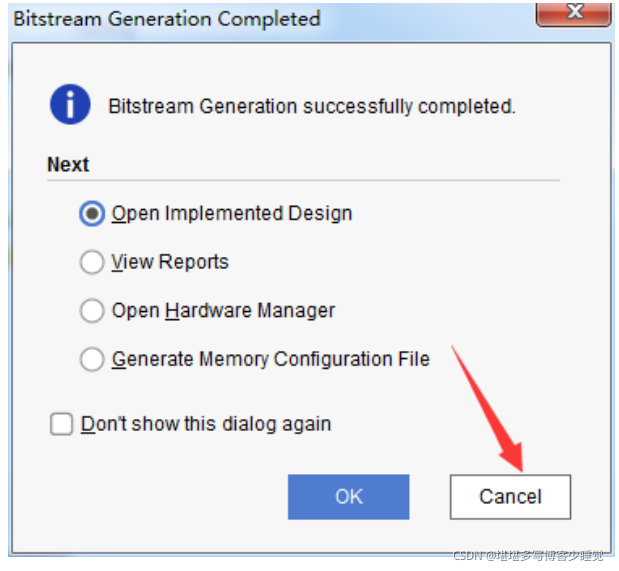

比特流生成完毕之后,Vivado 会弹出提示窗口,我们点击取消关闭该窗口:

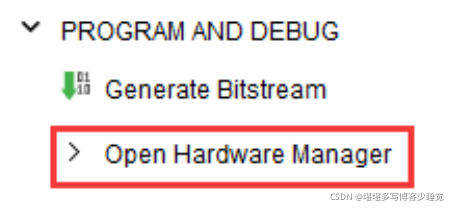

接下来我们开始下载比特流,点击“Flow Navigator”窗口中的“Open Hardware Manager”按钮,如下

图所示:

开发板完成并打开电源开关后,点击“Hardware”子窗口中的“Auto Connect”按钮,如下图所示:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-kRRR1oJ9-1630417069789)(C:\Users\Liu Junyong\AppData\Roaming\Typora\typora-user-images\image-20210830230137360.png)]](https://img-blog.csdnimg.cn/fbe062031b494f5c9c715032b71b5738.png?x-oss-process=image/watermark,type_ZHJvaWRzYW5zZmFsbGJhY2s,shadow_50,text_Q1NETiBA5aCq5aCq5aSa5YaZ5Y2a5a6i5bCR552h6KeJ,size_12,color_FFFFFF,t_70,g_se,x_16)

需要说明的是,下载完比特流后,如果开发板断电,程序会丢失。如果想要程序断电不丢失的话,需要将程序固化至开发板中,这个需要在嵌入式 SDK 软件中完成,ZYNQ 芯片无法单独固化比特流文件(PL的配置文件)**。这是由于 ZYNQ 非易失性存储器的引脚(如 SD 卡、QSPI Flash)是 ZYNQ PS 部分的专用引脚,这些非易失性存储器由 PS 的 ARM 处理器进行驱动,需要将 bit 流文件和 elf 文件(软件程序的下载文件)合成一个 BOOT.BIN,才能进行固化,因此需要学习 ZYNQ 嵌入式 SDK 的开发流程。硬件调试和仿真下节再说。