Chisel时序电路(三)——Chisel移位寄存器(Shift Register)详解

上一篇文章介绍了Chisel计数器以及一些高级用法,内容很多,学下来肯定收获也会很多。除了计数器以外,还有一种寄存器的应用十分广泛,那就是移位寄存器。这一篇文章就详细介绍移位寄存器和Chisel中的移位寄存器,还会囊括并行输出、并行加载的移位寄存器。

移位寄存器

移位寄存器是顺序连接的一组触发器,每个寄存器(触发器)的输出都作为下一个寄存器的输入。下图就是一个4级移位寄存器的示意图:

移位寄存器电路会在每个时钟tick将数据从左到右移动,那么上面示意图中的4级移位寄存器电路就实现了从din到dout的四拍的延时输出。需要注意的是,上面的示意图中使用了四个寄存器,但其实实现中等价于一个移位寄存器,后面两种移位寄存器也是如此。

下面的Chisel代码就实现了一个移位寄存器:

val shiftReg = Reg(UInt(4.W))

shiftReg := Cat(shiftReg(2, 0), din)

val dout = shiftReg(3)

这个代码需要解释一下,它做了这么些事:

- 创建了一个4位的寄存器

shiftReg;

- 将移位寄存器的低3位和输入

din用Cat拼接起来,作为寄存器的下一个输入;

- 寄存器的值的最高有效位(Most Significant Bit,MSB)作为

dout输出。

还是很好理解的。移位寄存器通常用于将串行数据转换为并行数据或将并行数据转换为串行数据,下面的两个小节就分别介绍这两种移位寄存器。

并行输出移位寄存器

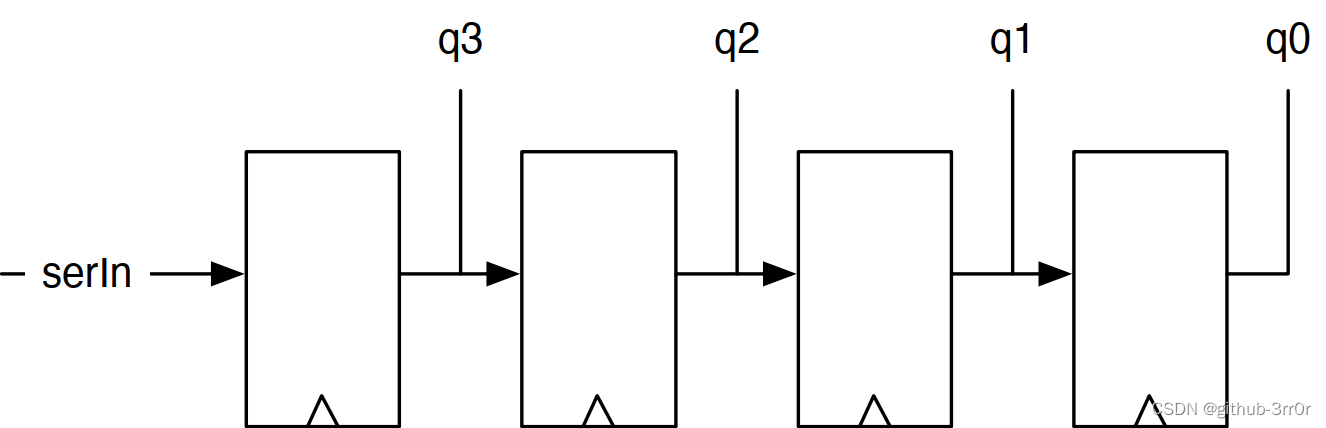

串行输入并行输出配置的移位寄存器可以将一个串行的输入流转换为并行的字,这种移位寄存器可能用于串口(UART)的接收功能。下图就是个4位的并行输出移位寄存器,它的每个触发器的输出都连接到一个单比特输出:

在四个时钟周期后,电路会将一个4位的串行数据字转换成一个4位的并行数据字q。在这个例子中,我们假设第0位(最低位)首先输入因此在读取完整的字的时候它是到达了最后一个寄存器的。下面的代码就实现了这样一个4位并行输出的移位寄存器:

val outReg = RegInit(0.U(4.W))

outReg := Cat(serIn, outReg(3, 1))

val q = outReg

这个移位寄存器outReg初始化为0,然后我们从MSB开始移入,也就是寄存器值右移,4个周期后,并行输出的结果q就寄存器outReg的值。

并行输入移位寄存器

并行输入串行输出配置的移位寄存器可以将一个并行的输入字(字节)流转换为一个串行的输出流,这种移位寄存器可能用于串口(UART)的发送功能。下图就是一个4位并行输入的移位寄存器的示意图:

可以看到,每个移位寄存器的输入都有一个Mux来选择加载哪个数据,如果load信号被设置,那就加载d,否则加载0或上一个寄存器的值,也就是移位,简单地说就是load有效时加载,load无效时移位输出。用Chisel代码实现如下:

val loadReg = RegInit(0.U(4.W))

when(load) {

loadReg := d

} .otherwise {

loadReg := Cat(0.U, loadReg(3, 1))

}

val serOut = loadReg(0)

注意看otherwise语句块中的Cat调用,在移位的时候最高有效位会填充0,被移出的最低有效位则作为输出连接到serOut上。

结语

这一篇文章介绍了移位寄存器的实现和两种常用的移位寄存器,在实现串口通信的时候会很有用,对后面的高速接口设计可能又会有一定启发。寄存器相关的内容到这里就结束了,不过在数字设计中,不仅仅有寄存器可以保存电路的状态信号,内存(Memory)也是可以保存状态信息的,在处理器设计中内存还用于程序代码和数据的存放,因此十足重要。下一篇文章我们将会用较长的篇幅详细讲述Chisel中的内存实现,敬请期待。