本文介绍下DDR3的管脚分配,其它系列的DDR管脚分配也基本一样的。FPGA型号:10AX027H4F34I3SG,DDR3型号:MT41J128M16JT-125,QuartusI Prime18.0

首先介绍下A10器件能支持的DDR系列以及速率,A10上的DDR控制器是硬核的,现在能支持到DDR4,2400Mbps。逻辑侧具体支持系列和速率见下表

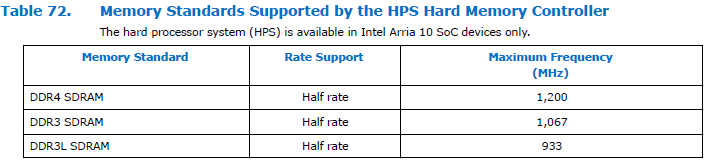

HPS侧DDR的运行速率见下表。

注:表里的Rate Support 有Quarter rate 和Half Rate两种,这个意思是指用户逻辑侧的时钟频率跟存储器器件侧的时钟频率的关系,比如memory侧运行的时钟频率是1200MHz,如果选择Quarter rate 那么逻辑侧的时钟频率是300Mhz,如果选择Half Rate则逻辑侧的时钟频率是600Mhz。另由于存储器的带宽是不变的,你选择不同Rate Support,则控制器到逻辑侧的数据总线位宽会跟着同步变化以达到同样的数据带宽。Ping Pong PHY是指允许两片外接存储器分时复用同一组地址/命令总线,相比于独立的使用地址/命令接口,这样可以使用更少的管脚。

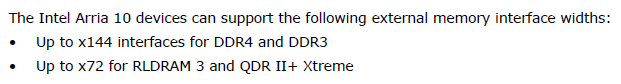

A10上外接存储器的最大接口位宽,DDR4/DDR3可以达到144位宽。

2、A10上外接存储器接口的结构

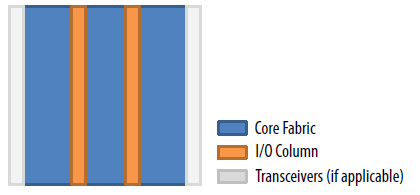

首先了解下A10上外接存储器接口的结构:I/O Subsystem,I/O Subsystem由两个或三个I/O column组成。

I/O column在A10的pin planner上的位置及其结构如下

每个I/O column主要是由I/O Bank 和IO-AUX两部分组成的。不同器件系列,不同封装,每个I/O column包含的I/O Bank个数是不一样的。每个I/O column最多可以包含13个I/O Bank。在A10的下面简单介绍下这两个模块。

I/O AUX

每个I/O column有一个I/O AUX,

(1)有一个hard Nios II processor

功能:对sequencer进行配置和开始校准任务

收集和处理数据

用校准运算的结果的来配置I/O

(2)对整个I/O column进行校准算法运算

(3)可以通过Avalon接口与每个I/O bank的的sequencer进行通信以实现校准控制。

I/O Bank

每个 I/O Bank又由下面的几个部分组成

(1)Embedded Hard Controller

每个bank包含一个嵌入式硬核控制器,当使用了多个bank的接口来拼接高位宽时,只有其中一个bank的控制器是使用的,其余bank的控制器是关掉的以节约功耗。

(2)Hard Sequencer

通过校准接口从而对接口传输延迟引起的建立保持时间的变化进行补偿,以使得高频率时钟操作正常。

(3)Dedicated DLL

(4)Interger PLL

(5)OCT calibration block

(6)PHY clock network

(7) Four I/O lanes

**每个I/O Bank上 有4个I/O lanes,每个I/O lanes有12个I/O pins。每个I/O lane都可以实现一个x8/x9的DQS group。其中2个管脚来做DQS和DQS#,其余10个管脚可以作为DQ和DM管脚。

3、DDR管脚分配规则

(1) A/C 地址/命令线

1) 所有的地址/命令接口必须放在同一个Bank 里

2) 地址/命令接口不能跟数据管脚放在同一个lane里(12 pins)

3)地址/命令接口可以跟数据放在同一个bank

(2)DQ pins 数据管脚

1)两个不同的DQS组,DQ管脚不能放在同一个I/O lane里

(3)DQS pins 数据选通管脚

1)x8/x9组里,跟DQ管脚对应的DQS,DM管脚必须放在同一个I/O lane里

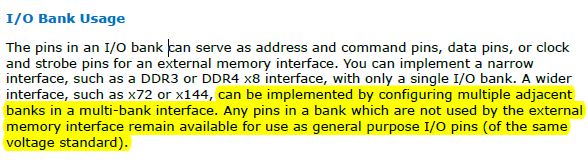

(4)I/Obank里没有用到的IO Pins可以当作同电平的GPIO使用

4、管脚分配实践

由于FPGA里对DDR的管脚分配有一定的限制,比如要求DQ,DQS,DM在一个组,地址,命令在某些bank等,所以,最好使用Quartusii 软件进行管脚自动分配,分配完成后,如果不满意,再进行局部调整。

一、先建一个工程,列化一个DDR3的IP,生成example

1.双击打开DDR3_IP进行参数设置。

2.修改列化IP名字为ddr3_ip, 单击OK按钮。

3.接着就是进行参数的配置了,我之前文章有详细列出参数配置选项注解,这里主要说下这个MEMORY运行时钟 与输入PLL的参考时钟的关系,从下图可以看到默认是memory时钟频率1066.667Mhz。输入的DDR_IP 锁相环的参考时钟是266.667M。

如果你的DDR3想跑其它的频率,比如修改为800Mhz, 那下面的PLL参考时钟就会可选择,你从下拉列表中选择一个外部的参考时钟输入,这里有多个时钟频率可供选择,为了保证性能和抖动,推荐选择频率值较大的时钟为输入。另外,有些人想不用该外部时钟,直接用FPGA内部锁相环输出一个时钟给DDR3_IP, 这种方法由于是内部PLL产生,抖动会较大,如果DDR3想跑高频率,这种方法是不推荐使用的。

4.为了简化设置,可以从下图的右下角选择你所使用的DDR3的型号,如果没有,可以选择一个相近的,apply后, 再进行修改。 这里我选择DDR3-1600K CL11128Mbx16,然后点击Apply,这样 参数就设置完成了。

5.接着点击Generate Example Design ,生成example.经过几十s等待完成example的生成,然后点击finish。 生成example 一是可以用该工程进行管脚分配,不用再重新自己建工程,二是,板子回来后,可以先用该example 进行接口测试。

6.完成example生成后,回到Quartusii 主界面,打开刚生成的example 工程, File->Open, 选择qpf格式文件 ,打开

7.接着 如果不需要指定DDR3管脚分配的bank, 那直接全编译工程即可。如果需要指定bank,则可以先综合,综合后,在Pin Planner 里设置管脚的bank,然后再全编译。一般,为了保证DDR3管脚没问题,直接全编译,用软件给的参考管脚即可。

8.下图就是全编译后,在pin planner里看到的管脚分配情况,Fitter Location 这一列就是分配的管脚,我们只需在Location 这一列 把同行的管脚Copy过来就行,另I/O Standard 这一列已经自动把管脚的电平约束好了,不需要再用tcl script进行管脚电平约束。

9.把所有的管脚在Location 列 分配好后, 再进行一次全编译,如果通过则表明DDR的管脚分配没问题。如果你是手段分配管脚,那最后也要进行全编译,只有 全编译 通过,才表明你们的DDR管脚分配没有问题。下面是分配管脚后,全编译过的管脚分配情况。

10.由于用的example工程,所有,里边还有一些DDR3管脚以外的信号,用来测试DDR3的校准以及数据读写是否OK的。如果有板子话,可以把该工程下载到板子上,然后进行测试,可以看硬件是否OK。

Tips

1.为了提高带宽,通常喜欢将多片DDR并联使用。目前A10上一个DDR3_IP,理论最多可以外接144位宽的数据总线,但实际推荐最多使用72位宽数据线。

2.在分配DDR管脚的bank,剩下的其它管脚 可以用作通用I/O使用,只是电平必须跟DDR使用的电平一样。

3.Arria10 上用的EMI IP 不需要再运行pin_assignments .tcl脚本就进行管脚电平约束。其在全编译时会自动进行管脚电平约束。