目录

一、常见名词

1.1 时钟偏移Skew

1.1.1 Skew出现的原因

1.1.2 Skew解决方法

1.2 抖动Jitter

1.2.1 Jitter出现的原因

1.2.2 时钟抖动永远存在

1.3 扇入扇出Fan-in/Fan-out

1.4 亚稳态及相关概念

1.4.1 建立时间(Setup time)

1.4.2 保持时间(Hold time)

1.4.3 setup和hold违例的危害

1.4.4 setup和hold约束关系

1.4.5 实例分析

1.4.6 复位时间(recovery)

1.4.7 撤销时间(removal)

异步复位,同步释放:

1.5 时间裕量Slack

1.5.1 概念

关键路径(critical path):

到达时间(arrival time):

需求时间(required time):

时间裕量(slack):

1.5.2 数据到达时间(Data Arrival Time)

1.5.3 时钟到达时间(Clock Arrival Time)

1.5.4 数据建立需求时间(Data Required Time Setup)

1.5.5 数据保持需求时间(Data Required Time Hold)

1.5.6 计算Slack

一、常见名词

1.1 时钟偏移Skew

1.1.1 Skew出现的原因

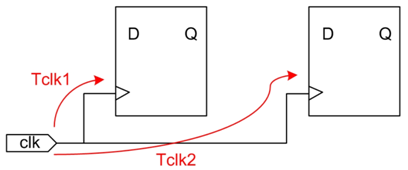

因时钟线长度不同或负载不同,导致时钟到达相邻单元的时间不同,这个时间上的偏差就叫时钟偏移SKEW。

在上图中的Tskew=Tclk2-Tclk1

1.1.2 Skew解决方法

偏移会一直存在

Skew 问题的解决方法就是:设计中的主要信号应该走全局时钟网络。

此外FPGA中延迟锁定环(Delay locked ring,DLL)也可以去SKEW,延迟锁相环由控制逻辑和延时线组成,控制逻辑将输入时钟与输出时钟进行比较,并插入延时从而使得时钟同步。

但无论如何,在STA时,仍然要考虑Skew。

1.2 抖动Jitter

1.2.1 Jitter出现的原因

在理想情况下,一个频率固定的完美的脉冲信号(以1MHz为例)的持续时间应该恰好是1us,每500ns有一个跳变沿。但这种信号并不存在。如图所示,信号周期的长度总会有一定变化,从而导致下一个沿的到来时间不确定。这种不确定就是抖动(jitter)。

1.2.2 时钟抖动永远存在

1.3 扇入扇出Fan-in/Fan-out

数字电路中,逻辑门相互连接,每个逻辑门输出端与输入端都连着大量别的单元,因此由扇入扇出表示处理外部输入以及驱动外部其他单元的能力。

1.4 亚稳态及相关概念

同步电路中:

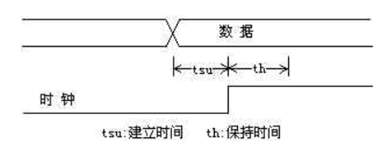

1.4.1 建立时间(Setup time)

触发器时钟上升沿到来前数据保持稳定的时间。

1.4.2 保持时间(Hold time)

触发器时钟上升沿到来后数保持据稳定的时间。

1.4.3 setup和hold违例的危害

如上图所示,在时钟上升沿到来前后的一段时间内数据必须保持稳定,否则数据就无法写入,造成“亚稳态“输出。如果前级驱动够强劲,电路就能按照趋势变化下去,一定时间后该点的值就会变化为“正确值”,如果驱动不够强劲,电路就会恢复之前的值,最终得到何值是不可控的,所以我们要避免亚稳态。在使用DFF时,必须满足其建立时间和保持时间的要求。

1.4.4 setup和hold约束关系

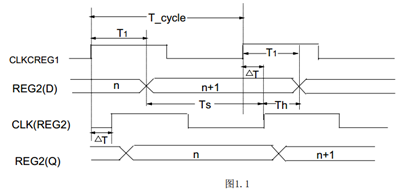

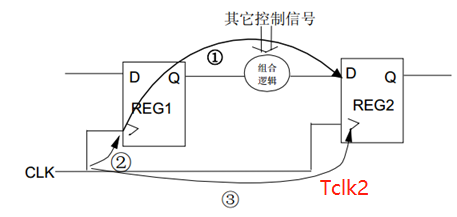

以上图为例,假设时序如下

在上图时序中:

△T = Tskew

T1 = REG1检测到时钟后内部延时(Tclk_q) + 组合逻辑延时最后到达REG2的时间(Tcomb)

Tcycle = CLK的周期(Tclk)

Tsu=数据在CLK2上升沿到达前维持的时间

Tsu = Tcycle + Tskew - T1

Th=数据在CLK上升沿到达后维持的时间

Th = T1 – Tskew

如果Ts>setup time(触发器),Th>hold time(触发器)则数据能正常写入,由这个条件可以看出,Tskew与T1起着关键作用,而正之前所说如果使用全局时钟则Tskew会很小,可以忽略不计。

1.4.5 实例分析

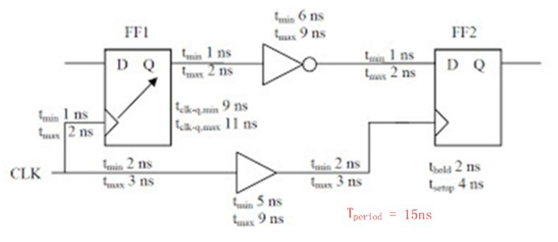

以上图为例

Tsu= Tcycle + Tskew-T1 要使Tsu最小,则Tskew最小,T1最大。

Tsu(min) = Tcycle + Tskew(min) - T1(max) = Tcycle(=15) + Tskew(min)(=2+5+2-2) - T1(max) (=11+2+9+2) = 15+2+5+2-2-11-2-9-2 = 22- 24 < Tsetup

因此发生了setup violation

异步复位时:

除了同步电路中会产生亚稳态外(不满足Tsu和Th),在异步复位时也会产生亚稳态,这里需要提到复位时间与撤销时间。

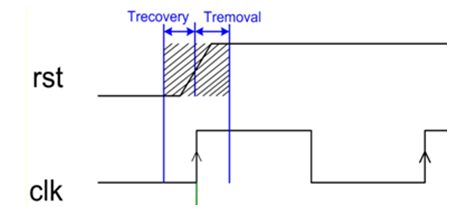

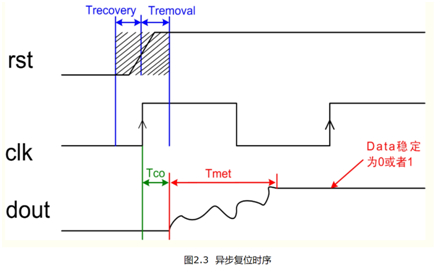

1.4.6 复位时间(recovery)

复位信号释放(对于低电平有效的复位信号指上升沿),与紧跟其后的第一个时钟上升沿之间的最小时间。

1.4.7 撤销时间(removal)

时钟信号的上升沿,与紧跟其后异步复位信号从有效到无效的最小时间。

如下图所示,异步复位信号撤销必须在复位时间和撤销时间外,否则会产生亚稳态。

异步复位信号撤销时间在Trecovery和Tremoval之内,则会造成亚稳态,在时钟上升沿Tco(输出延时)后会产生振荡,振荡时间为Tmet(决断时间)。

补充:

1.只要系统中有异步元件,亚稳态就是无法避免的,亚稳态主要发生在异步信号检测、跨时钟域信号传输中。

2.对于同步信号而言不满足Tsu和Th会产生亚稳态,对于异步信号,复位不满足Trecovery和Tremoval会产生亚稳态。

3.随着clk频率的增加,亚稳态发生的几率是增加的。

消除亚稳态方法:

1.对异步信号进行同步处理;

2.使用FIFO对跨时钟域数据进行缓冲处理;

3.复位电路采用异步复位,同步释放处理;

异步复位,同步释放:

为了避免亚稳态,让拉高的复位信号打两拍,达到与时钟clk边沿同步的目的

module asyn_reset(

clk,

rst_n,

rst_s2

);

input clk;//时钟

input rst_n;//异步的复位信号

output reg rst_s2;//同步释放的复位信号

reg rst_s1;//中间寄存1拍

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) begin

rst_s1 <= 1'b0;

rst_s2 <= 1'b0;//异步复位:复位信号有效:没有打拍

end

else begin

rst_s1 <= 1'b1 ;

rst_s2 <= rst_s1;//同步释放:clk边沿触发:打了两拍

end

end

endmodule

异步复位,同步释放的电路原理图

仿真代码

`timescale 1ns/100ps

module tb_asyn_reset();

reg clk;//时钟

reg rst_n;//异步的复位信号

wire rst_s2;//同步释放的复位信号

asyn_reset my_asyn_reset(clk,rst_n,rst_s2);

always #5 clk = ~clk;

initial begin

clk = 0;

rst_n = 1;

#3;

rst_n = 0;

#2.5;

rst_n = 1;

#100;

$stop;

end

endmodule

1.5 时间裕量Slack

1.5.1 概念

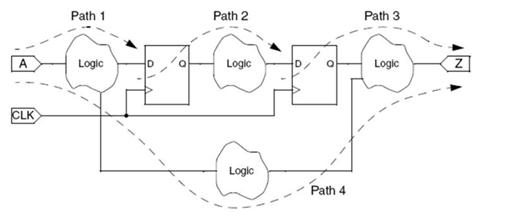

时间裕量分析 首先需要将电路中的路径找出来。

路径的起点有两种:时序器件的时钟输入端、电路的起点;

终点也有两种:时序器件的数据输入端、电路的终点。

如下图所示,一共有四种路径。

除了路径外还有以下几个概念需要了解:

关键路径(critical path):

从输入到输出中延时最大的那条路径。

到达时间(arrival time):

信号从参考的时间起到达某特点位置的时间。

需求时间(required time):

信号到达的最晚的时间。

时间裕量(slack):

用需求时间减去到达时间得到的结果就是时间裕量(slack =required time- arrival time)。

如果是正数则说明路径延时满足需求,如果是负数则说明延时不满足。其中比较重要的时Hold Time Slack。

计算:

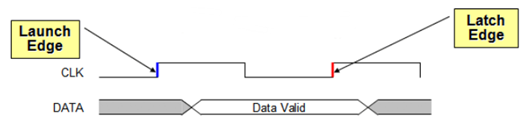

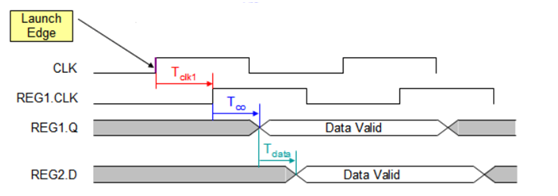

仍然以该电路为例

发射沿(Launch Edge):产生数据的REG1的clock上升沿;

锁存沿(Latch Edge):接受数据的REG2的clock的上升沿,延时Launch Edge1个时钟;

1.5.2 数据到达时间(Data Arrival Time)

Tclk1= CLK到达REG1的时间

Tco = REG1固定延时

Tdata= 数据传输时间

时序图如下:

Data Arrival Time = Launch Edge+Tclk1+Tco+Tdata

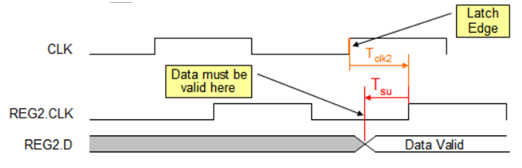

1.5.3 时钟到达时间(Clock Arrival Time)

时序图如下:

Clock Arrival Time = latch Edge+Tclk2

1.5.4 数据建立需求时间(Data Required Time Setup)

因为数据必须在Tsu之前有效,因此:

Data Required Time Setup = Clock Arrival Time - Tsu

1.5.5 数据保持需求时间(Data Required Time Hold)

因为数据必须在Th之后才能改变,因此:

Data Required Time Hold= Clock Arrival Time+Th

1.5.6 计算Slack

Setup Slack = Data Required Time Setup - Data Arrival Time

= Clock Arrival Time - Tsu - (Launch Edge+Tclk1+Tco+Tdata )

= (latch Edge+Tclk2) - Tsu - (Launch Edge+Tclk1+Tco+Tdata )

= (latch Edge - Launch Edge) + (Tclk2 - Tclk1) - Tsu - Tco - Tdata

即Setup Slack=Tclk + Tskew - Tsu - Tco - Tdata(=Tcomb)

若Setup Slack為正,表示Data Required Time在Data Arrival Time之後,所以一定滿足Setup Time,反之若Setup Slack為負,則表示Data Arrival Time在Data Required Time之後,所以一定無法滿足Setup Time。

Hold Slack = Data Arrival Time - Data Required Time Hold

= (next)Launch Edge+Tclk1+Tco+Tdata - (Clock Arrival Time+Th)

= (next)Launch Edge+Tclk1+Tco+Tdata - (latch Edge + Tclk2 + Th)

= Tclk1 - Tclk2 +Tco +Tdata - Th

即Hold Slack=Tco +Tdata - Th - Tskew

若Hold Slack為正,表示Data Arrival Time在Data Required Time之後,所以一定滿足Hold Time,反之若Hold Slack為負,則表示Data Required Time在Data Arrival Time之後,所以一定無法滿足Hold Time。

参考文献:

(原創) timing中的slack是什麼意思? (SOC) (Quartus II) - 真 OO无双 - 博客园 (cnblogs.com)

【基础知识】时序(Slack、Setup、Hold、Jitter、Skew、亚稳态) - 要努力做超人 - 博客园 (cnblogs.com)

校招Verilog——异步复位同步释放 - 咸鱼FPGA - 博客园 (cnblogs.com)