中断第处理外部突发事件的一个重要技术

硬件中断

外部中断

一般是外设发出的中断

内部中断

硬件出错或运算出错引起的中断,不可被屏蔽

软件中断

中断处理程序

CPU必须建立中断信息和中断处理程序之间的联系

中断信息中包含(1byte)中断类型码,CPU根据此来定位中断处理程序

中断向量表:存放中断类型码和中断处理程序的对应关系的表,存放中断处理程序的入口地址

8086的中断向量表是放在内存起始位置总共256个中断类型,占用1024个字节

中断过程:

- 取得中断类型码N

- 标志位寄存器入栈,pushf

- 设置标志寄存器的TF和IF为0。TF=0,IF=0

- CS入栈,push cs

- IP入栈,push ip

- 获取中断类型码4和中断类型码*4+2两个字单元读取16段地址和16位偏移地址,获取中断入口,(ip)=(N4),(cs)=(N4+2)

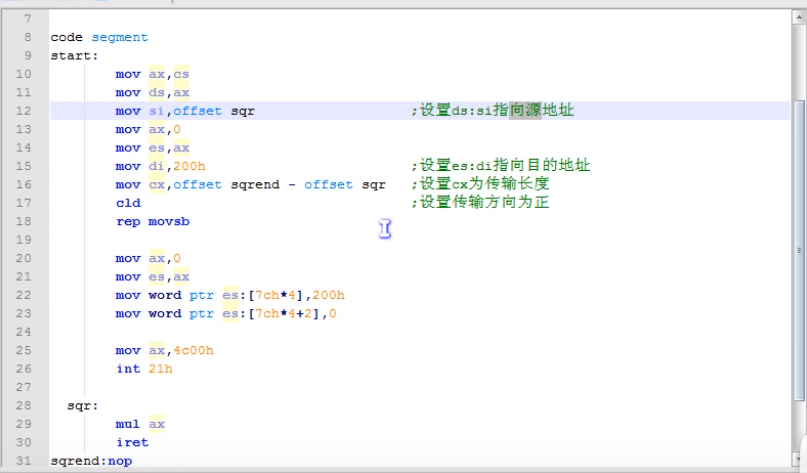

中断处理程序的常规步骤:

(1) 保存用到的寄存器

(2) 处理中断

(3) 恢复用到的寄存器

(4)用iret指令返回,iret指令就相当于pop ip pop cs popf

编译器可以使用加减乘除减来处理两个常数的运算,减号两边的操作数必须在编译后就能确定数值,可以是标号,不能是寄存器

单步中断

CPU在执行完一条指令之后,如果检测到标志位寄存器TF为1,则产生单步中断

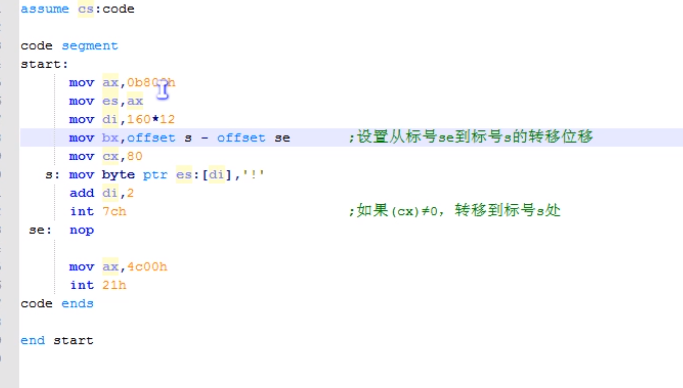

响应中断的特殊情形:有些情况下CPU在执行完当前指令后,即便发生中断,也不会响应

例如:

在执行完ss寄存器传送数据的指令后,即便检测到中断信号,也不会响应,因为ss和sp共同完成栈顶的位置,CPU响应中断是需要用到栈结构的,ss改变sp没有设置,指向不确定的栈顶

int指令

相当于引发一个n号中断,执行中断子程序,通常与iret指令相互配合,iret中断返回

执行过程:

(1)取中断类型码

(2)标志位寄存器入栈:TF=0,IF=0

(3)CS、IP入栈

(4)(ip)=nx4,(cs)=(nx4+2)

转去中断处理程序

]

]

端口的读写(主要指的是硬件外设提供的端口)

CPU可以直接访问内存、端口、寄存器

端口读写指令只有两条:in out

访问端口:in al,60h从60h号端口读入一个字节

无论读取还写出都是只能使用ax寄存器

PC机都有一个CMOS RAM芯片,共128个字节

该芯片有70h,71h两个端口

shl和shr

shl为逻辑左移

shr为逻辑右移

如果移动的位数大于1的时候,将移动的位数放入cl中才能使用

移动的过程中溢出的进入CF位

外中断源一共有两类:

可屏蔽中断

不可屏蔽中断

CPU在检测到可屏蔽中断信息时

如果IF=1,CPU在执行完当前指令后响应中断

如果IF=0,不响应中断,在中断子程序的过程中,关闭IF

sti指令:设置IF=1

cli指令:设置IF=0

键盘的处理过程:

按下一个键产生的扫描码为通码

松开一个键产生的扫描码为断码

两者相差80H

BIOS提供int 9处理中断输入