推荐阅读AMD官方文档,该文档介绍了各种资源的具体含义。

链接: 7 Series FPGAs Configurable Logic Block User Guide (UG474)

以XC7A35T为例:

Logic Cells:逻辑单元,对于7系列来说,The ratio between the number of logic cells and 6-input LUTs is 1.6:1,也就是说,Logic Cell的数量为LUT数量的1.6倍。

Slice:切片,7系列中,一个Slice里有4个6输入LUT,3个多路选择器 ,1个快速进位链,和8个触发器。

Slice * 4 * 1.6就是Logic Cells的数量。

CLB Flip Flops:寄存器资源。

Maximum Distributed RAM (Kb):最大分布式RAM资源,Kb单位。

Block RAM/FIFO w/ ECC (36 Kb each):块RAM资源的个数,每个36Kb。

Total Block RAM (Kb):总共的块RAM资源,用Block RAM/FIFO w/ ECC (36 Kb each) * 36就是。

CMTs (1 MMCM + 1 PLL):时钟资源,1个CMTs包含1 MMCM(混合模式时钟管理器) + 1 PLL(锁相环)。

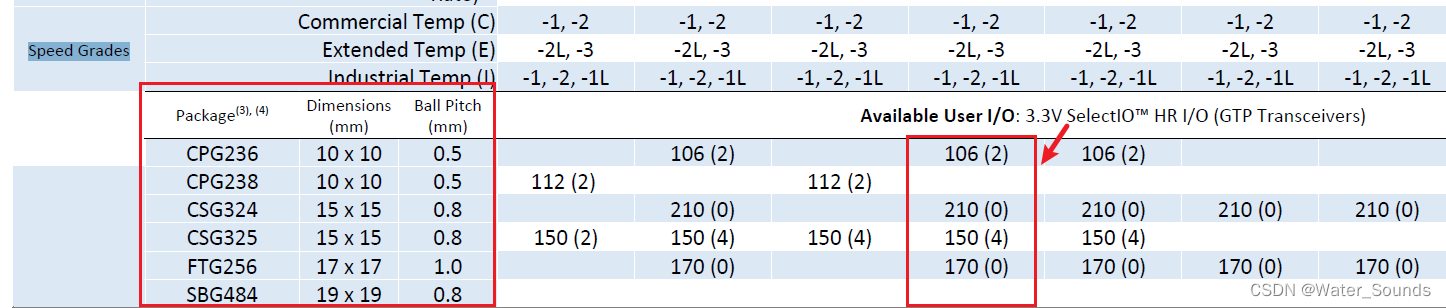

Maximum Single-Ended I/O:单端口的IO最大数量。

Maximum Differential I/O Pairs:差分IO口的最大对儿数。

DSP Slices:DSP切片。

PCIe Gen2:PCIe硬核。

GTP Transceivers:高速串行收发器。

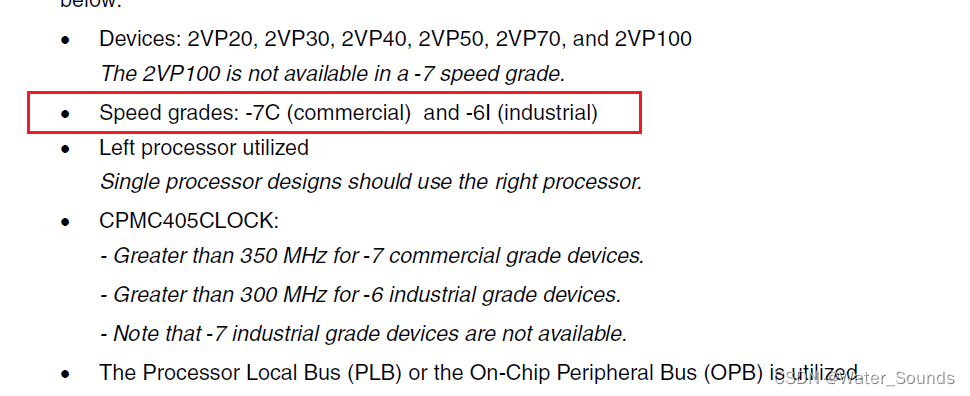

Speed Grades:速度等级,数越小,速度越高,性能越好,带L的表示低功耗。

剩下的资源都是封装,尺寸,厚度,IO数和对应封装所具有的(GTP收发器)

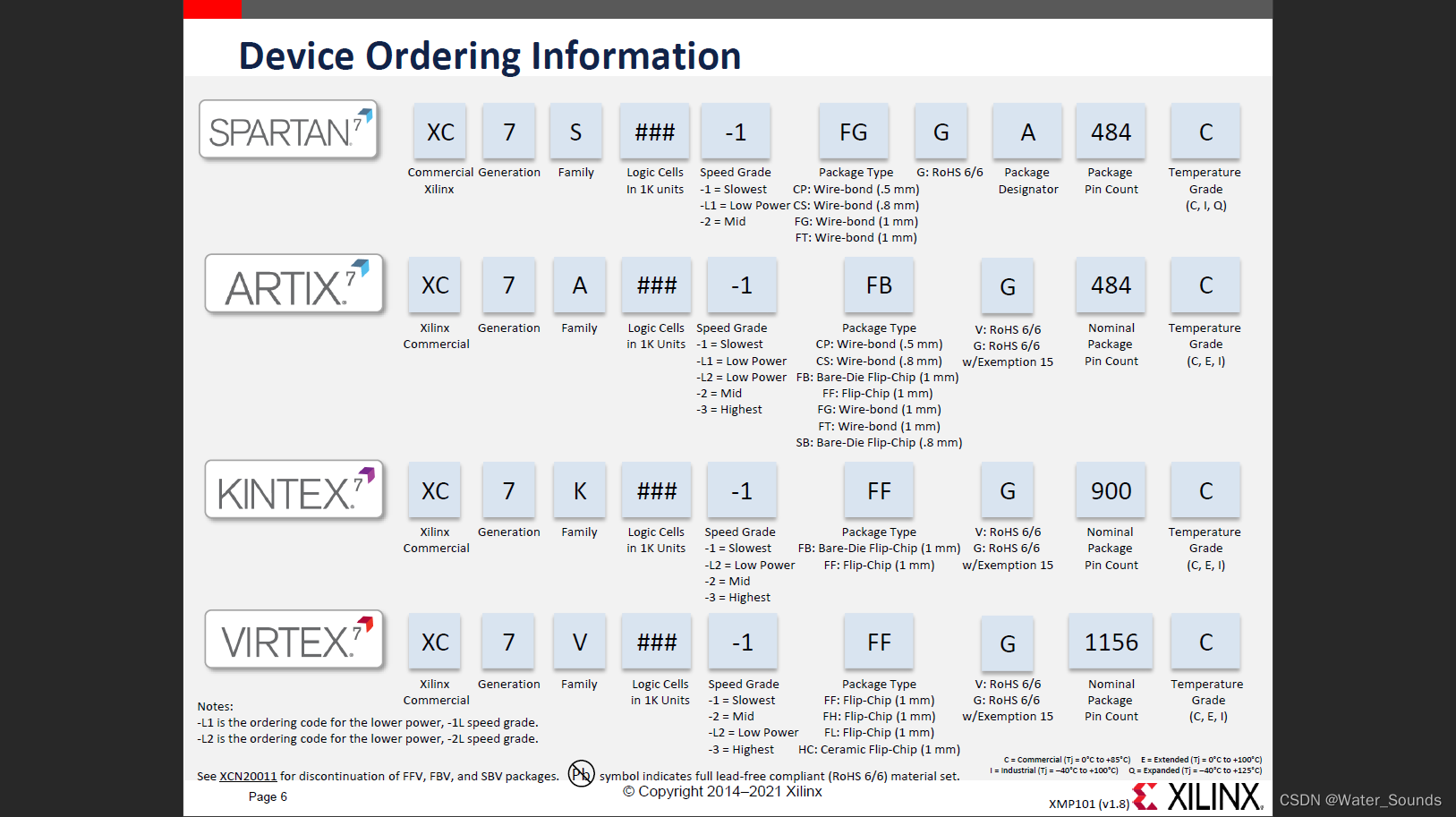

命名规则: