本文从0开始叙述过程。

使用的工具为vivado2016.4,sdk也是2016.4.

准备工作:

首先下载如下的目标文件:

1.下载xilinx官方的bootloader文件

$ git clone https://github.com/Xilinx/u-boot-xlnx.git boot_loader-generator

2.下载xilinx device tree生成工具

git clone https://github.com/Xilinx/device-tree-xlnx.git device_tree-generator

3.下载dtc编译工具

git clone https://git.kernel.org/pub/scm/utils/dtc/dtc.git dtc

4.下载linux kernel

git clone https://github.com/Xilinx/linux-xlnx.git linux_kernel-sources

5.下载root file system

$ git clone git://git.buildroot.net/buildroot file_system

6.拷贝用户空间AXIDMA测试程序

git clone https://github.com/bperez77/xilinx_axidma

PL端

1.创建PL端工程

这里给一张图,按图在vivado里设置该工程,(我用的是zedboard)

2.创建设备树

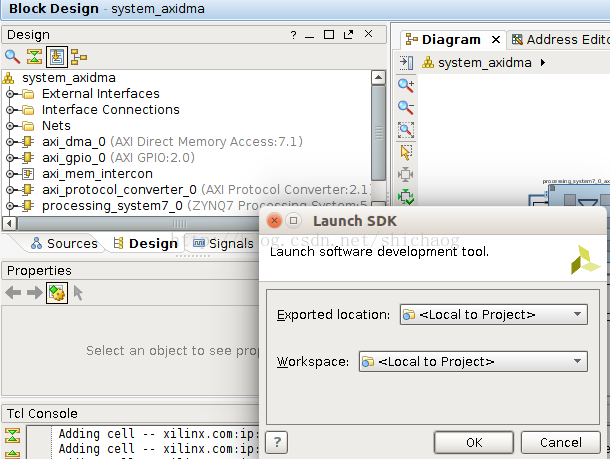

a)在生成bit文件并export后的vivado工程中,选择file--》launch sdk---》点击ok

b)在菜单栏中选择Xilinx Tools --> Repositories

c)在弹窗中选择New,并添加在第一小节中下载的device tree,如下图所示。

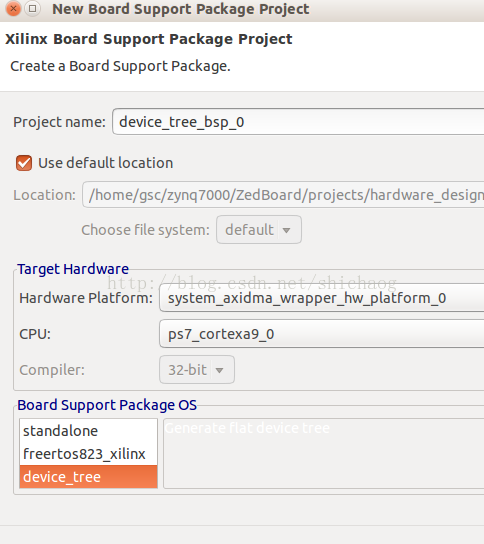

d)接下来创建BSP

选择File-->New-->Board Support Package,在Board Support Package框中选择 device tree,然后点击Finish。在跳出的窗口中选择bootargs,并填入如下:

console=ttyPS0,115200 root=/dev/mmcblk0p2 rw rootfstype=ext4 earlyprintk rootwait

完成后会多出如下内容:

生成的设备树位于axidma_user/axidma_user.sdk/device_tree_bsp_0:

其中pl.dtsi是PL侧设备树信息,正确的工程生成的设备树如下:

/*

* CAUTION: This file is automatically generated by Xilinx.

* Version:

* Today is: Sun Apr 2 18:20:15 2017

*/

/ {

amba_pl: amba_pl {

#address-cells = <1>;

#size-cells = <1>;

compatible = "simple-bus";

ranges ;

axi_dma_0: dma@40400000 {

#dma-cells = <1>;

clock-names = "s_axi_lite_aclk", "m_axi_sg_aclk", "m_axi_mm2s_aclk", "m_axi_s2mm_aclk";

clocks = <&clkc 15>, <&clkc 15>, <&clkc 15>, <&clkc 15>;

compatible = "xlnx,axi-dma-1.00.a";

interrupt-parent = <&intc>;

interrupts = <0 29 4 0 30 4>;

reg = <0x40400000 0x10000>;

xlnx,addrwidth = <0x20>;

dma-channel@40400000 {

compatible = "xlnx,axi-dma-mm2s-channel";

dma-channels = <0x1>;

interrupts = <0 29 4>;

xlnx,datawidth = <0x20>;

xlnx,device-id = <0x0>;

};

dma-channel@40400030 {

compatible = "xlnx,axi-dma-s2mm-channel";

dma-channels = <0x1>;

interrupts = <0 30 4>;

xlnx,datawidth = <0x20>;

xlnx,device-id = <0x0>;

};

};

axi_gpio_0: gpio@41200000 {

#gpio-cells = <2>;

compatible = "xlnx,xps-gpio-1.00.a";

gpio-controller ;

reg = <0x41200000 0x10000>;

xlnx,all-inputs = <0x0>;

xlnx,all-inputs-2 = <0x0>;

xlnx,all-outputs = <0x1>;

xlnx,all-outputs-2 = <0x0>;

xlnx,dout-default = <0x00000000>;

xlnx,dout-default-2 = <0x00000000>;

xlnx,gpio-width = <0x8>;

xlnx,gpio2-width = <0x20>;

xlnx,interrupt-present = <0x0>;

xlnx,is-dual = <0x0>;

xlnx,tri-default = <0xFFFFFFFF>;

xlnx,tri-default-2 = <0xFFFFFFFF>;

};

};

};

生成FSBL

依然是刚刚打开的skd中。

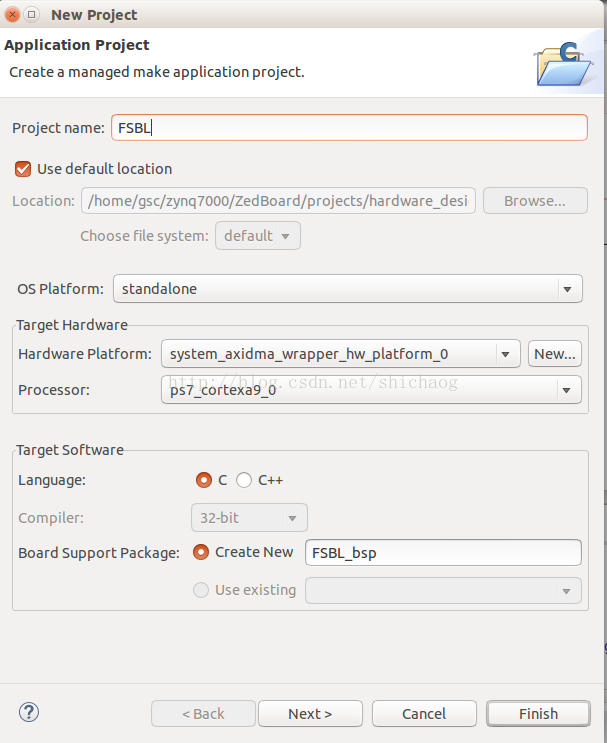

a)File->New->Application Project.注意:按如下方式核对一下。无误后点击finish。

b)在Project explorer中右键FSBL,然后选择Bulid Configuration项,然后选择Set Active ->Release。再一次右键FSBL,然后选择Clean Project,然后在邮件FSBL,然后选择Build Project。

如果顺利console窗口的输出如下:

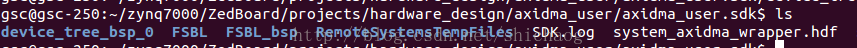

其所在目录和device tree在统一个目录下:

编译u-boot

按如下方式修改u-boot,使用SD上的文件系统而非ramdisk文件系统

导出xilinx路径:

export PATH=/opt/Xilinx/SDK/2016.4/gnu/arm/lin/bin:$PATH

export CROSS_COMPILE=arm-xilinx-linux-gnueabi-

然后编译

gsc@gsc-250:~/zynq7000/ZedBoard/resources/boot_loader/boot_loader-generator$ make distclean

gsc@gsc-250:~/zynq7000/ZedBoard/resources/boot_loader/boot_loader-generator$ make zynq_zed_config

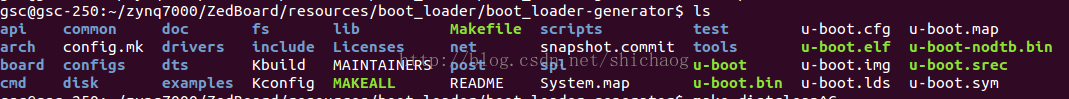

编译完成以后,u-boot跟目录变成:

我们需要图中绿色的u-boot文件,这里将其重命名成u-boot.elf。下一小节将使用它。

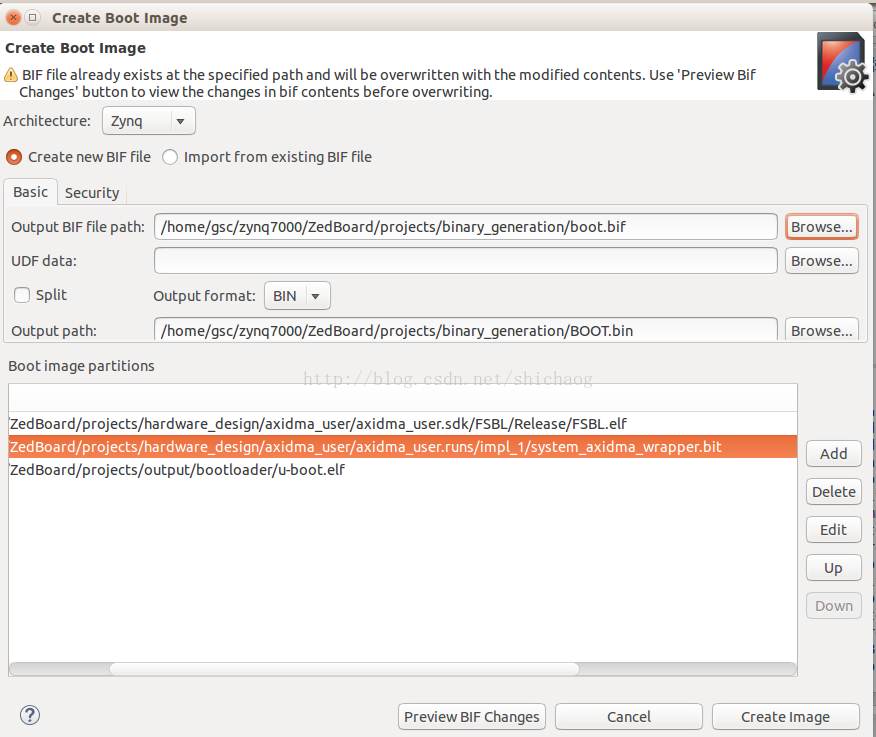

生成二进制文件

依然是SDK里。选择Xilinx Tools->Create Boot Image,切记相关配置。

其中-boot.elf,FSBL.elf以及bit文件是前面生成的。

最终将在output path下指定的路径里将生成Boot.bin文件供后面使用。至此可以退出SDK。

编译linux

导出xilinx路径:

export PATH=/opt/Xilinx/SDK/2016.4/gnu/arm/lin/bin:$PATH

export CROSS_COMPILE=arm-xilinx-linux-gnueabi-

配置linux

$ make distclean

$make ARCH=arm xilinx_zynq_defconfig

$ make ARCH=arm menuconfig

$ export PATH=/home/gsc/zynq7000/ZedBoard/projects/boot_loader/tools/:$PATH(这个是前面编译生成uboot下的tools路径)

$make ARCH=arm UIAMGE_LOADADDR=0x8000 uImage

这里需要配置linux,具体来说就是去掉ramdisk的支持,并且开启代码的支持。

文件太长不单独列出,有需要,下载地址:

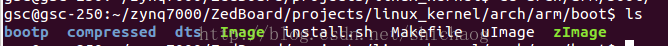

编译完成后

生成linux加载使用的设备树

如果没错,则生成的设备树在如下目录:

使使用如下命令生成设备树

使使用如下命令生成设备树

gsc@gsc-250:~/zynq7000/ZedBoard/projects/linux_kernel/scripts/dtc$ dtc -O dtb -I dts -o devicetree.dtb /home/gsc/zynq7000/ZedBoard/projects/hardware_design/axidma_user/axidma_user.sdk/device_tree_bsp_0/system.dts

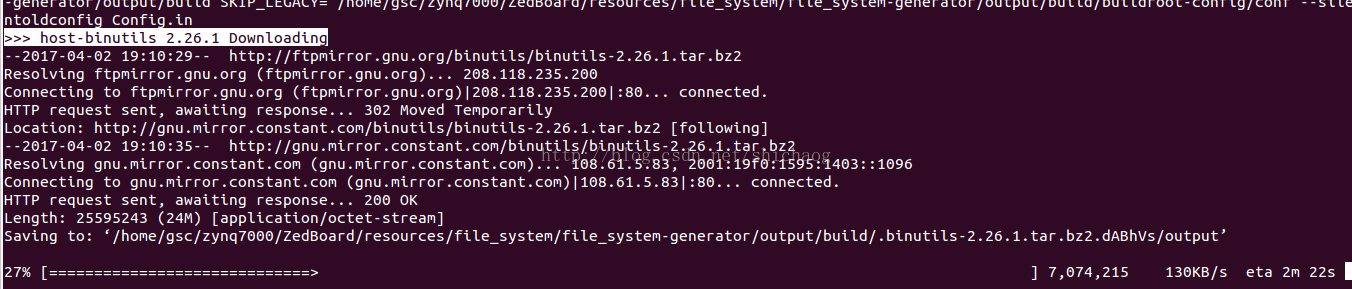

生成文件系统

导出xilinx路径:

export PATH=/opt/Xilinx/SDK/2016.4/gnu/arm/lin/bin:$PATH

export CROSS_COMPILE=arm-xilinx-linux-gnueabi-

make xconfig

make

整个编译过程会根据配置先下载相关工具,然后进行编译。

在生成的目录中

file_system/output/images/rootfs.ext4

编译DMA测试程序:

make CROSS_COMPILE=arm-linux-gnueabihf- ARCH=arm KBUILD_DIR=</path/to/kernel/tree> driver

拷贝到SD中

1.拷贝跟文件系统到ext4分区:

sudo mount -t ext4 -o loop XXX/rootfs.ext4 /mnt

sudo cp -rf /mnt/* ${Where you mount SD card}

sudo umount -l /mnt

如生成的是rootfs.tar这种形式的

sudo tar -C /destination/of/extraction -xf images/rootfs.tar

将生成的DMA测试程序拷贝到SD卡的/media目录下

2.拷贝系统镜像到FAT分区

boot.bin

devicetree.dtb

uIamge