ARM介绍

嵌入式系统:

嵌入式系统 = 嵌入式硬件 + 嵌入式软件。

硬件是软件的载体,软件是硬件的灵魂。

嵌入式软件:

1、裸机:APP

2、系统:OS+APP

嵌入式硬件:

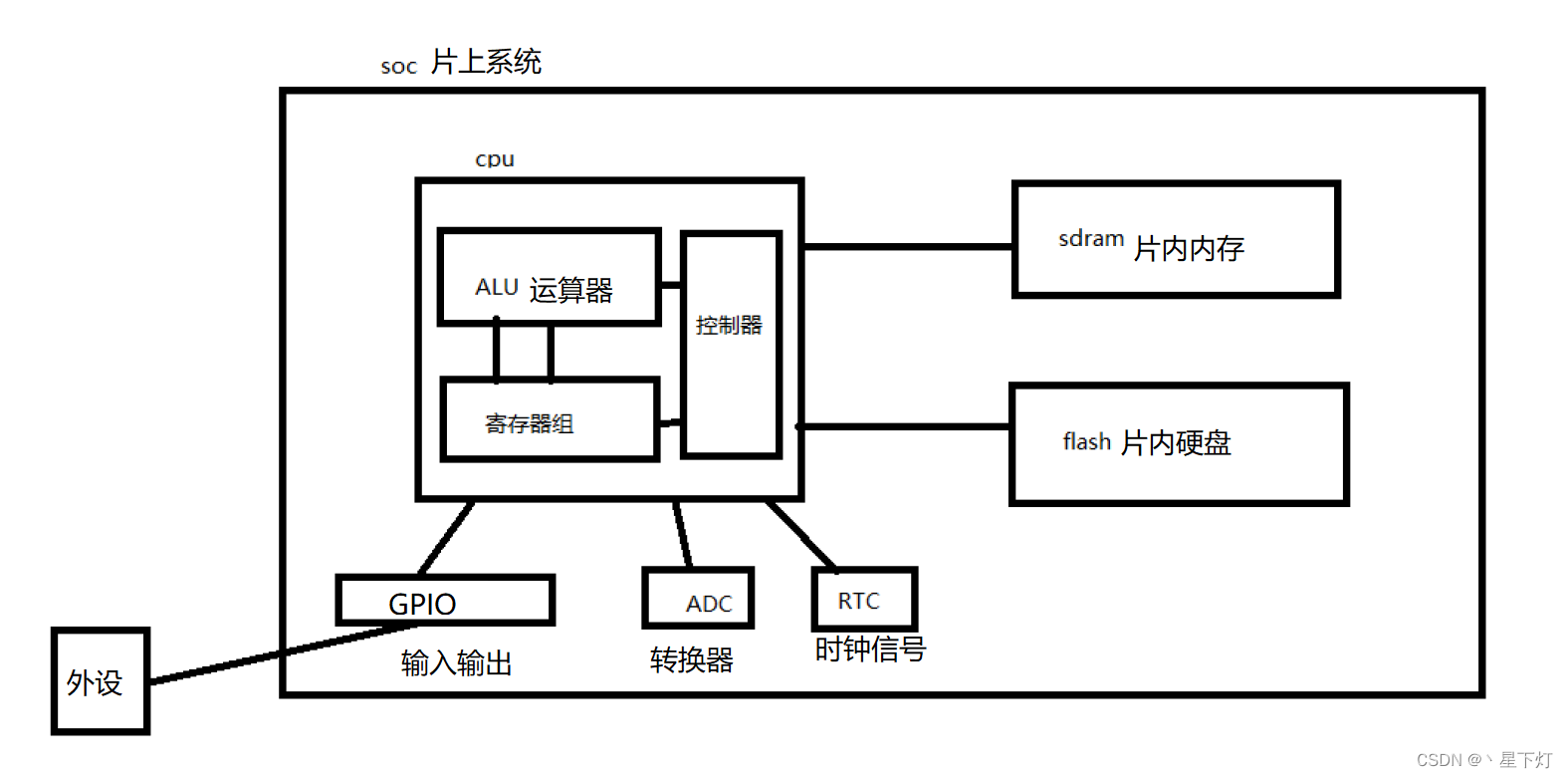

嵌入式硬件 = 输入+输出+存储器+控制器+运算器+总线;

-

输入和输出:GPIO

-

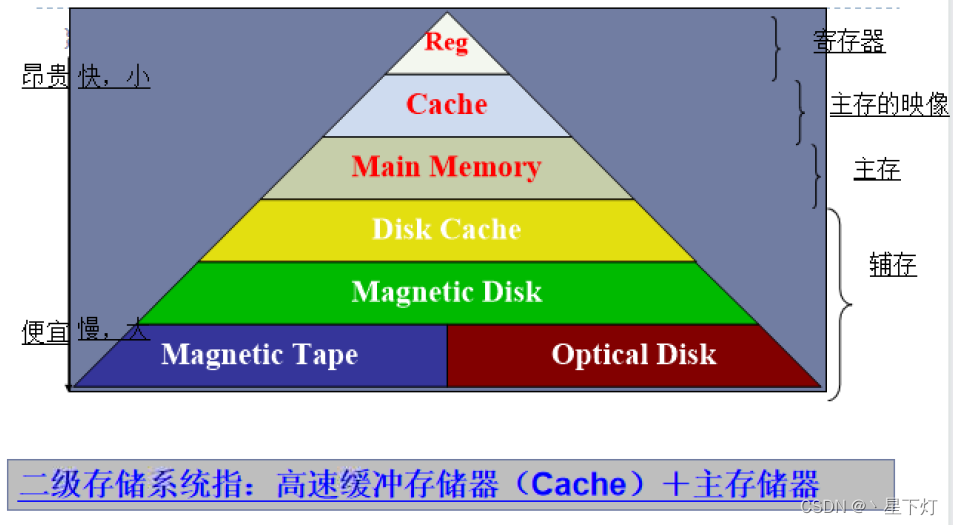

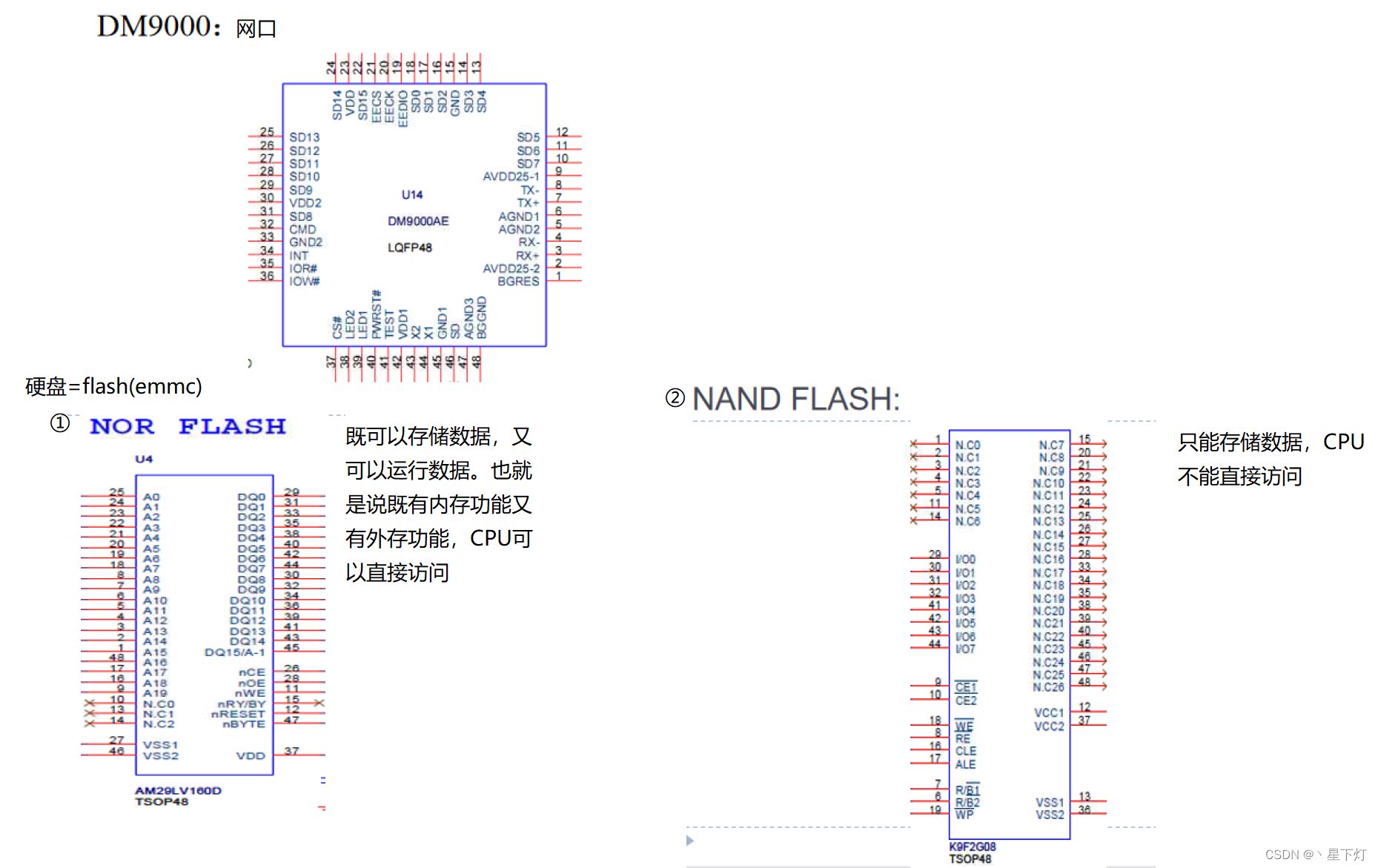

存储器:(从内到外 四级存储体系) 寄存器(Reg) --> Cache(高速缓存器) --> 内存(Main Memory) --> 外存

- 寄存:分为通用寄存器和专用寄存器两类,距离CPU最近的存储单元,CPU可以直接访问,超高速。

- Cache:用来存放正在执行的程序中的活跃部分,CPU可以直接访问,高速。

- 内存(主存):用来存放正在执行的程序,CPU可以直接访问,快速。

- 外存:用来存放需要永久保存的数据的空间,CPU不能直接访问。

-

控制器:指挥中心,由一系列的时序逻辑电路组成

-

运算器:信息进行处理和运算的部件,也称为ALU

-

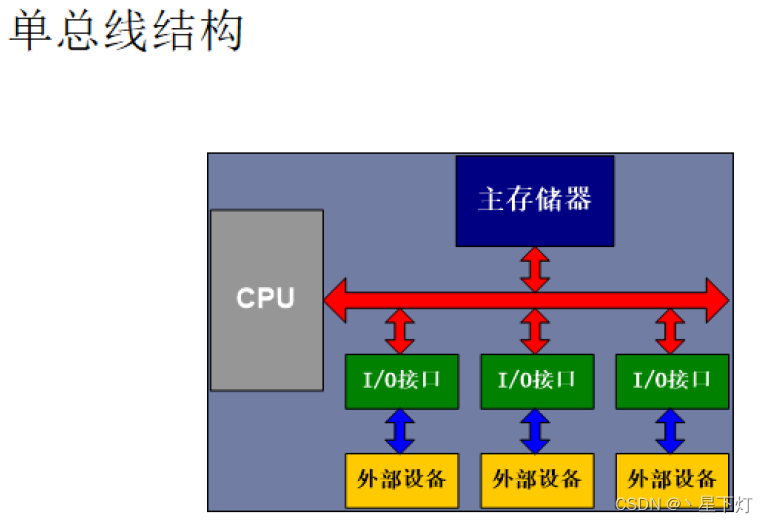

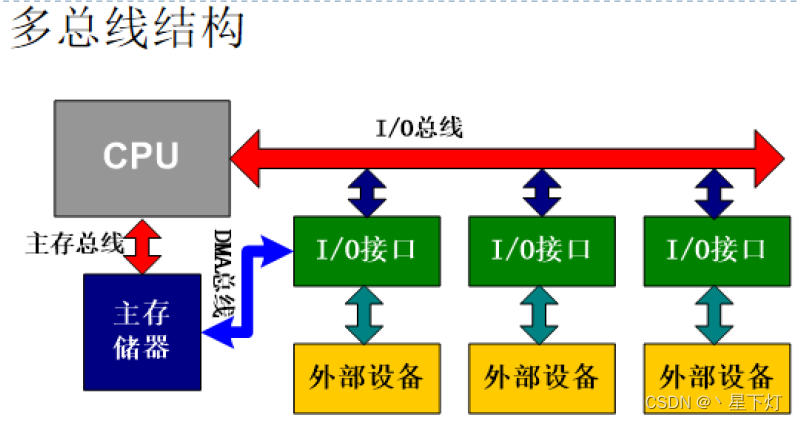

总线(BUS):①用来连接嵌入式硬件的各个模块;②用来传输数据;

.

.

-

CPU = 控制器 + 运算器 + 寄存器组(通用寄存器)

-

SOC = CPU + 外围组件 (System On Chip)

ARM的5大系列:

1、classic系列

ARM7系列:基于ARMv3或ARMv4架构

ARM9系列:基于ARMv5架构

ARM11系列:基于ARMv6架构

2、cortex-M系列

cortex-M0:智能测量

cortex-M0+:人机接口设备

cortex-M1:汽车和工业控制系统

cortex-M3:家用电器

cortex-M4:消费性产品和医疗器械等

(此系列针对成本和功耗比较敏感的应用)

3、cortex-R系列

cortex-R4:汽车制动系统

cortex-R5:动力传动解决方案

cortex-R7:大容量存储控制器等深层嵌入式实时应用

(此系列实时性较好)

4、cortex-A系列

cortex-A5

cortex-A7:智能手机

cortex-A8:平板电脑

cortex-A9:汽车娱乐系统

cortex-A12:数字电视等

cortex-A15

(用于具有高计算要求、运行丰富操作系统及提供交互媒体和图形体验的应用领域)

5、cortex-A5D系列

(基于ARMv8架构,允许在32位和64位之间进行完全的交互操作)

·

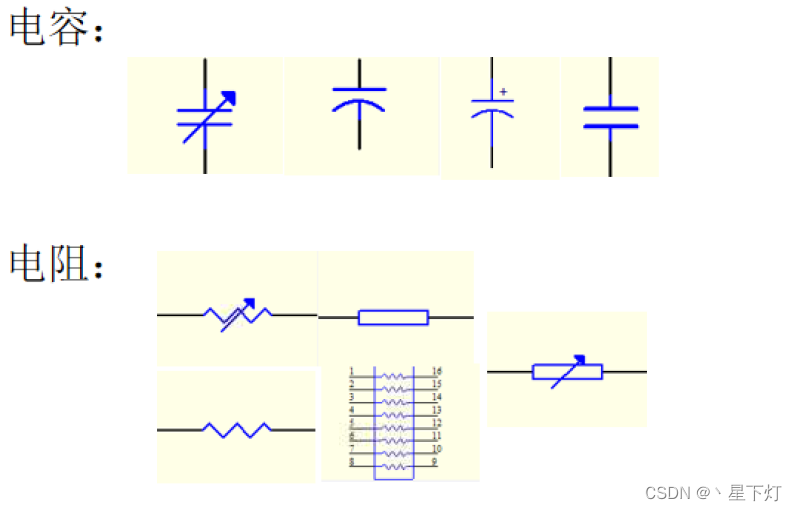

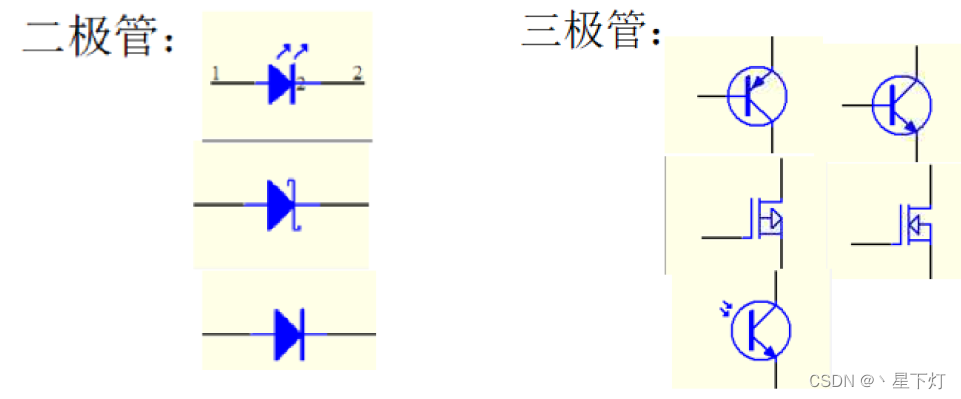

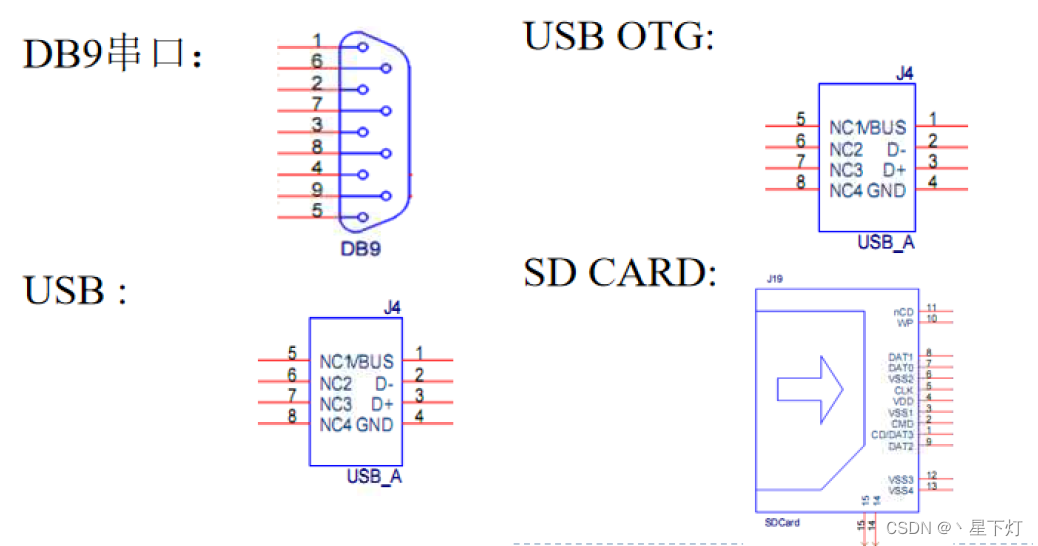

器件

ARM体系结构介绍

ARM代表一款处理的架构,ARM不是芯片,ARM公司向芯片厂商提供ARM内核,芯片厂商用ARM内核和外围组件设计出处理器芯片。

处理器架构 = 处理器内核 = 处理器的控制时序电路+ARM指令集/thumb指令集;

芯片 = 处理器架构(比如ARM架构) + 外围组件;

指令集:

1、RISC:精简指令集。

2、CISC:复杂指令集,每条指令都是由多条精简指令集成。

编程模型

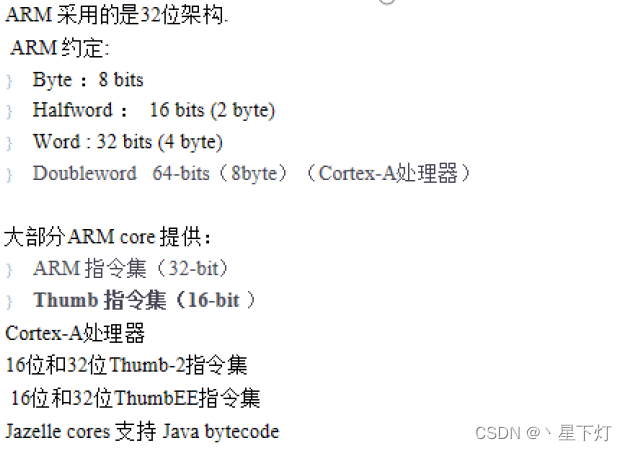

如下约定:

注意:

1、ARM32位架构:表示CPU一次处理指令的能力。32bit

2、CPU的工作 就是周期性的去处理指令(取指令,译码,执行)

3、周期性:看CPU主频,

比如2.7GHZ表示该CPU在1s中内取2.7条指令来处理,周期 = 1/2.7G

4、取指:CPU去存储器中取指令。一般来说在 寄存、cache、主存 中取。每次取32bit刚好是一条ARM指令。

工作模式

当ARM内核处于ARM态,该内核有 7 - 8 种工作模式。

- User:非特权模式,大部分任务执行都是这种模式。

- FIQ:当一个高优先级(fast) 中断产生时将会进入这种模式。

- IRQ:当一个低优先级(normal)中断产生时将会进入这种模式。

- Supervisor:当复位或软中断指令执行时将会进入这种模式。

- Abort:当存取异常时将会进入这种模式。

- Undfine:当执行未定义指令时会进入这种模式。

- Cortex-A特有模式(monitor):ARM Cortex-A系列特有的模式,普通ARM没有。是为了安全而扩展出的用于执行安全监控代码的模式,也是一种特权模式。

- System:系统模式。

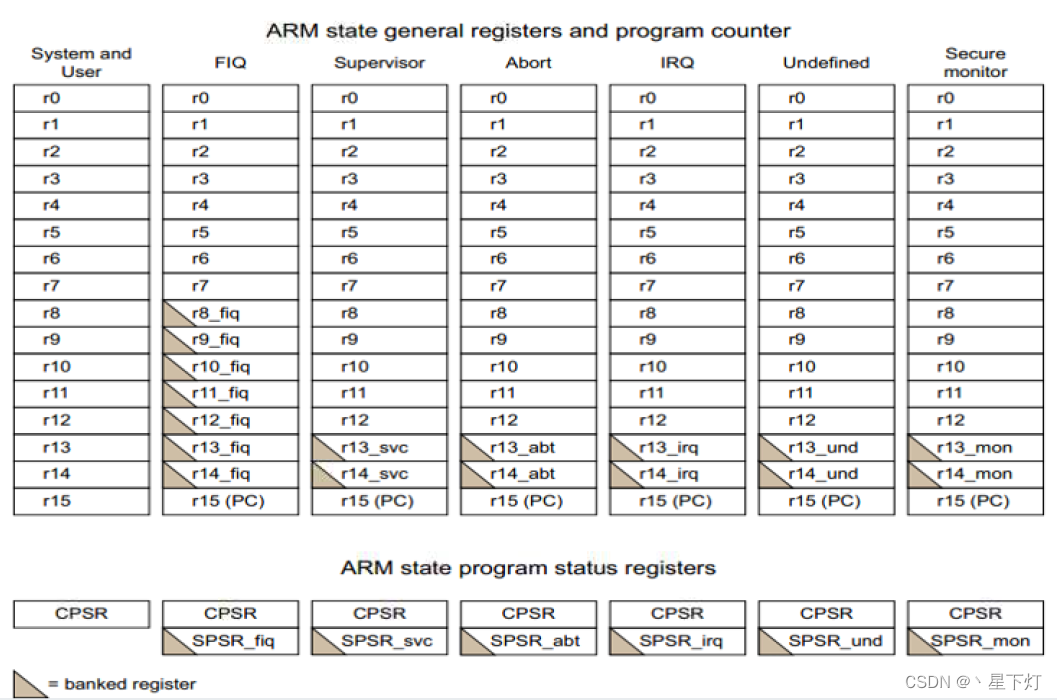

寄存器

作用:用于在指令执行过程中存放运算数据和结果值的容器。

容量

1、普通ARM

有37个寄存器,每一个寄存器的容量是4字节,所以总容量 = 374 = 148(byte)

2、Contex-A的ARM

有40个寄存器,每一个寄存器的容量是4字节,所以总容量 = 404 = 160(byte)

寄存器标识

用R标识,r0,r1,r2……r15,cpsr,spsr

寄存器个数计算

Contex-A提供了40个寄存器,怎么计算的?

r0-r7:8个共用

除了FIQ剩下的7中模式共用r8-r12:5个

FIQ 特殊的专用寄存器r8-r12:5个

User和System模式共用普通寄存器r13-r14:2个

除了User和System模式,其他6种模式都有对应的专用寄存器r13-14:12个

7种模式共用r15:1个

Cpsr寄存器:所有模式共用 1个

Spsr寄存器:User和System模式没有该寄存器,其余6种模式都有自己专用的寄存器:6个

上述之和 = 40个寄存器

详细图解如下:

寄存器分工

40个寄存器中r0-r12用来存放CPU运算数据,其他几个特殊寄存器用来辅助运算。

特殊寄存器:

- r13(sp) :存放sp栈指针;

- r14(lr) :当终端或函数调用发生时用来存放中断的下一条指令地址或函数的返回地址;

- r15(pc):存放pc程序的取指地址,pc指向正在取指的指令而不是正在执行或译码的指令;

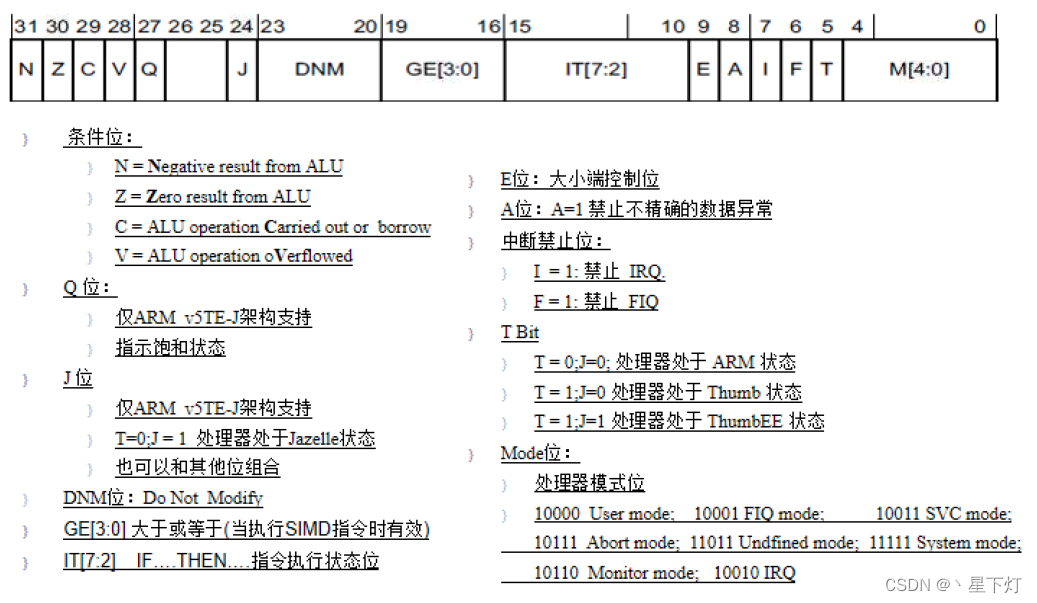

- Cpsr:当前程序状态寄存器。用来存放当前处理器的状态信息;

- Spsr:是Cpsr的备份寄存器。通常在中断时使用,当中断发生时Cpsr将中断地址拷贝到Spsr中以便于中断的恢复;

程序状态寄存器占32bit,每1bit位含义如下:

注意:

在复位后,ARM处理器处于SVC(特权模式)、ARM状态。

指令流水线

指令可以分为几个阶段并且可以并行执行这几个阶段,就称其为几级指令流水线

三级指令流水线:最佳

ARM内核CPU每次都从r15(PC)寄存器种取指令、译码、执行。

取指、译码、执行并行进行。

比如第3条指令取指的同时对第二条指令做译码,对第一条指令做执行。

本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有涉嫌抄袭侵权的内容,请联系:hwhale#tublm.com(使用前将#替换为@)