目录

- 前言

- MIPI简介

- MIPI联盟的MIPI DSI规范

- MIPI名词解释

- MIPI DSI分层结构

- command和video模式

- D-PHY

- Lane模组

- Lane 全局架构

- Lane电压和状态

- DATA LANE操作模式

- 时钟LANE低功耗状态

- 高速数据传输

- 高速CLK传输

- D-PHY总结

- DSI

- CSI

前言

MIPI接口的内部非常复杂,如果不是专门去做MIPI接口,没有必要像研究H264一样往深入的去研究。

我们知道MIPI协议连接了camera与soc、LCD和soc,作为此间的开发者,我们只需要关注他怎么使用就可以了

知识是学不完的,选取我们有需要的即可

MIPI标准文档大全

MIPI简介

MIPI (Mobile Industry Processor Interface) 是2003年由ARM, Nokia, ST ,TI等公司成立的一个联盟,目的是把手机内部的接口如摄像头、显示屏接口、射频/基带接口等标准化,从而减少手机设计的复杂程度和增加设计灵活性。

MIPI联盟下面有不同的WorkGroup,分别定义了一系列的手机内部接口标准,比如

- 摄像头接口CSI

- 显示接口DSI

- 射频接口DigRF

- 麦克风 /喇叭接口SLIMbus

- 等等

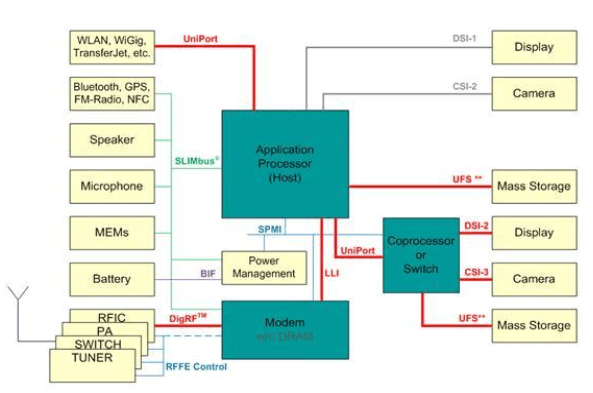

统一接口标准的好处是手机厂商根据需要可以从市面上灵活选择不同的芯片和模组,更改设计和功能时更加快捷方便。下图是按照 MIPI的规划下一代智能手机的内部架构。

MIPI联盟的MIPI DSI规范

MIPI名词解释

-

DCS(Display Command Set)

DSC是用于命令模式显示模块的标准化命令集

-

DBI、DPI(Display Bus Interface,Display Pixel Interface)

DBI:具有显示控制器和帧缓冲区的显示模块并行接口

DPI:无显示控制器和帧缓冲区的显示模块并行接口

-

DSI、CSI(Display Serial Interface,Camera Serial Interface)

DSI:定义了一个位于CPU和显示模组之间的高速串行接口

CSI:定义了一个位于CPU和摄像模组之间的高速串行接口

-

D-PHY

提供DSI和CSI的物理层定义

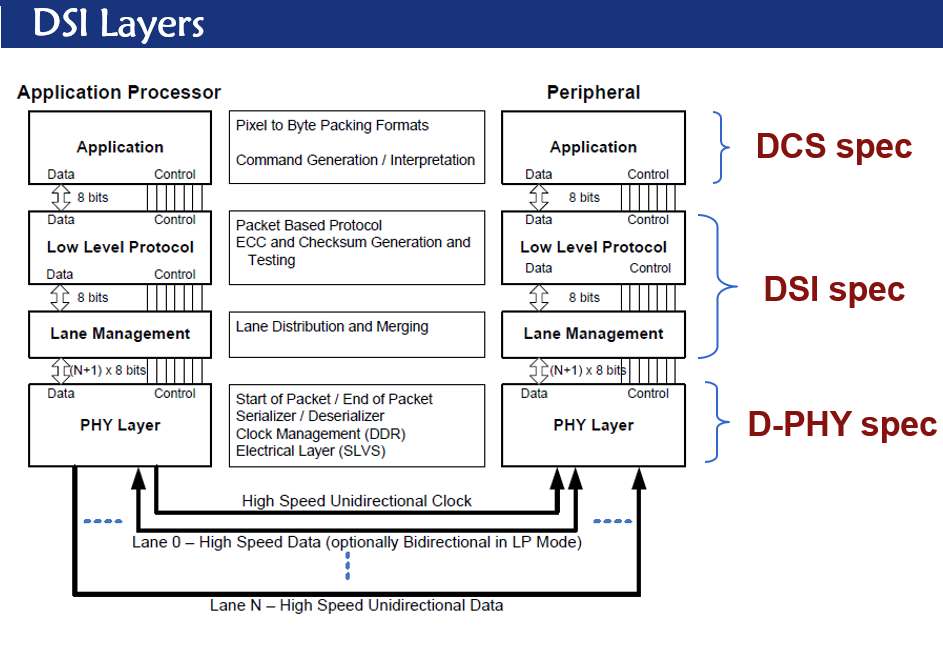

MIPI DSI分层结构

- PHY 定义了传输媒介,输入/输出电路和和时钟和信号机制。

- Lane Management层:发送和收集数据流到每条lane。

- Low Level Protocol层:定义了如何组帧和解析以及错误检测等。

- Application层:描述高层编码和解析数据流。

command和video模式

DSI兼容的外设支持Command或Video操作模式,用哪个模式由外设的构架决定

Command模式是指采用发送命令和数据到具有显示缓存的控制器。主机通过命令间接的控制外设。Command模式采用双向接口Video模式是指从主机传输到外设采用时实象素流。这种模式只能以高速传输。为减少复杂性和节约成本,只采用Video模式的系统可能只有一个单向数据路径

D-PHY

D-PHY 描述了一同步、高速、低功耗、低代价的PHY

PHY配置包括

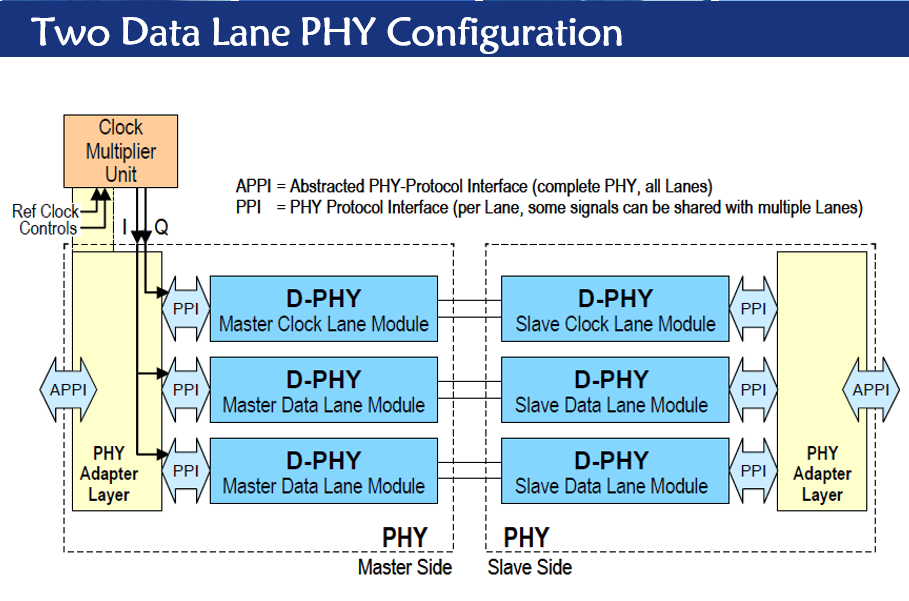

两路数据线的PHY配置如下

三个主要的lane类型

D-PHY的传输模式

- 低功耗(Low-Power)信号模式(用于控制):10MHz (max)

- 高速(High-Speed)信号模式(用于高速数据传输):80Mbps ~ 1Gbps/Lane

D-PHY低层协议规定最小数据单位是一个字节

D-PHY适用于移动应用

- DSI:显示串行接口

一个时钟lane,一个或多个数据lane - CSI:摄像串行接口

Lane模组

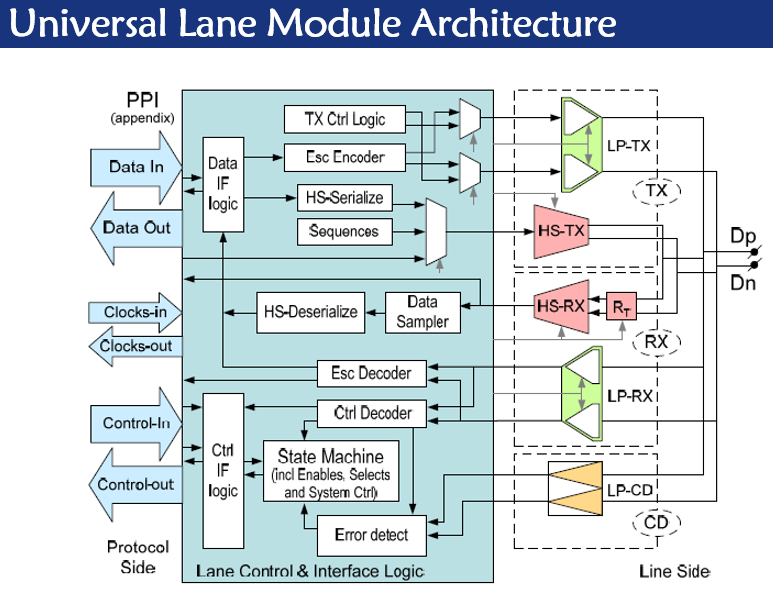

PHY由D-PHY(Lane模块)组成

D-PHY可能包含

- 低功耗发送器—Low-Power Transmitter(LP-TX)

- 低功耗接收器—Low-Power Receiver(LP-RX)

- 高速发送器—High-Speed Transmitter(HS-TX)

- 高速接收器—High-Speed Receiver(HS-RX)

- 低功耗竞争检测器—Low-Power Contention Detector(LP-CD)

三个主要的lane种类

- 单向时钟Lane

• Master:HS-TX, LP-TX

• Slave:HS-RX, LP-RX - 单向数据Lane

• Master:HS-TX, LP-TX

• Slave:HS-RX, LP-RX

-双向数据Lane

• Master, Slave:HS-TX, LP-TX, HS-RX, LP-RX, LP-CD

Lane 全局架构

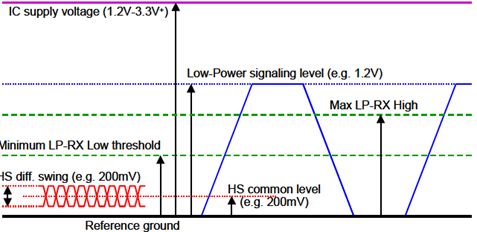

Lane电压和状态

两个LP-TX独立、单端的驱动一组Lane的两条线路

四种可能的低压Lane状态

一个HS-TX差分地驱动一组Lane

两种可能的高速Lane状态

在HS传输的时候,LP接收器在数据线上执行LP-00

线路电压

- LP:0~1.2V

- HS:100~300mV(电泳200mv)

Lane状态

- LP-00,LP-01,LP-10,LP-11(单端)

- HS-0,HS-1(差分)

DATA LANE操作模式

数据Lane的三种操作模式

- Escape mode

- High-Speed(Burst) mode,

- Control mode

从控制模式的停止状态开始的可能事件有

- Escape mode request (LP-11→LP-10→LP-00→LP-01→LP-00)

- High-Speed mode request (LP-11→LP-01→LP-00)

- Turnaround request (LP-11→LP-10→LP-00→LP-10→LP-00)

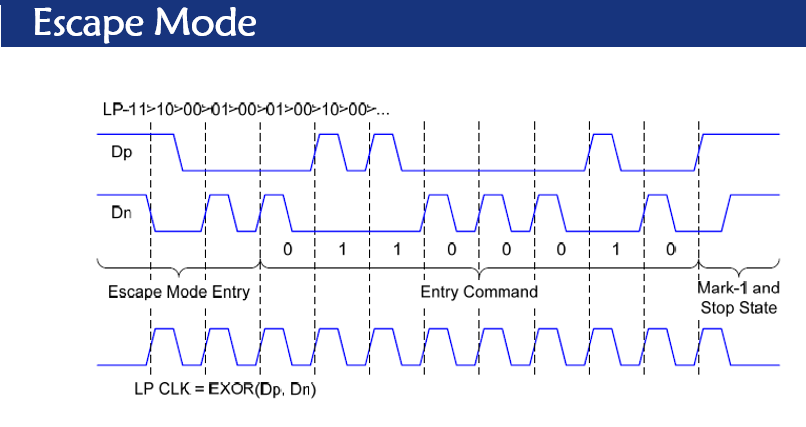

Escape mode是数据Lane在LP状态下的一种特殊操作

- 在这种模式下,可以进入一些额外的功能:LPDT, ULPS, Trigger

- 数据Lane进入Escape mode模式通过LP-11→LP-10→LP-00→LP-01→LP-00

- 一旦进入Escape mode模式,发送端必须发送1个8-bit的命令来响应请求的动作

- Escape mode 使用Spaced-One-Hot Encoding

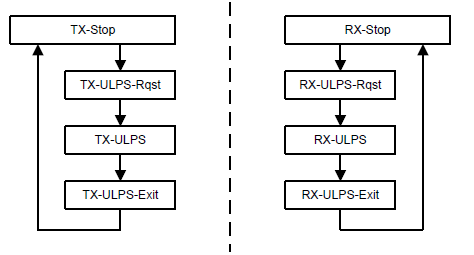

超低功耗状态(Ultra-Low Power State)

时钟Lane的超低功耗状态

- 时钟Lane通过LP-11→LP-10→LP-00进入ULPS状态

- 通过LP-10 → TWAKEUP →LP-11退出这种状态,最小TWAKEUP时间为1ms

高速数据传输

- 发送高速串行数据的行为称为高速数据传输或触发(burst)

- 全部Lanes门同步开始,结束的时间可能不同。

- 时钟应该处于高速模式

各模操作式下的传输过程

- 进入Escape模式的过程 :LP-11→LP-10→LP-00→LP-01→LP-00→Entry Code → LPD (10MHz)

- 退出Escape模式的过程:LP-10→LP-11

- 进入高速模式的过程:LP-11→LP-01→LP-00→SoT(00011101) → HSD (80Mbps ~ 1Gbps)

- 退出高速模式的过程:EoT→LP-11

- 控制模式 - BTA 传输过程:LP-11→LP-10→LP-00→LP-10→LP-00

- 控制模式 - BTA 接收过程:LP-00→LP-10→LP-11

状态转换关系图

Escape Mode图示

时钟LANE低功耗状态

一条时钟Lane可以通过LP-11 -> LP-10 -> LP-00进入低功耗模式ULPS(Ultra-Low Power Status)

退出低功耗模式,通过一个长度为TWAKEUP-的1标记作为停止状态,如下

- LP-10 ->TWAKEUP->LP-11

- TWAKEUP的最小值是1ms

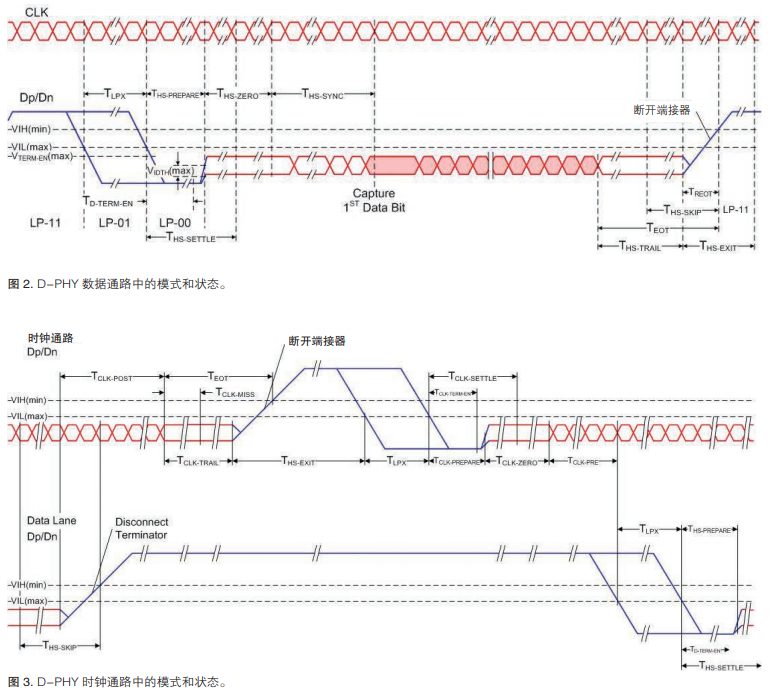

高速数据传输

发送高速串行数据的行为被称作HS传输或burst

传输开始的流程如下

- LP-11 -> LP-01 ->LP-00 -> SoT(0001_1101)

- 数据高速传输(HS Data Transmission Burst)

- 所有Lane将同步开启,但可能在不同时间结束

- 时钟Lane将会在高速模式,向从机侧提供DDR时钟

结束的流程如下

- 在最后一个有效负载数据之后马上切换成差分状态

- 并将此状态保持

THS-TRAIL时间

高速CLK传输

在CKL传输和低功耗模式间切换时钟Lane

- 时钟通道是主通道通向从通道的单向通道

- 在HS模式,时钟Lane提供低振幅差分DDR时钟信号

- 时钟burst总是通过一个HS-0状态开启和结束

- 时钟burst总是包含偶数个转换

时序图如下

D-PHY总结

Lane模组,Lane状态,Lane电压

Lane模组:LP-TX,LP-RX,HS-TX,HS-RX,LP-CD

Lane状态:LP-00,LP-01,LP-10,LP-11,HS-0,HS-1

Line Levels(typical):LP:0-1.2V,HS:100-300mV(Swing:200mV)

操作模式

escape模式进入流程:LP-11 -> LP-10 -> LP-00 -> LP-01 -> LP-00 -> Entry Code -> LPD(10MHz)

escape模式退出流程:LP-10 -> LP-11

高速模式进入流程:LP-11 -> LP-01 -> LP-00 -> SoT(0001 1101) -> HSD(80Mbps - 1Gbps)

高速模式退出流程:EoT -> LP-11

控制模式BTA传输进入流程:LP-11 -> LP-01 ->LP-00 -> LP-10 -> LP-00

控制模式BTA接收进入流程:LP-00 -> LP-10 -> LP-11

系统状态模式

- 低功耗模式(Low-Power Mode)

- 高速模式(High-Speed Mode)

- 超低功耗模式(Ultra-Low Power Mode)

故障检测

- 连接检测—Contention Detection(LP-CD)

- 看门狗计时器

- 序列错误检测(错误报告)

全局操作定时参数

- 时钟通道计时,数据通道计时

- 其他的计时器—初始化、BTA、从ULPS唤醒

电气特性

- HS-RX,LP-RX,LP-TX,LP-CD,引脚特训,时钟信号,时钟计时器

- DC和AC特性

DSI

IDisplay Serial Interface

DSI:定义了一个位于CPU和显示模组之间的高速串行接口

CSI

Camera Serial Interface

CSI:定义了一个位于CPU和摄像模组之间的高速串行接口

现在事无巨细的完全整理出来对我而言没有什么意义,剩下内容待更

本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有涉嫌抄袭侵权的内容,请联系:hwhale#tublm.com(使用前将#替换为@)