引言:本文我们继续介绍Xilinx FFT IP核,主要对IP核的接口进行详细说明,并对IP核信号各个通道接口数据格式进行详细介绍,方便我们进行FPGA软件设计。本文介绍以下接口信号:

- 时钟信号

- 复位信号

- 事件信号

- AXI4-Stream信号

1.时钟信号

aclk(时钟信号)

IP核采用单时钟操作,即aclk,所有输入输出接口及内部逻辑都受这个时钟控制。该时钟的最高频率在软件设计时是有限制的。基于不同的器件家族及FFT/IFFT运算点数及配置,FFT IP核最高运行时钟稍有不同,这从Xilinx官方提供的IP核性能中可以看到,如表1所示。

表1、FFT IP性能和资源利用率(点击看大图)

aclken(时钟使能,可选)

如果aclken选项使能,驱动该端口低电平会暂停IP核当全处理状态,所有内部逻辑都会暂停,驱动该端口高电平会继续IP核处理。

2.复位信号

aresetn(同步清零,可选)

如果aresetn选项使能,驱动该端口低电平,会使所有输出端口、内部计数器和状态恢复到它们的初始状态值。初始状态值如表2所示,该初始状态值也是上电启动默认值。所有挂起的进程、转换计算和卸载处理都会重新初始化,NFFT设置为最大允许的FFT点数(Vivado IDE允许设置的最大值)。缩放因子设置为1/N。对于Radix-4突发I/O和流水线I/O架构使用非4幂次点数,最后一级缩放为1,其余缩放为2,参见表2。

表2、同步清零复位后配置信息

aresetn管脚优先于aclken,如果插入了aresetn,则无论aclken的值如何,都会发生复位。复位至少满足两个时钟周期。

3.事件信号

IP核提供一些实时非AXI信号报告IP核的状态信息。这些信号IP是必须输出的,但是如果这些信号不连接,则会被综合工具综合掉,以节约资源。某些事件信号在某些模式下是不出现的,这在后续会有介绍。

event_frame_started

当IP核开始处理新帧时,会插入该信号,且该信号只持续一个时钟周期。该信号允许用于计数帧数,也可以用于同步配置特殊帧。

envent_tlast_missing

当IP核输入的数据数目大于Vivado设置的最大FFT/IFFT点数时,会插入此信号。该信号持续一个时钟周期。是否插入s_axis_data_tlast与此信号无关。

event_tlast_unexpected

当s_axis_data_tlast插入的位置不是最后一个帧数据时,该时钟会有效,持续一个时钟周期。如果一个帧中出现多个s_axis_data_tlast高电平,此信号也会对应的插入多个。

event_fft_overflow

该信号用来监视FFT/IFFT输出数据m_axis_data_tdata是否溢出。如果数据一直溢出,该信号一直输出高电平。该信号只在缩放模式或者单精度浮点模式下使用,其他配置模式(块浮点模式)无此信号。

event_data_in_channel_halt

该信号在当FFT/IFFT核需要从数据输入通道接收数据,而没有数据可用时,会插入此信号。例如,当NFFT设置为1024点,而输入数据只输入了1000点数据,此时,该信号会插入,直到有新的数据插入时,该信号才会变为低电平。

event_data_out_channel_halt

当FFT/IFFT核需要写数据到输出通道时,但缓冲buffer已经满了,此时,该信号会出现高电平,表示输出通道挂起,直到输出buffer非满,该信号才会变为低电平。该信号只在Non-Realtim模式中应用。

event_status_channel_halt

当FFT/IFFT核需要写数据到状态通道时,但缓冲buffer已经满了,此时,该信号会出现高电平,表示状态通道挂起,直到输出buffer非满,该信号才会变为低电平。该信号只在Non-Realtim模式中应用。

4.AXI4信号

4.1握手协议

FFT IP核使用标准的AXI4-Stream协议格式,通过TREADY和TVALID信号实现上下游模块之间的握手。图1显示了AXI4-Stream通道数据传输模型。

图1、AXI4-Stream通道

4.2 配置通道

配置通道端口信号如表3所示。

表3、配置通道端口信号定义

TDATA数据字段介绍

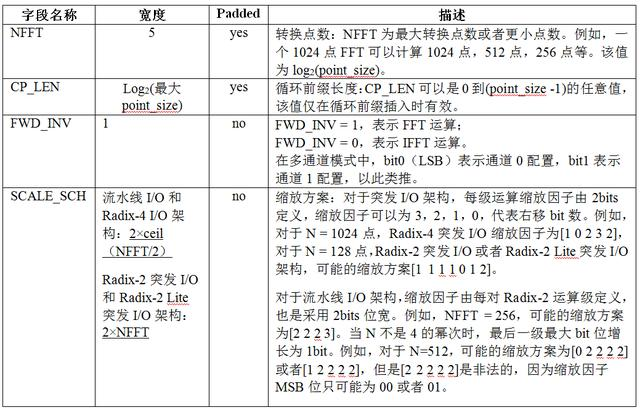

配置通道(s_axis_config)接口是AXI通道,TDATA接口描述如表4所示。所有需要padded的字段如果未达到8bit边界,需要扩展到8bit边界。扩展的bit未可以为任意值,设计为常量值可以节省器件资源。

表4、TDATA字段描述

TDATA数据格式

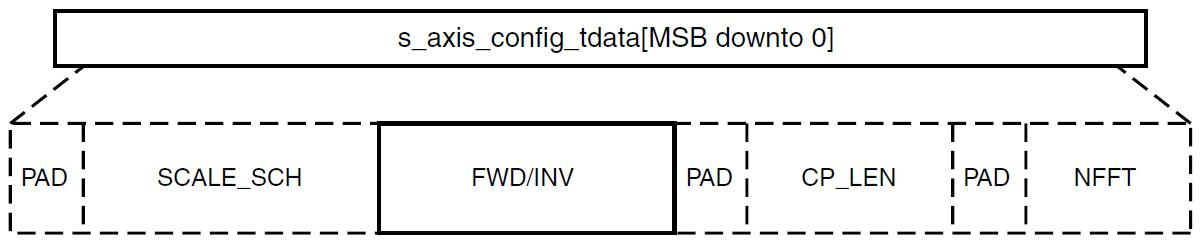

配置字段按照以下顺序打包为s_axis_config_tdata向量。

- NFFT附加padding,可选

- CP_LEN附加padding,可选

- FWD/INV

- SCALE_SCH,可选

图2配置通道TDATA(s_axis_config_tdata)格式。

图2、配置通道TDATA(s_axis_config_tdata)格式

TDATA数据格式举例

IP核配置:最大支持128点转换,该核配置为8点转换;插入循环前缀,4点循环前缀;3通道转换,其中,通道0和通道1执行IFFT转换,通道2执行FFT转换。

表5、配置通道数据格式举例

上述表格5中TDATA总的bit数为19bit,为满足字节边界,需要扩展为24bit,因此给定配置通道TDATA格式如图3所示。

图3、配置通道TDATA s_axis_config_tdata举例

4.3数据输入通道

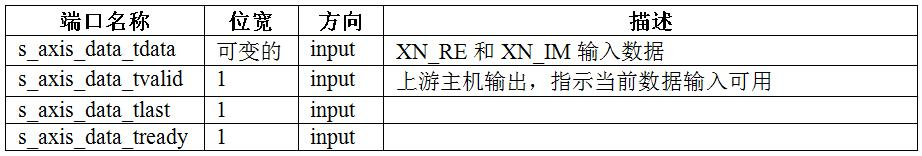

数据输入通道包括需要转换的实部和虚部数据,端口描述如表6所示。

表6、数据输入通道端口定义

TDATA字段

数据输入通道是AXI接口通道,TDATA向量格式如表7所示。

表7、AXI输入数据格式

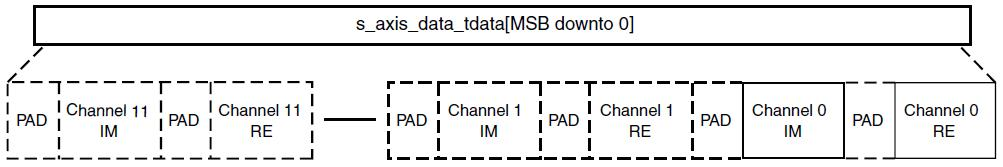

TDATA格式

TDATA数据格式如图4所示。该字段以向量形式打包为s_axis_data_tdata数据。所有需要padded的字段如果未达到8bit边界,需要扩展到8bit边界。扩展的bit未可以为任意值,设计为常量值可以节省器件资源。

图4、数据输入通道TDATA格式

TDATA举例

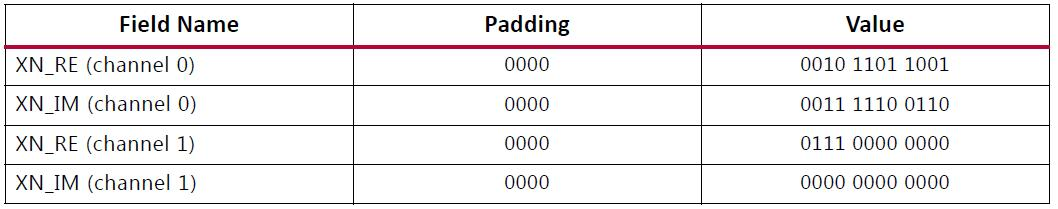

参数配置:2通道FFT数据通道,位宽12-bit数据。

数据通道CH0数据采样值:

- RE = 0010 1101 1001

- IM = 0011 1110 0110

数据通道CH1数据采样值:

- RE = 0111 0000 0000

- IM = 0000 0000 0000

表8、数据输入通道TDATA输入数据

图5、数据输入通道s_axis_tdata格式举例

4.4数据输出通道

数据输出通道上包含转换结果的实部和虚部,在TDATA上传输。TUSER用于传输和TDATA数据相关的状态信息。状态信息用于下游模块处理使用。状态信息包括以下信号:

- XK_INDEX信息

- 每个FFT通道,块指数BLK_EXP

- 每个FFT通道,OVFLO溢出状态信息

表9、数据输出通道端口定义

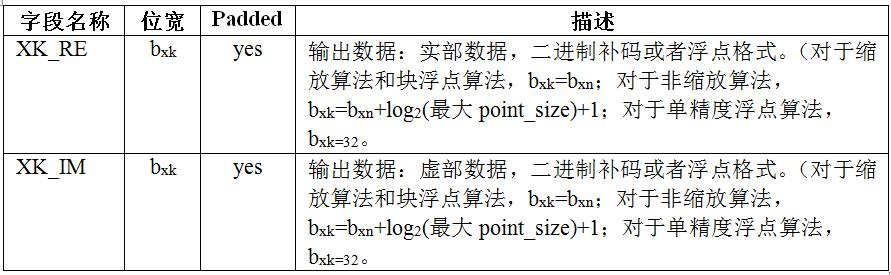

TDATA字段

TDATA字段字段定义如表10所示。

表10、数据输出通道TDATA字段字段定义

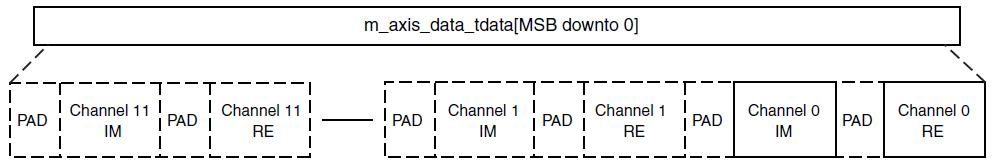

TDATA格式

数据字段按照以下格式以向量形式打包为m_axis_data_tdata。

- 通道0:XK_RE附加padding位

- 通道0:XK_IM附加padding位

- 可选的通道1:XK_RE附加padding位

- 可选的通道1:XK_IM附加padding位

- ……

- 可选的通道11:XK_RE附加padding位

- 可选的通道11:XK_IM附加padding位

图6、数据输出通道TDATA(m_axis_data_tdata)格式

TDATA举例

参数配置:2通道FFT,12-bit位宽数据。

通道0:

- RE = 0010 1101 1001

- IM = 1011 1110 0110

通道1:

- RE = 0111 0000 0000

- IM = 1000 0000 0000

图7、数据输出通道TDATA举例

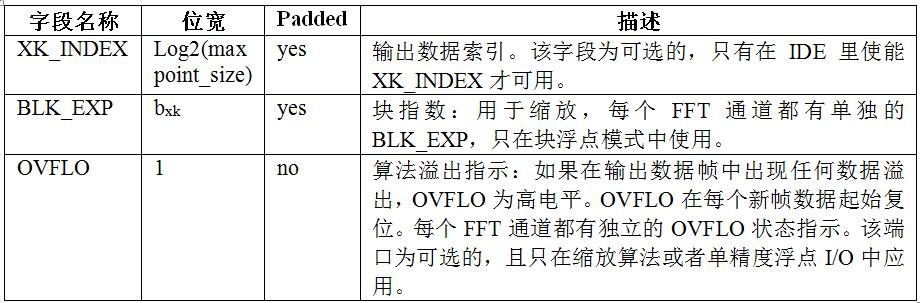

TUSER字段

数据输出通道TUSER字段释义如表11。

表11、数据输出通道TURSER字段定义

TUSER格式

数据字段按照以下格式以向量形式打包为s_axis_data_tuser。

- 可选的XK_INDEX附加padding

- 可选的通道0:BLK_EXP附加padding位

- 可选的通道1:BLK_EXP附加padding位

- ……

- 可选的通道0:OVFLO附加padding位

- 可选的通道1:OVFLO附加padding位

padding为确保TUSER 8-bit对齐。注意IP核不能同时配置为具有BLK_EXP和OVFLO。所有的状态字段都是可选的,当TUSER没有字段时,整个状态通道自动从IP和接口中移除。

图8、输出数据通道TUSER格式

TUSER举例

举例1:

参数配置:2通道FFT,128点转换,溢出和XK_INDEX配置。第三个采样(XK_INDEX = 3)在通道0设置溢出,通道1无溢出。参数配置如表12。

表12、TUSER举例1

图9、TUSER举例1 m_axis_tuser接口数据

举例2:

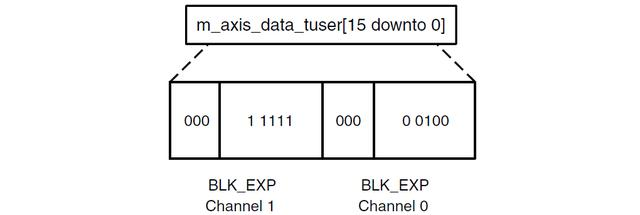

参数配置:2通道FFT,块指数,无XK_INDEX,通道0块指数为4,通道1块指数31,如表13所示。

表13、TUSER举例2

m_axis_data_tuser数据结构如图10所示。

图10、TUSER举例2 m_axis_data_tuser接口数据

4.5状态通道

状态通道包含前帧的状态信息,即和整个数据帧相关的信息。它的目的是用于告知那些不是直接操作数据的后续其他模块控制系统其他部分需要了解的信息。这些信息分类作为前帧状态:

- 每个通道块指数信息:BLK_EXP

- 每个通道溢出信息:OVFLO

注意:IP核不能同时配置为具有BLK_EXP和OVFLO。BLK_EXP状态信息在帧的起始发送,OVFLO在帧的结束发送。

表14、状态通道接口定义

TDATA字段

状态通道TDATA字段定义如表15所示。

表15、状态通道TDATA字段定义

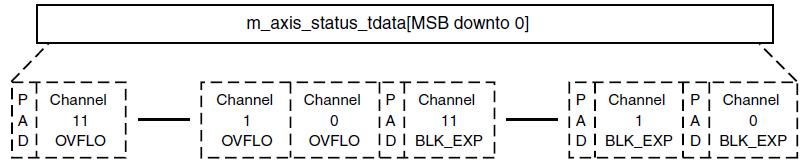

TDATA格式

该字段以向量形式打包为m_axis_status_tdata向量:

- 通道0:可选的BLK_EXP附加padding位

- 通道1:可选的BLK_EXP附加padding位

- ……

- 通道0:可选的OVFLO附加padding位

- 通道1:可选的OVFLO附加padding位

- ……

padding为确保TDATA 8-bit对齐。注意IP核不能同时配置为具有BLK_EXP和OVFLO。所有的状态字段都是可选的,当TDATA没有字段时,整个状态通道自动从IP和接口中移除。

图11、状态通道TDATA字段格式

TDATA举例

举例1

参数配置:4通道FFT和溢出,通道2和3包含溢出配置。

状态通道TDATA举例1如表16所示。

表16、TDATA状态通道举例1

该信号向量长度4bit,扩展为字节边界,因此需要附加4bit,m_axis_status_tdata信号举例如图12所示。

图12、状态通道举例1 m_axis_status_tdata数据格式

举例2

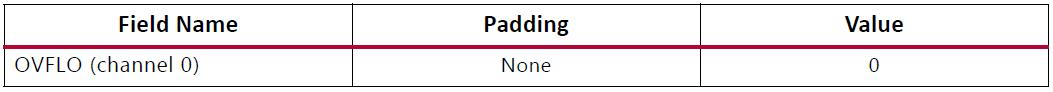

参数配置:单通道FFT和溢出,当前帧不包括溢出。

表17、状态通道TDATA举例2

该信号向量长度1bit,扩展为字节边界,因此需要附加7bit,m_axis_status_tdata信号举例如图13所示。

图13、状态通道TDATA举例2

5.小结

本文我们对FFT IP核接口信号进行了详细的介绍,主要包括时钟、复位接口以及AXI4-Steam接口。AXI4-Stream接口设计配置通道、数据输入通道、数据输出通道以及状态通道。这几个数据通道在数据格式组织上具有相似性,例如,都必须满足8bit字节对齐,都采用小端数据组成格式等。后续文章我们介绍FFT实例时再对这些接口的应用进行讲解。