本文阐述基于Proteus 7.8的简易测频计电路的实现,附具体电路的工程文件下载:

工程文件下载链接

设计要求

- 闸门时间1S﹑10S可选。

- 读数保持时间10秒(可选)。

- 四位数字显示,范围000.1~9999 Hz。

- 能够自动进行下一次测量。

设计方法

分模块完成:

(1) 施密特整形电路,对输入信号进行整形,提高测量的稳定性和可靠性。

(2) 秒信号发生器及分频器,采用计数器构成模1和模10的分频器,分别得到周期为1S和10S的门控信号。

(3) 测量控制(闸门)

(4) 读数保持与清除

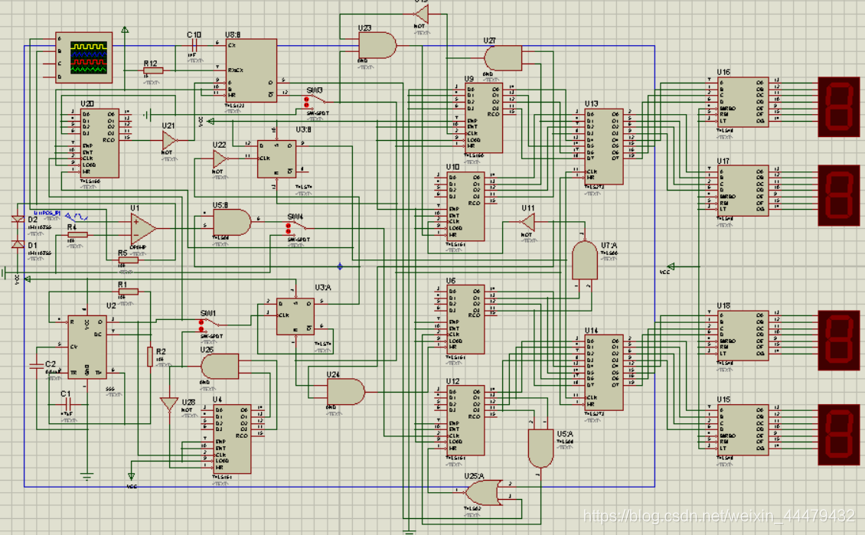

具体电路如下:

电路工作原理分析

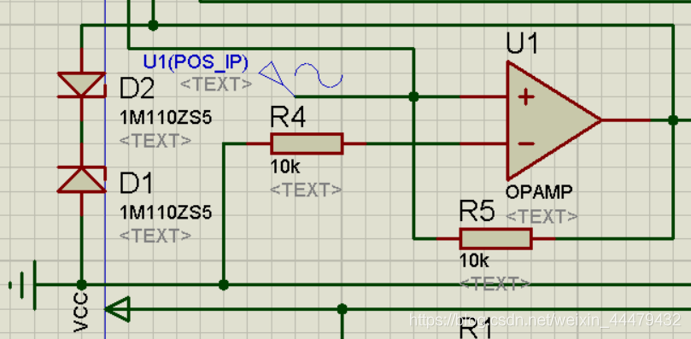

施密特整形电路

施密特整形电路主要是由运算放大器、电阻,稳压二极管组成,产生反馈来维持稳态平整波形的电路。可将三角波、正弦波等变成方波,便于通过电平的高低达到计数的效果,并且还可以将脉冲波整形,避免波形畸变,出现上升沿和下降沿不理想的情况,可用施密特触发器整形后,获得较理想的矩形脉冲。

由于电阻网络将施密特触发器的输入端(即比较器的同相‘+’端)和输出端连接起来,达到反馈的目的。利用稳压隧道二极管来整波,防止出现波形变形。设置阈值施密特触发器能在不同的时刻翻转电平。若输入是绝对值很大的负输入,输出将为低电平;若输入是绝对值很大的正输入,输出将为高电平,这就实现了同相施密特触发器的功能。

实现效果:

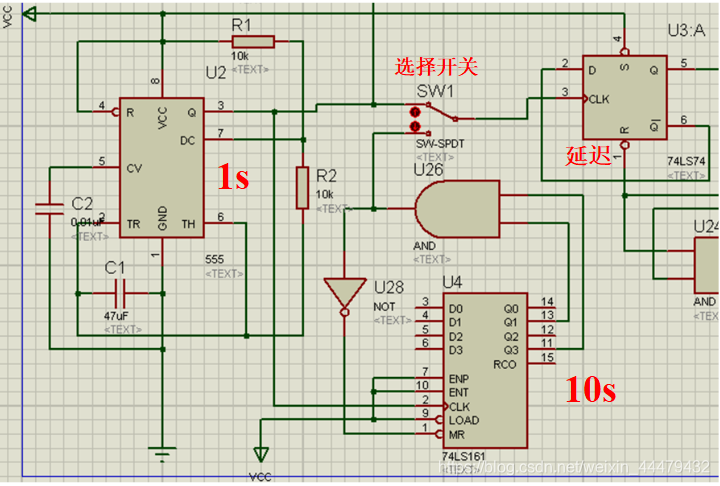

秒信号发生器及分频器

按照要求,采用555定时器,产生周期1s的方波脉冲,按照公式

频率 f =1.43 / ((R1+2R2)*C)

可得当R1=R2=10kΩ,C=47uF时,可以产生1s的脉冲,在接上一个十进制技术器(我选择74ls161,因为74ls160只能跳9次,影响高频测定),但也保证总的测量周期不变,PPT设计要求里前后要求不一致,无论周期是多少,原理都相同。我就直接用了1s和10s的测量周期,可用switch开关进行选择,为了防止开关打开而产生的跳变或者脉冲宽度误差影响计数,我采用74ls74延迟计数信号,连到阀门上。具体电路如下图:

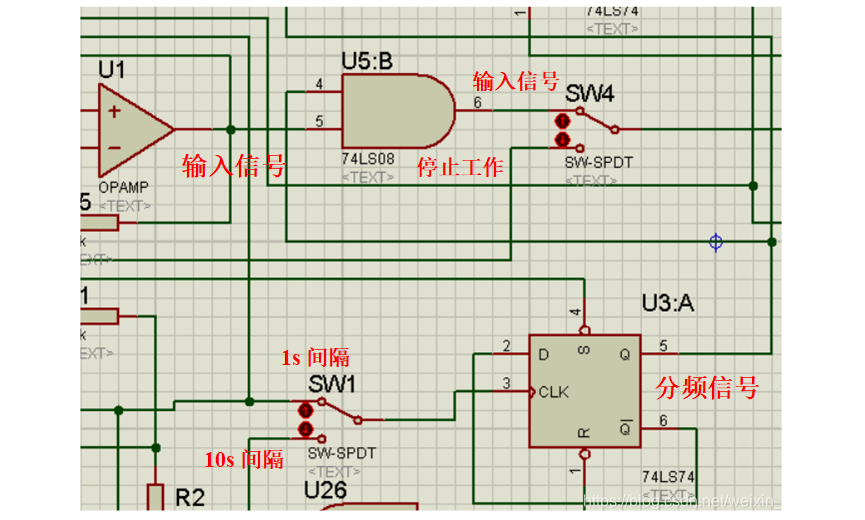

测量控制(阀门)

直接使用与门,一端连接待测信号,另一端连接分频器,为了防止跳变,我还是设置了一个switch开关。

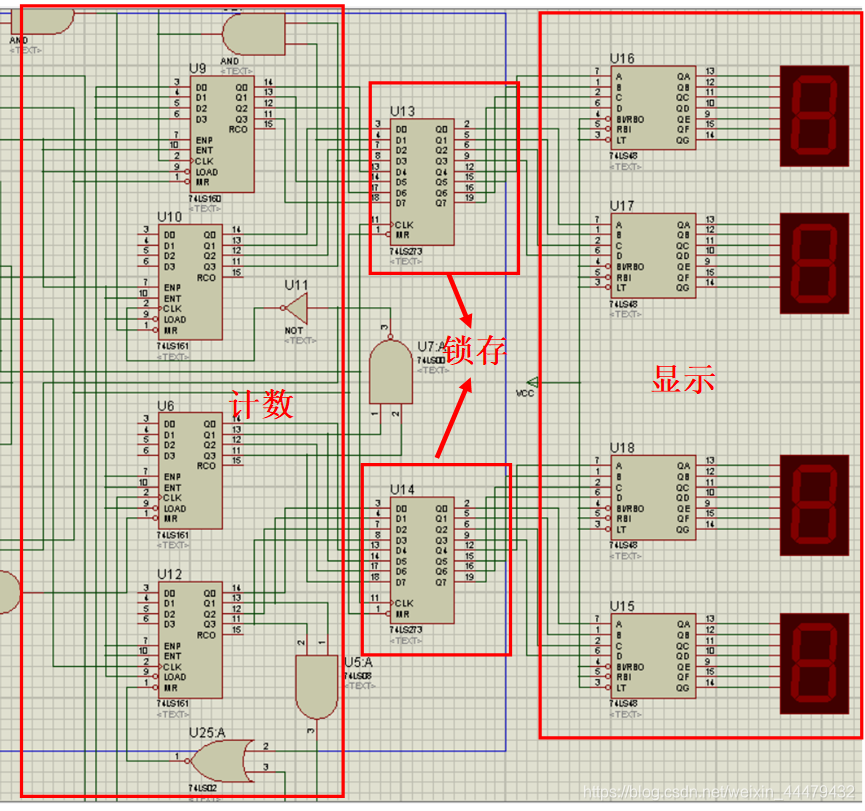

计数及显示模块

这个说简单也简单,说复杂也复杂。通过阀门的信号直接接到异步十进计数器上,由于需要4位显示,所以用了3个74ls161,最高位用74ls160以保证不会溢出(最高位不超过9,因为74ls161是二进制计数器,74ls160是十进制计数器),然后连接到2个锁存器74ls273上,锁存之后通过7段显示译码器74ls48连接到数码管上。这个模块只需注意清零和进位的逻辑关系即可,但是电路连接复杂,具体如下:

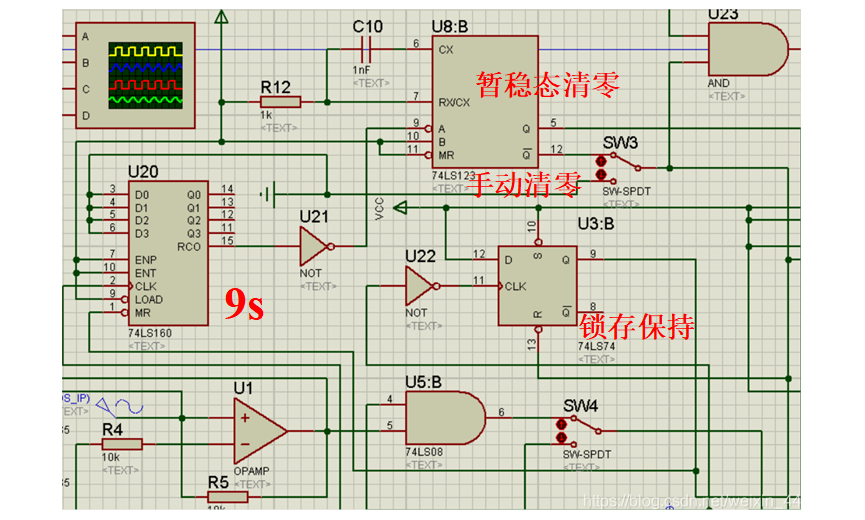

读数保持和清除

按照要求保持10s,这就意味着锁存器clk端要在计数完成后保持一段时间的高电平,时间为十秒钟。然后马上清零,用到两个单稳态触发器,可以使用555时基器件也可以用74ls123单稳态触发器,我利用了秒信号触发器部分,再连一个74ls160,虽然是9s但是问题不大,尽可能保持电路的简洁。

74ls160进位端输出的高电平置反之后给到74ls123,通过查阅资料,得知单稳态触发器有一段时间很短的暂稳态。因为我需要的是低电平清零信号,所以暂稳态是低电平,而稳态情况下是高电平,正好符合计数的74ls161和74ls160清零端的工作要求,另外我还用switch开关设置了手动清零。(P.S 当然有些清零端是多种情况下清零的,要用到与门或门非门,但是都是基本逻辑,这里不一一赘述)

值得一提的是,74ls273锁存器的工作原理是清零端MR为低电平清零,而锁存需要MR置高电平的情况下clk为高电平,所以要做到读书保持,需要在阀门关闭的瞬间置高电平来满足锁存需要。我想到了状态机,还是使用74ls74,将D端直接接高电平,在清零信号没来之前,只要计数一终止,就将高电平送入锁存端并保持不变,等到单稳态触发器出现暂稳态,所有计数器清零了,D触发器和锁存器才清零,这样就达到了读数保持和清零的功能,具体电路图如下:

总结

本电路由于电脑硬件设备的限制,随着频率升高误差会越来越大,程序也越来越卡,1s的周期可能要很长时间才会发生跳变,但是低频段误差不大。毕竟这是简易测频计,精度没办法保证。本文仅供参考,电路还有很多可以优化的方法,不要被一种方法限死。

如果有疏漏或者错误的地方还请指正,如果能够帮助到你,请给我点个赞。

祝各位学业有成。