Design Compiler(以下简称DC)是Synopsys公司用于做电路综合的核心工具,可以将HDL描述的电路转换为基于工艺库的门级网表。本系列主要介绍综合相关的知识以及DC工具的使用。

Verilog编码效率的高低是综合后电路性能高低的决定性因素,两种不同风格的编码,即使它们所表达的逻辑功能一下,也会产生出大不一样的综合结果。就算综合工具运用的再好,也不能完全依赖它把一段编码很差的代码综合出一个像样的电路来。本节将通过大量的实例介绍综合时Verilog的各种语言结构(always、if、case、loop等等)到门级的映射。这些语言结构是在编写Verilog代码的时候经常用到的一些基本结构,希望通过分析他们与门级网表之间的对应关系,大家能够对什么样的语句能生成什么样的具体电路有个初步的认识。

编写用于综合的HDL代码的三个原则:

①编写代码的时候注意代码综合后大概的硬件结构,不写不可综合的语句;

②编写代码的时候注意多用同步逻辑,并将异步和同步逻辑分开处理;

③编写代码的时候注意代码的抽象层次,多用RTL级的描述。

1、always语句的综合

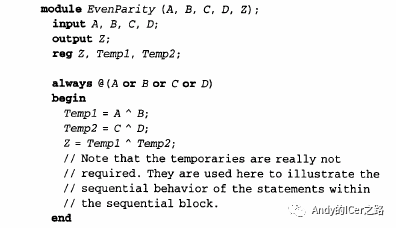

always语句用来描述电路的过程行为(procedural behavior), 表示当事件列表中的状态发生变化时,执行语句体中的语句。下面是一个包含过程赋值的always语句的例子。

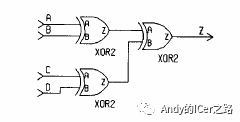

电路综合后的网表如下图所示:

使用always语句描述组合电路要注意的是:在该语句中读入的所有变量都需要出现在事件列表中(对Verilog语言而言是指”@”符号之后的信号),否则可能会得不到用户期望的结果。

2、If语句的综合

if 语句用于描述受条件控制的电路,下面是一个例子: