时钟约束sdc常用的命令有:

creat_clock

creat_generated_clock

set_clock_uncertainty

set_clock_groups

时钟的三要素:Waveform ,uncertainty 和clock group

creat_clock

主要定义一个clock的source 源端,周期和信号上升沿下降沿的时间点,例如:

这个时钟描述成的sdc语句就是

creat_clock -name SYSCLK -period 20

-waveform {0 5}[get_ports2 SCLK]

waveform 后面跟的是上升沿的时间点,如果没有指定默认waveform为{0,period/2}

creat_generated_clock

generated clocks 是另外一个重要的时钟概念:

genreated clocks 是从master clock 中取得的时钟定义,master clock 就是creat_clock 命令指定的时钟产生点,如图:

我们一般把时钟的源头定义为creat_clock ,而分频时钟则会定义为creat_generated_clock ,generated clock 并不会产生新的clock domian ,而且定义generated clcok 后,clcok path 的起点始终位于master clcok,这样source latency并不会重新计算,这就是定义generated clcok 的优点所在。

Virtual Clock

craat_clocok ,creat_generated_clock 都是real clock ,而virtual clock 则不挂在任何port或者pin上,只是虚拟创建出来的时钟。

//定义虚拟时钟

creat_clock -name VCLK -period 10 -waveform {0 5}

我们通常会把input /output delay 挂在virtual clcok上,因为input/output delay 约束本来就是指片外的时钟,所以挂在虚拟时钟上比较合理,当然如果要省事情,直接挂在real clock 上也是可以的。

set_clock_uncertainty

主要定义了clcok信号到时序器件的clock端可能早到或者晚到的时间,主要是用来降低jitter(时钟抖动对有效周期的影响)。值得注意的是,在setup check中,clock uncertainty是代表着降低了时钟的有效周期;而在hold check中,clock uncertainty是代表着hold check所需要满足的额外margin。

set_clock_groups

定义完时钟后,我们也需要通过设置clock group来确认各个时钟之间的关系。这是很重要的一步,因为通常我们还需要做cross domain check,如果clock group设错了,会导致整个STA检查错误。一般有三个选项:asynchronous,physically_exclusive和logically_exclusive。

asynchronous代表两个异步的clock group

physically_exclusive代表两个clock group在物理意义上相互排斥,比如在一个source pin上定义了两个时钟。

logically_exclusive代表两个clock group在逻辑上相互排斥,比如两个clock经过MUX选择器。一个简单的例子:

set_clock_groups -physically_exclusive

-group {CLK1 CLK2} -group {CLK3 CLK4}

为了判别划分时钟组,将不同的时钟划分成以下两类:

a. Synchronous Clocks

当两个时钟间的相位是固定的,则可以称这两个时钟为同步时钟(synchronous clock)。一般同源,如由同一个MMCM or PLL产生的两个时钟可以称为同步时钟。因此可以将主时钟和与之对应的衍生时钟约束成同一个时钟组。

b. Asynchronous Clocks

无法判定两个时钟间相位时,则可以称这两个时钟为异步时钟(asynchronous clocks)。两个来自不同晶振的时钟,一定是异步时钟。通常情况下设计中不同的主时钟肯定是异步时钟,因此可以将这两个主时钟及其衍生时钟约束成不同的时钟组。

对于异步时钟,由于其两个时钟间相位不固定,时序分析的结果定然不确切,因此这部分的分析可以通过设置时钟组约束忽略,但是这并不意味着这部分的设计能工作正常(使用动态时序分析);对于异步时钟间的设计,必须做跨时钟域处理,避免亚稳态的产生。

笔试 virtual clock 例子

有一电路图,假设输入IN 的input delay 恒定为1ns:

可以把输入端挂在virtual clock 上,红色虚线表示关键路径。

笔试 generated clock 例子

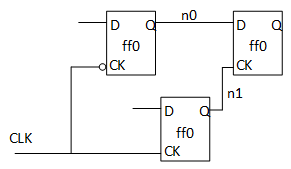

如下电路中,ff2的CK和D之间,是同步还是异步关系,该电路是否有时序风险?

该电路中有三个DFF,一个CLK源。可以认为是同步关系

FF0.CK来自CLK的取反;

FF1.CK来自CLK;

FF2.CK来自FF.Q。属于CLK的分频,可以定义为CLK的generated-clk。

假设数据D端也同样来自CLK,那么它们三个DFF之间的时序路径(timing arc)依然可以由STA(静态时序分析,不能分析异步时钟域)工具保证。

理论上:同一个时钟分组(clock group)是同一个时钟域。

参考:https://www.sohu.com/a/218980533_99933533