FPGA开发中,数据采集、数据分析场景下需要用对高速ADC数据缓存,FPGA片内RAM无法做到大的容量,基于MIG IP做了个DDR3映射成FIFO的模块,以完成高速、量大的数据缓存应用。

背景和选择

part1

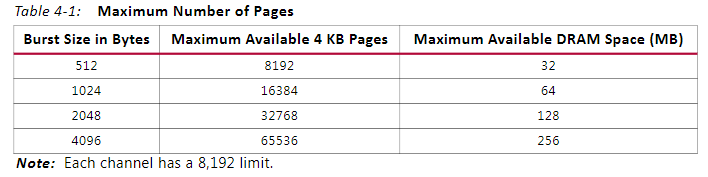

官方也提供了类似功能的IP:AXI Virtual FIFO Controller,如果你需要多通道,该方案倒是比较不错,最大可支持到8个通道,但是容量嘛,支持情况如下图,Note注意到,每个通道最大也就32MB(8192*4K)的容量,这个在某些场合就不适用了。

part2

换个路子试试,找了个 AXI Memory Mapped to Stream Mapper,mm2s是不是能满足应用呢?贴出overview的一段谷歌翻译,好像我会错意了,该模块要成对使用,并且把地址什么的也压到AXIS接口去了,看来不是我们想要的。

AXI内存映射到流映射器IP(axi_mm2s_mapper)的功能是将AXI4内存映射(AXI4-MM)事务封装到一对AXI4-Stream(AXI4-S)接口上。这允许使用面积通常较小,频率更快的AXI4-S组件,并允许系统设计具有更大的灵活性。 AXI内存映射到流映射器IP旨在与成对使用,一对将AXI4-MM事务转换为AXI4-Stream事务,另一半以相反的操作执行以扩展AXI4-S事务到AXI4-MM事务。 AXI4-MM写地址,读地址和写数据通道映射到一个AXI4-S主接口,而读数据和写响应通道映射到一个AXI4-S从接口。通过及时复用两个AXI4-S接口,它们可以一起承载五个AXI4-MM通道。

VFIFO特性说明

- 通道数:1

- 接口 AXI Stream (不支持Last、 Keep)

- FIFO容量:1GB(DDR3容量)

- 输入输出异步时钟:支持

- 测试平台:黑金开发板AX7z035

- 开发环境:vivado19.1

DDR3带宽的计算

内存带宽计算公式:带宽=内存核心频率×内存总线位数×倍增系数

6400MB = 200 X 4 X8

内存时序

这个带宽能不能达到,内存时序没做细研究,对我来说够用了。映射成VFIFO,读写时序切换带宽也略有损失,如果比较要求高的话可以提高busrt_length,后面会提及。

设计框图

-

match_fifo(**X**)

- 用于位宽适配,DDR3端的位宽为256bit,目前接口采用的128,使用时可根据需求对其进行修改,位宽修改是通过AXI4-Stream Data Width Converter实现的;里面的FIFO位宽采用256bit,与DDR端相匹配;

-

mem_manager

- 内存管理主要实现了读写地址管理,读写控制。实现方式Ring,循环缓冲区;

-

mem_burst

- DDR3 native接口控制,实现burst模式的读写,读写长度受限于match_fifo的长度;

-

ddr3

实现描述

DDR3映射为VFIFO,并采用AXI2-stream的接口封装形式,方便与设计的端逻辑标准接入。如果对LAST、KEEP信号有需求的用户,可以对数据做帧头、帧尾封装,以适应具体需求。

VFIFO实现方式:将内存看做buffer,通过读写地址的控制,实现了循环缓冲区,并增加了empty、half_full、full信号,用于外部使用。其中DDR3的控制采用native接口(AXI4-MM接口还是比较复杂的),采用burst的模式,这样可以减轻状态切换的频次,进而增加了读写带宽。

mem_manager 读写控制,burst_length单次传输长度为FIFO的一半,当输入端match_fifo内的数据长度 > burst_length时,触发写do_tx输入给manager,当输入端match_fifo内的数据长度<burst_length时,触发do_rx信号输入给manager,并且根据产生的empty、full信号,进而控制读写逻辑和读写地址。

如果修改busrt_length,首先注意两点,1、确保读写切换过程中match_fifo不被填满,保证数据不丢失。2、FPGA内部RAM资源有限、增加长度势必考虑整个工程的BRAM使用情况。

小提示:

AXIS FIFO的实际长度>=设计参数的长度。这个很好理解,每个BRAM块的大小为18K或36K,为了保证你设计的长度,BRAM容量块肯定>=设计容量,xilinx IP对其是全使用的。这就造成仿真下与实际应用中,FIFO填满时长度不一致的情况,要以实际测试的为准。

联系方式:1174316744@qq.com