我自己前些天在运行项目时也发生了这个错误,事实上,我很困惑,因为我之前已经破解完成了,为什么有出现这个问题?

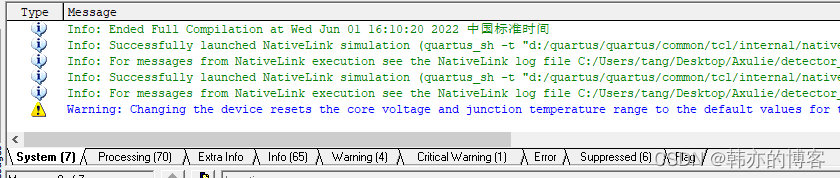

报错提示:

Error(102290): current license file does not support the EP2C5F256I8 device

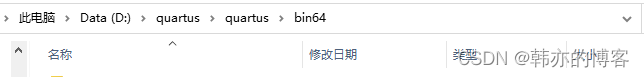

后来发现了原因,实际上应该算是破解不完全的原因,我是64位Quartus,而我破解的时候,没有去关心这个,破解的是32位的Quartus,故出现了问题。

知道了原因后就可以解决了,只需要在破解一次,这次在生成破解文件时,选择的是bin64文件夹下的文件即可。

问题解决: