/*

如果在两个模块之间传输数据,两个模块之间的处理速率不同,会导致采集数据的遗漏或错误

在他们之间加一个数据缓存器,所有数据先经过缓存器缓存,再输入数据接送模块

*/

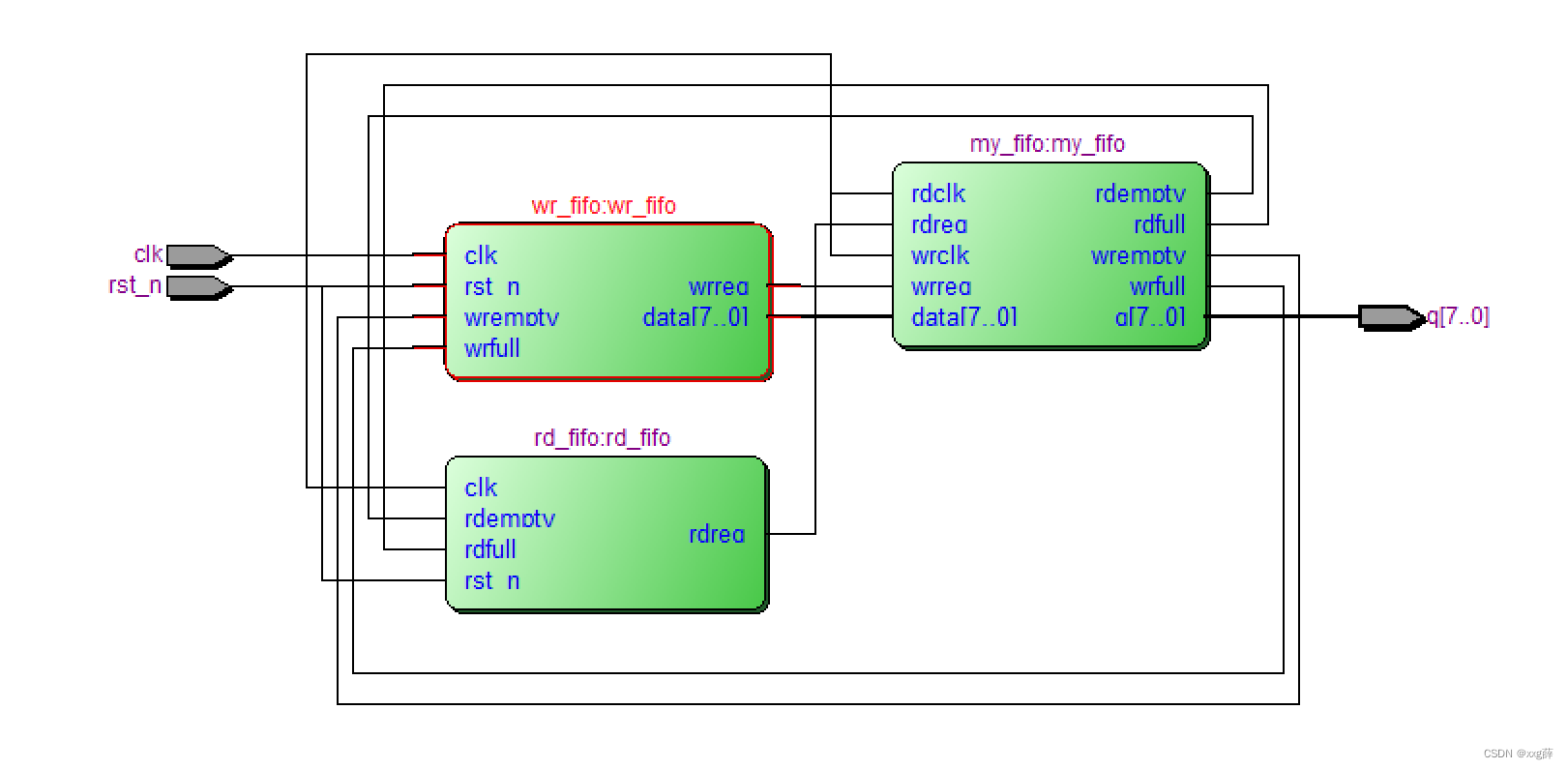

/*创建两个模块,一个 作为发送模块,一个作为接受模块,发送模块检测到 fifo为空开始向fifo写数据

直到fifo写满为止,数据接受模块检测到fifo满,则从fifo中读出数据,直到fifo读空为止

*/

module fifo(

input clk,

input rst_n,

output[7:0] q

);

wire wrreq;

wire rdreq;

wire [7:0]data;

wire wrfull;

wire wrempty;

wire rdempty;

wire rdfull;

wr_fifo wr_fifo(

.clk (clk ),

.rst_n (rst_n ),

.wrfull (wrfull ),

.wrempty (wrempty ),

.data (data ),

.wrreq (wrreq )

);

rd_fifo rd_fifo(

.clk (clk ),

.rst_n (rst_n ),

.rdfull (rdfull ),

.rdempty (rdempty ),

.rdreq (rdreq )

);

my_fifo my_fifo(

.data (data ),

.rdclk ( clk ),

.rdreq (rdreq ),

.wrclk ( clk ),

.wrreq ( wrreq ),

.q ( q ),

.rdempty ( rdempty ),

.rdfull (rdfull ),

.wrempty ( wrempty ),

.wrfull ( wrfull )

);

endmodule

module wr_fifo(

input clk,

input rst_n,

input wrfull,

input wrempty,

output reg[7:0]data,

output reg wrreq

);

reg state;

always@(posedge clk or negedge rst_n)

if(!rst_n)

begin

data<=0;

wrreq<=0;

state<=0;

end

else begin

case(state)

0:begin

if(wrempty)

begin

state<=1;

wrreq<=1;

data<=0;

end

else

state<=0;

end

1:begin

if(wrfull)

begin

state<=0;

wrreq<=0;

data<=0;

end

else begin

data<=data+1;//没有写满时,写入数据

wrreq<=1;

end

end

default:state<=0;

endcase

end

endmodule

module rd_fifo(

input clk,

input rst_n,

input rdfull,

input rdempty,

output reg rdreq

);

reg state;

always@(posedge clk or negedge rst_n)

if(!rst_n)

begin

rdreq<=0;

state<=0;

end

else begin

case(state)

0:begin

if(rdfull)

begin

rdreq<=1;

state<=1;

end

else

begin

rdreq<=0;

state<=0;

end

end

1:begin

if(rdempty)

begin

rdreq<=0;

state<=0;

end

else begin

rdreq<=1;

state<=1;

end

end

default:state<=1;

endcase

end

endmodule

`timescale 1ns/1ns

module fifo_tb();

reg clk;

reg rst_n;

wire[7:0] q ;

initial begin

clk=0;

rst_n=0;

#100.2;

rst_n=1;

end

always #10 clk=~clk;

fifo fifo(

.clk(clk),

.rst_n(rst_n),

.q (q)

);

endmodule