最开始在学习SV的时候,碰到interface的使用并没有过多的在意,只是了解clocking block是为了解决竞争问题。然而在后续使用clocking block的过程中,总会碰到一些时序错位的问题。

如下,通过简单的例子来表述下clocking cb中对应的input delay和output delay的作用。

interface代码

in 为dut的输入信号;out为dut的输出信号。

interface();

logic clk;

logic [7:0] in;

logic [7:0] out;

clocking cb @(posedge clk);

default input #5ns output #10ns;

input out;

output in;

endclocking

endinterface

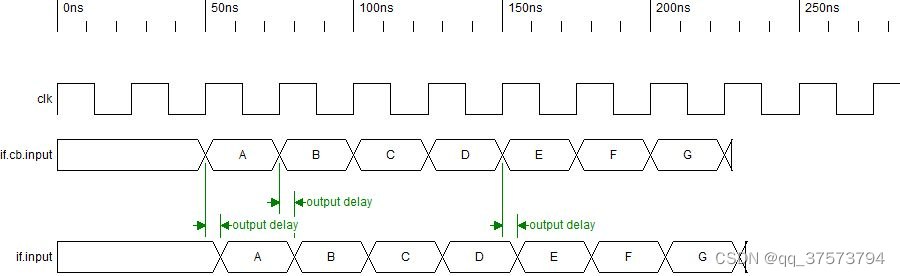

output delay

在driver中对if.cb.in进行激励,连接到dut上真实的信号为if.in,两者的延迟就是output delay,对应上述代码即为10ns。

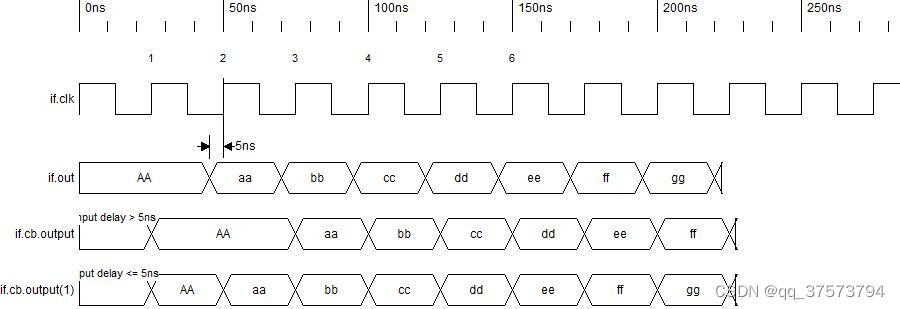

input delay

如上图,DUT输出if.out与时钟沿始终有一个5ns的提前量:

- 当input delay大于5ns,意味着时钟沿2采样的提前量大于5ns,因此在时钟沿2的位置采样仍为AA;

- 当input delay不大于5ns,同样时钟沿2为例,采样提前量不大于5ns,因此时钟沿2的位置采样为aa。

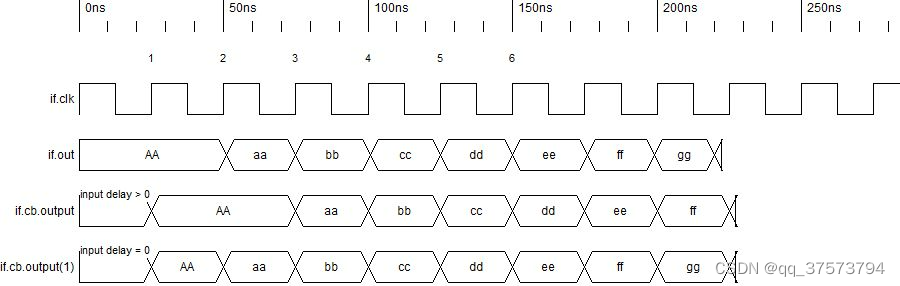

上述波形为说明采样的提前量,使用了异步的始终采样。应用中的一般情况下,会使用相同时钟进行采样,对应如下时序。

如上可以看到,对于input delay为0的情况下,if.out和if.cb.out保持相同时序。