Xilinx BUFGMUX使用注意事项

最近使用Xilinx FPGA的时候,需要用到一个外部时钟和一个PLL产生的时钟,可以通过外部SWICH进行时钟的切换,觉得这种方式可以通过原语例化完成。

原语

果不其然,在原语示例中找到了类似的模块:

// BUFGMUX : In order to incorporate this function into the design,

// Verilog : the following instance declaration needs to be placed

// instance : in the body of the design code. The instance name

// declaration : (BUFGMUX_inst) and/or the port declarations within the

// code : parenthesis may be changed to properly reference and

// : connect this function to the design. All inputs

// : and outputs must be connected.

// <-----Cut code below this line---->

// BUFGMUX: Global Clock Mux Buffer

// Kintex-7

// Xilinx HDL Language Template, version 2018.3

BUFGMUX #(

)

BUFGMUX_inst (

.O(O), // 1-bit output: Clock output

.I0(I0), // 1-bit input: Clock input (S=0)

.I1(I1), // 1-bit input: Clock input (S=1)

.S(S) // 1-bit input: Clock select

);

// End of BUFGMUX_inst instantiation

具体原语寻找的路径如下:

Tools -> Language Templates:

找到Device Primitive Instantiation,在对应的设备下选择Clock Components中的Clock MUXes选项:

使用

找到原语后,就立刻在工程中进行了例化,通过SW开控制切换时钟源的选择输出。

但是,在使用的时候出现了问题,无论SW怎么设定,输出的时钟在仿真中一直处于Hiz状态,这与之前的理解不符合。

解决这种问题最直接的方法,就是去查找手册,看一看这个BUFGMUX到底是如何进行工作的,是不是有一些限制条件。

BUFGMUX介绍

ug472_clocking_resources中page43 开始对BUFGMUX的描述如下:为了方便,我直接翻译成拙略的中文了,如有疑问,以原文为准。

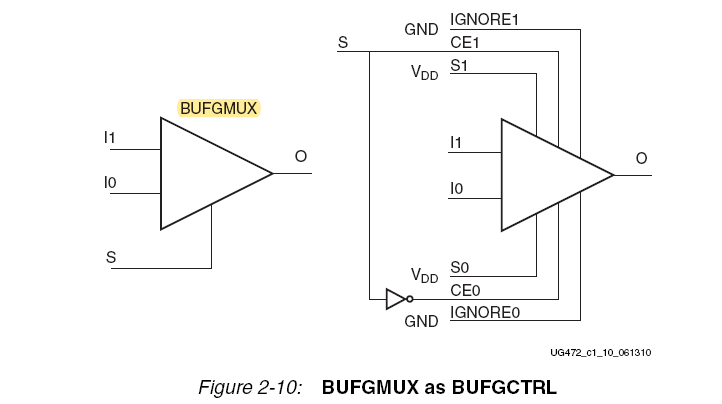

BUFGMUX is a clock buffer with tow clock inputs, one clock output, and a select line. This primitive is based on BUFGCTRL with some pins connected to logic High or Low.Figure 2-10 illustrates the relationship of BUFGMUX and BUFGCTRL.

BUFGMUX是一个有两时钟输入,一个时钟输出,和一个选择信号的时钟缓冲。它的原语是在BUFGCTRL的基础上将某些引脚连接在逻辑高或者逻辑低。图2-10表明了BUFGMUX和BUFGCTRL的关系:

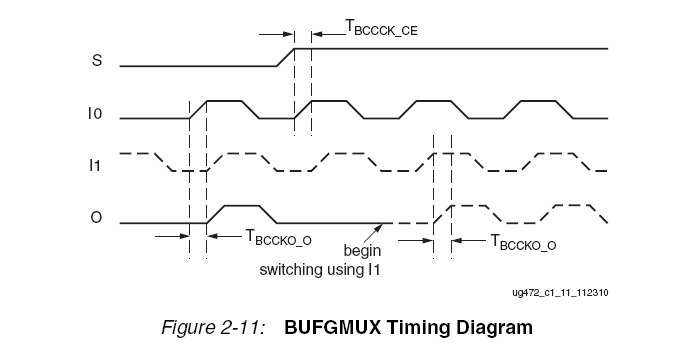

由于BUFGMUX用CE引脚作为选择引脚,当进行选择时,建立时间必须要被满足。忽略这个建立时间会导致结果进入故障。BUFGMUX的切换条件与BUFGCTRL的CE引脚一致,图2-11展示了BUFGMUX需要的时序图:

在图2-11中:

- 当前时钟为I0;

- S信号为高电平有效;

- 如果I0当前状态为高电平,多路选择器会等待I0直到变为低电平;

- 一旦I0变为低电平,多路先择期输出就会维持在低电平,直到I1从高电平变为低电平;

- 当I1从高电平变为低电平时,输出就切换到了I1;

- 如果满足建立和保持时间,不会有故障或者短的脉冲在输出端口出现。

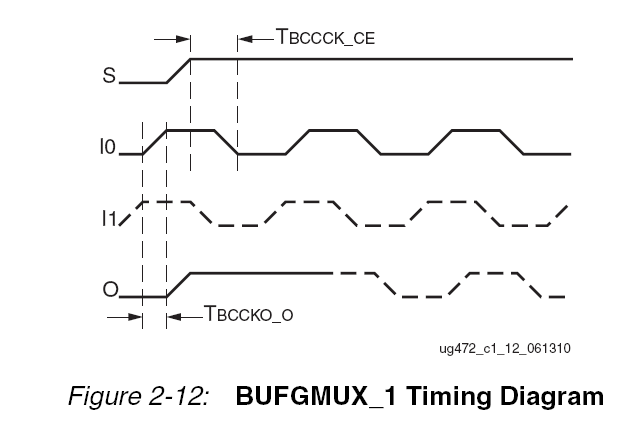

BUFGMUX_1是上升沿敏感,若开关在I0时钟高电平切换时,输出时钟优先保持高电平,直道切换为I1的时钟,图2-12展示了BUFGMUX_1的时序:

在图2-12中:

- 当前时钟为I0;

- S信号为高电平有效;

- 如果I0当前状态为低电平,多路选择器会等待I0直到被拉高;

- 一旦I0被拉高,多路复用器会维持高电平知道I1从低电平变为高电平;

- 当I1从低电平变为高电平时,输出就切换到了I1;

- 如果满足建立和保持时间,不会有故障或者短的脉冲在输出端口出现。

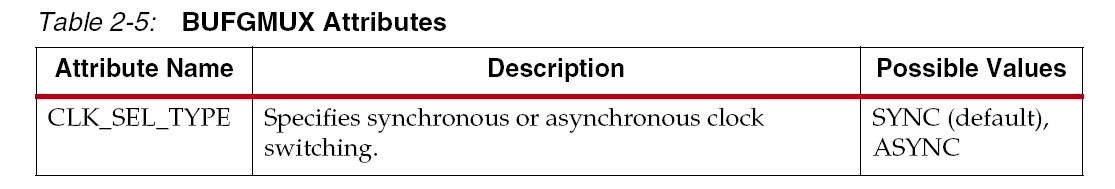

BUFGMUX Attributes

BUFGMUX也是有属性参数的,见下图:

可以看出默认的I0和I1时钟是同步时钟,如果I0和I1为异步时钟,需要选择属性为ASYNC。

BUFGMUX_CTRL

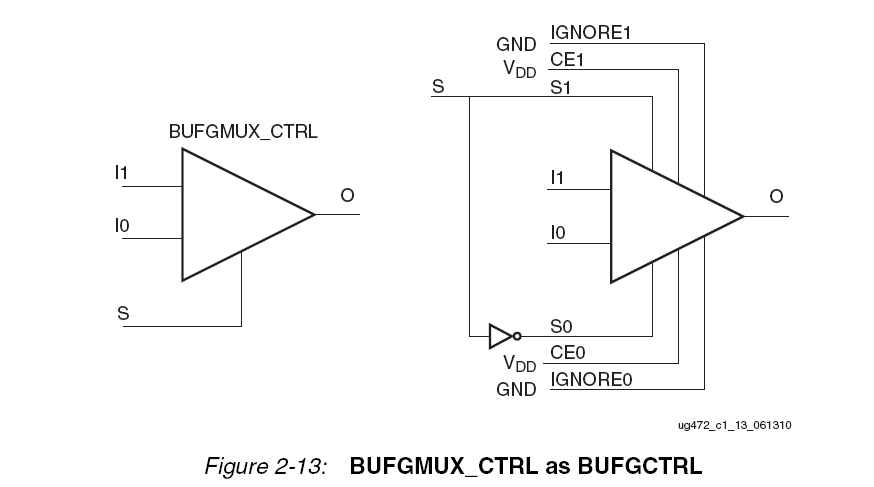

之前介绍了BUFGMUX的原语是在BUFGCTRL的基础上将某些引脚连接在逻辑高或者逻辑低。自然也要介绍一下BUFGMUX_CTRL。

BUFGMUX_CTRL是一个有选择信号的两时钟输入,一时钟输出时钟缓冲。这个原语是在BUFCTRL的基础上将某些引脚连接到高电平或低电平。图2-13展示了BUFGMUX_CTRL和BUFGCTRL的关系。

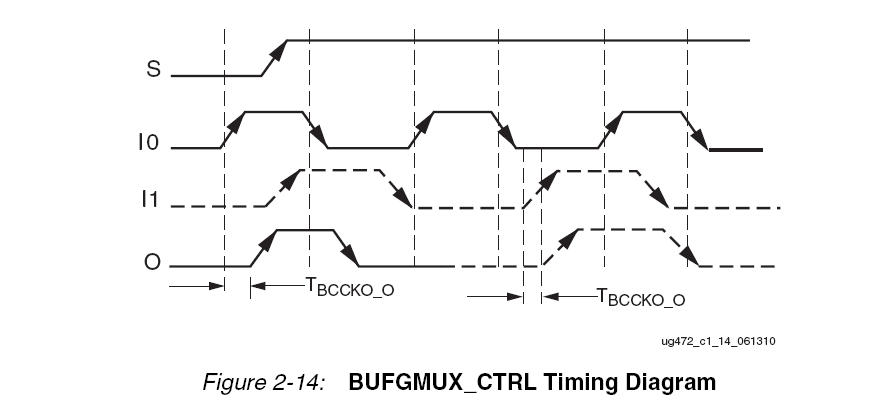

BUFGMUX_CTRL使用S引脚作为选择引脚。S在任何时候开关,都不会导致故障。S的建立和保持时间决定了输出端口是否将额外的上一个时钟的多余脉冲在切换到新时钟的时候输出。

如果S像图2-14中那样改变,在建立时间TBCCK_S之前,且I0从高电平转换为低电平之前,输出端不会传递I0多余的脉冲。

如果S改变在S的保持时间,那么输出就会传递出I0的一个多余脉冲。

所以如果S在不不满足建立和保持时间的情况下改变,输出就会多一个额外的脉冲,但是并不是故障。在任何情况下,输出都会在I0,I1中较慢的时钟三个周期内传递出去。

S0和S1的建立保持时间要求取决于时钟下降沿,而不是CE0和CE1的上升沿。

BUFGMUX_CTRL的转换条件与BUFGCTRL的S引脚相同,图2-14表示出BUFGMUX_CTRL的时序。

BUFGMUX_CTRL原语的其他功能如下:

- 在配置(FPGA上电配置?)之后对I0和I1进行与选择。

- 在配置之后可以设定输出为高电平或者低电平为初始值。

附加的使用模型

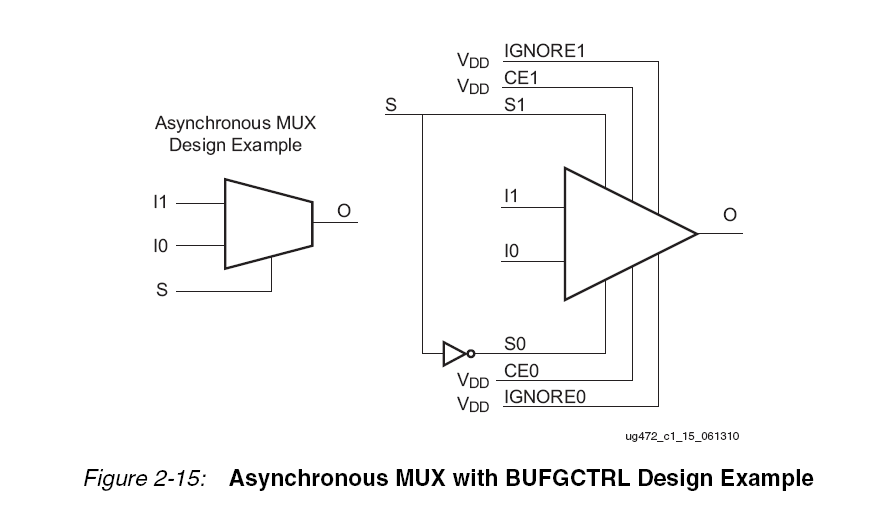

使用BUFGCTRL做异步时钟选择

在某些应用情况下,需要理科切换输入时钟,或者忽略BUFGCTRL的边沿敏感。

其中一个例子就是假设一个时钟不再进行切换了(我理解为时钟保持H,L,X,Z状态)。这种情况下输出时钟也不会正确的切换,因为BUFGCTRL永远也检测不到时钟的下降沿了。

这种情况下就要使用异步MUX,图2-15展示了BUFGCTRL与异步MUX的设计例子。

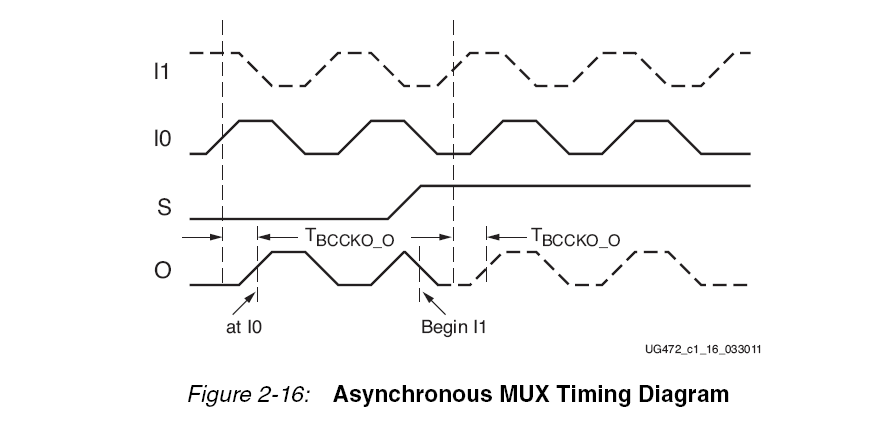

图2-16展示了异步MXU的时序。

在图2-16中:

- 当前时钟来自I0;

- S为高电平有效;

- 输出时钟立刻切换为I1;

- 当Ignore信号拉高时,故障保护就会无效;

带有时钟使能的BUFGMUX_CTRL

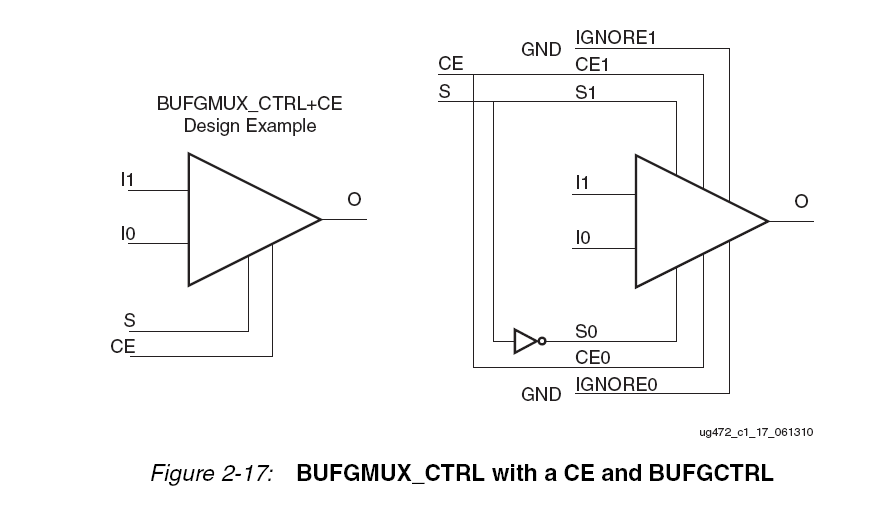

带有时钟使能和BUFGCTRL的BUFGMUX_CTRL配置允许你在即将到来的时钟输入间选择。

如果有必要,可以通过时钟使能信号来使得输出无效。图2-17展示了BUFGCTRL的方法设计案例。

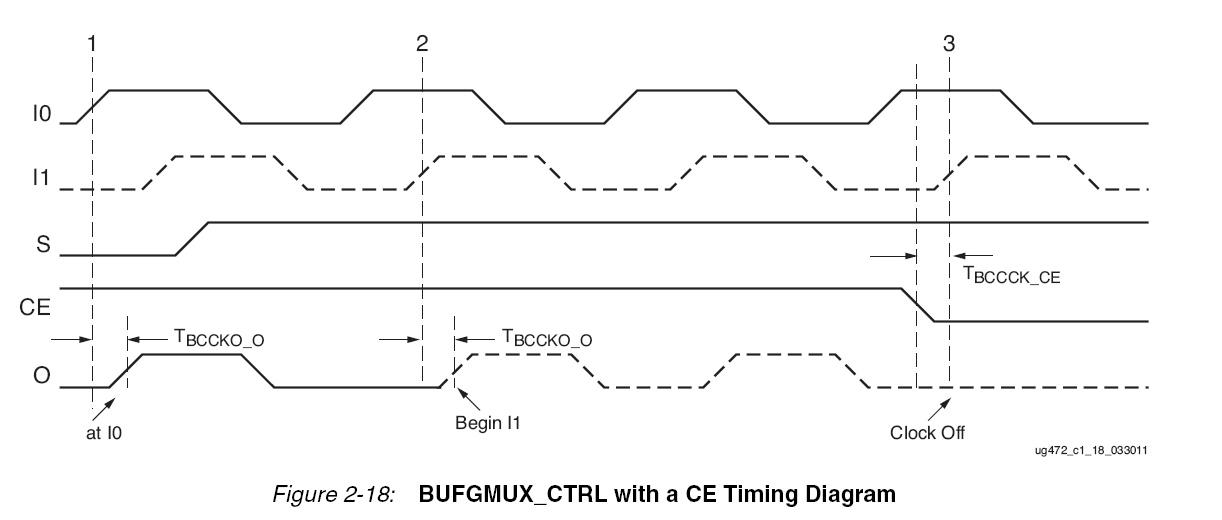

图2-18展示了时序图:

在图2-18中:

- 当前时刻为事件1,输出O使用I0;

- 在事件2之前,S被拉高;

- 在事件2之后的TBCCKO_O 时刻,输出O使用I1。这发生在I0从高电平到低电平的变换,和I1从高电平到低电平变换完成之后。

- 在事件3之前的TBCCCK_CE 时刻,CE被拉低。为了避免任何输出时钟的小故障,直到I1从高电平转换为低电平完成后,输出时钟转换并一直保持为低电平。

问题解决

在自己的设计中,有一个时钟I0是外部输入,另外一个I1为FPGA的PLL产生;若外部时钟不是一直存在,相当于I0为(H,L,X,Z某一状态),所以此时例化BUFGMUX的时候需要加上异步的属性:

BUFGMUX #(

.CLK_SEL_TYPE("ASYNC")

) BUFGMUX_inst (

.O(O), // 1-bit output: Clock output

.I0(I0), // 1-bit input: Clock input (S=0)

.I1(I1), // 1-bit input: Clock input (S=1)

.S(S) // 1-bit input: Clock select

);

这样,在没有I0时钟输入的时候,S为高电平选择I1也会有时钟输出。

参考链接

Xilinx FPGA中BUFGMUX使用注意事项

2021-05-09.