一、.COE格式文件生成

由于Quartus ii软件ROM用的是mif格式的文件,且可以用软件Guagle_wave生成正弦波、三角波、锯齿波。我们可以利用这个软件先生成数据,然后再将其转化为符合COE格式的文件。具体请参考以下步骤:

1. 先打开Guagle_wave软件;

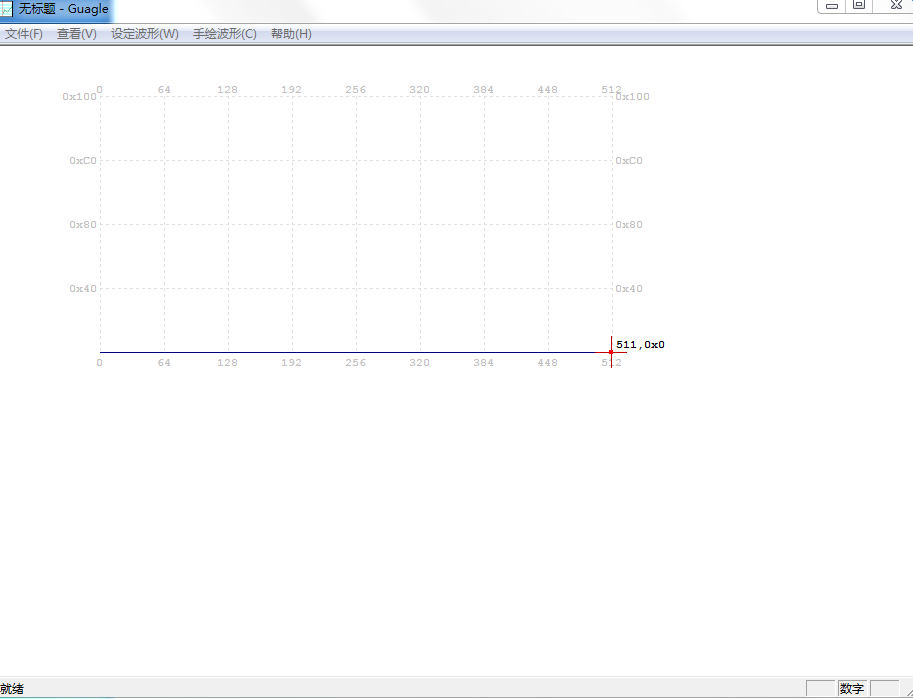

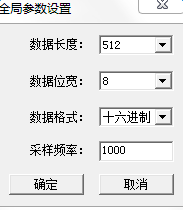

2. 菜单栏-->查看-->全局参数设定(如下图所示):

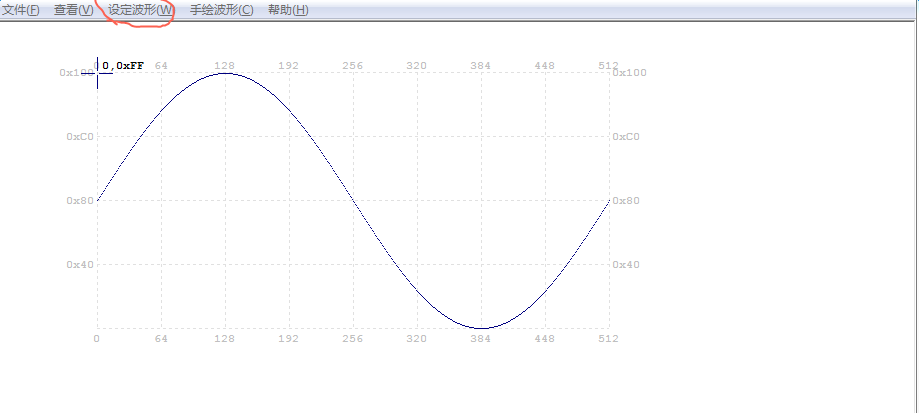

3. 设定波形-->我们选择正弦波(如下图):

4. 保存为 zhengxian.mif 文件

5. 用文本编辑器打开zhengxian.mif 文件,我用的是Notepad++,然后将所需数据复制出来,不要都复制,只复制数据部分(如下图所示):

6. 新建一个txt文本,将以上数据复制进去,注意:如果深度是512的话,就有512个数据;

7. 然后在文档最前加入以下两行代码:

memory_initialization_radix=16; //该处16代表进制

memory_initialization_vector=

并且把数据的分号都变为逗号,最后一组数据后边是分号。然后将文本保存为.coe格式(自己敲个xxx.coe就ok了)

8. 由于coe格式文件最初为unix系统,在windows系统中需要转化以下格式:这里需要用到Ultraedit文本编辑器

9. 用Ultraedit打开以上自己制作的xxx.coe文本,然后转化以下,选择 转换--DOS到Unix,然后保存为xxxx.coe,这样coe文件制作完成,可以往ROM里添加了;

---------------------------大功告成!!!!!!!---------------------------------------------------------------------