1、概述

在高速电路设计中一块单板上常存在多种电源(3.3V,1.8V,1.2V,1.0V,0.9V,0.75V等),有时光是对FPGA供电就需要五六种电源,为了便于使用往往用户只需要提供一种或几种电源,然后经过板上电源模块转换到各个目标电源进行使用,电源架构一般有集中式电源架构和分布式电源架构。

1、集中式电源架构

即输入电压直接通过隔离DCDC模块转换到各个目标电压,但成本高,占用PCB面积大。

2、分布式电源架构

输入电源经过隔离DCDC电源转换到中间电源再经过非隔离电源模块转换到最终目标电压,节约成本,PCB面积占用相对小,但是效率较低。

在高速电路设计中常常使用分布式电源架构。

2、 电源类型

1、整流:将交流电转换为直流电的过程。

2、斩波:把某一电平的直流电转换成另一电平的直流电的过程。

3、逆变:将直流电转变为交流电的过程。

4、变频:把某一频率的交流电转换成另一频率的交流电的过程。

在单板设计过程中最常见的是斩波类型,即直流转直流电源类型,这类电路通常又分为两种类型电路:DC/DC、LDO。

3、线性稳压电源

3.1、结构

线性稳压电源即LDO,通常由一个工作在线性区的调整管和差值放大器组成,通过R2、R2电阻分压对VOUT进行电压采样,然后送至差值放大器和基准电压比较差值并放大,从而通过控制调整管压降调整数输出电压,从本质上来说是基于反馈的原理。

3.2、参数

对参数的介绍用TI的3A 低压差 LDO tps74401示例:

① 输入电压范围:不同芯片见具体手册。

② 输出电压范围:分为固定输出、可调输出。

③ 最大输出电流:相对DCDC小。

④ 输入输出电压差VDO:与负载电流有关,往往负载电流越大,压差要求越高。

⑤ 功耗:LDO功耗相对DCDC高,应注意散热设计, P=(Vin-Vout) * I 。

⑥ 电源纹波抑止比PSRR:与输入频率、压差、负载电流等有关,表示输出电压受输入电压影响的量。PSRR越大表示输出受输入影响越小。 PSRR=20log[ripple (in) / ripple (out)]

⑦ 线性调整率:输出负载电流一定,输入电压变换对输出电压影响

⑧ 负载调整率:输入电压一定,输出负载电流变化对输出电压变化影响。

3.3、 LDO总结

一般LDO输出电压电流比较小,输出纹波和噪声小,适合用于精密器件如ADC/DAC/晶振/PLL等,(其模拟电源和数字电源通常需要分开供电,模拟电源一般要用LDO供电,数字电源可用DCDC或LDO供,同时模拟地和数字地需要分割处理然后通过磁珠或0R电阻单点连接,目的是减少数字噪声对模拟地干扰,当然也不是严格要求分割,如果数字地比较干净没什么噪声)LDO缺点是功耗较大、效率低只能做降压变换;设计时一般VDO越大PSRR越好,但VDO越大功耗也越大,设计时为了节省功耗VDO不能一味做到很大,需要综合考虑负载电流取合适的VDO;同时还要注意分压电阻取值不是任意的还要满足芯片对偏置电流的要求奥。

4、DCDC电源

4.1、分类

LDO只能实现降压变换,而DCDC可以实现升压、降压、反向等操作,以降压为目的DCDC电源电路称为BUCK电路,以升压为目的DCDC电源电路称为BOOST电路,以反相为目的的电源电路称为BUCK-BOOST电路。

4.1.1、BUCK

BUCK电路由MOS管、续流二极管、LC电路组成,通过PWM波控制MOS管通断实现对电容进行充放电,从而实现开关电源输出,BUCK电路通常VIN>VOUT。

4.1.2、BOOST

BOOST电路由MOS管、续流二极管、LC电路组成,通过PWM波控制MOS管通断实现对电感进行充放电,充电时MOS管导通,MOS管关闭时由于L的自感效应,电流经过续流二极管向负载供电,从而实现开关电源输出,BOOST电路通常VIN<VOUT。

4.2、参数

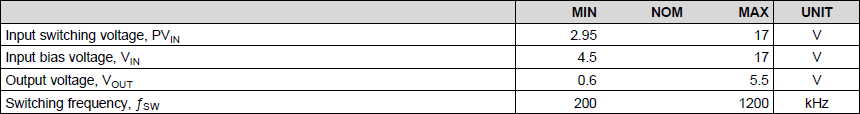

以TI的LMZ31710示例:

① 输入电压范围:不同芯片见具体手册。

② 输出电压范围:一般为可调输出。

③ 最大输出电流:相对LDO更大。

⑤ 功耗:相对LDO功耗小效率高,随电流增大功耗越高。

⑥ 效率:和输出电流电压开关频率相关,根据手册提供曲线图可确定,效率越高说明同等条件下芯片功耗越小,n=输出功率 / 输入功率 = 输出功率 / (输出功率+功耗)。

⑦ 开关频率:一般在KHz-MHz范围,影响后级LDO PSRR参数。

⑧ 纹波:是指电源波动中的低频成分,一般 < 5MHz,由开关频率引起。

⑨ 噪声:是指电源波动中的高频成分,一般 > 5M,通常受随机白噪声和开关频率、周围信号干扰。

4.3、DCDC总结

DCDC作为隔离电源,支持升压降压和反相等变换,可以输出大电流,且功耗低效率高,但是缺点是输出电源纹波大,PCB占面积大。DCDC通常给数字电源供电,对有时序要求的情况,DCDC输入输出有较大时延可以保证时序,而LDO本身是无法保证上电时序的。