文章目录

- 一、赋值

- 二、例化

- 1.大端->大端,小端->小端

- 2.大端->小端,小端->大端

- 总结

近来在学习VHDL时发现其有TO和DOWNTO两种声明位宽的方式,不同方式在赋值操作时存在差异,容易混淆。想来Verilog也存在这种问题,故在此进行一个简单的讨论。

众所周知,在Verilog中声明数据位宽有两种方式:

第一种为DOWNTO方式,这种方式是我们通常使用的声明位宽的方法,在声明时,左侧为高位,右侧为低位,即小端存储。

wire [7:0] DOWN_TO; //声明一个8位的wire型变量DOWN_TO

第二种为TO方式,声明时左端为低位,即大端存储。

wire [0:7] TO; //声明一个8位的wire型变量TO

下面就这两种声明方式讨论其在赋值和例化时的差异:

一、赋值

现在我们对TO和DOWN_TO赋值16进制数AA(二进制:10101010)。

assign TO = 8'haa;

assign DOWN_TO = 8'haa;

直接编译后编译器会提醒我们部分信号时钟为高或低。

可以发现DOWN_TO和TO信号值相等,但各位正好相反。小端存储赋值时高位对高位,大端存储赋值时高位对低位。

二、例化

1.大端->大端,小端->小端

仍然定义小端存储DOWN_TO,大端存储TO,包装成模块。

首先用大端接收大端,小端接收小端:

wire [0:7] TO1;

wire [7:0] DOWN_TO1;

TO_TEST U(

.TO(TO1),

.DOWN_TO(DOWN_TO1)

);

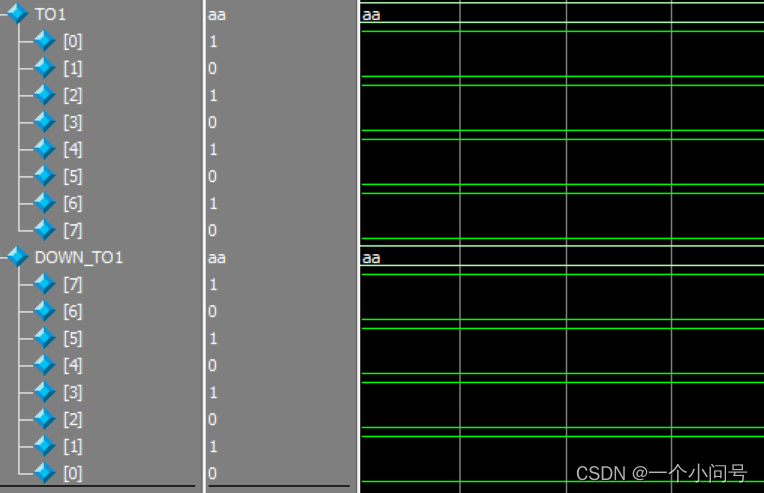

仿真结果如下

结果与上面一致,值相等但各位相反。

2.大端->小端,小端->大端

接下来用大端接收小端,小端接收大端:

wire [7:0] TO2;

wire [0:7] DOWN_TO2;

TO_TEST U(

.TO(TO2),

.DOWN_TO(DOWN_TO2)

);

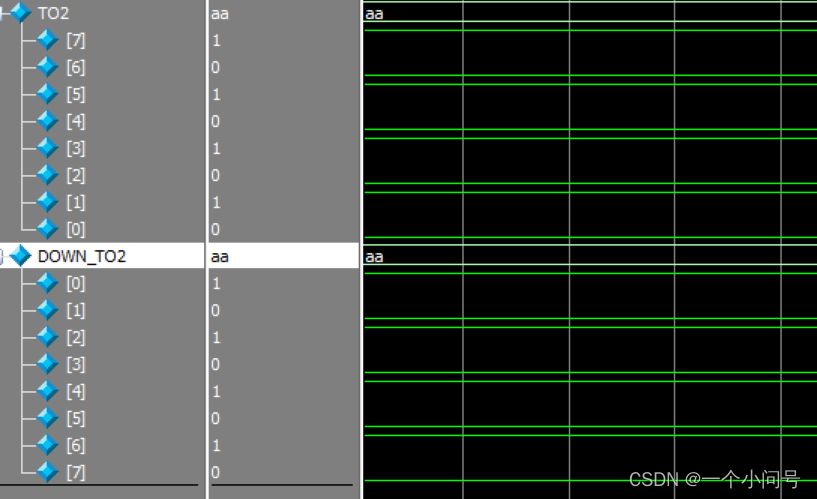

值仍然不变,但TO2由大端变成了小端,DOWN_TO2由小端变成了大端。

总结

Verilog中有大端和小端两种位宽定义方式,在赋值时需要注意两种方式的差异(反转数据或许用得着)。

在进行例化时,值将会正常传递,但存储方式总取决于最外层的定义。

本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有涉嫌抄袭侵权的内容,请联系:hwhale#tublm.com(使用前将#替换为@)