3.0 接口和信号描述

3.1 SD/eMMC控制器

| 标准 | 注释 |

| SD规范Part A2 SD Host控制器标准规范V4.00 | |

| SD规范Part 1 物理层规范V4.00 | |

| SD规范Part E1 SDIO规范V4.00 | 支持SD4.0规范,没有UHS-II |

| 嵌入时多媒体卡(e-MMC),电气标准5.1 | |

SD/eMMC控制器能同SD/eSD、SDIO卡和eMMC设备连接,它有一个直接的内存接口,能发起在内存和外部卡之间的数据传输,SD/eMMC控制器支持2个不同的总线协议:SD和eMMC协议。它有一个APB从接口用来存取配置寄存器,为了存取Micro Boot 的iRAM,SD/eMMC控制器依赖内存控制器中的AHB重定向仲裁器。

特点:

l 支持eMMC/eSD卡的8bit数据传输。

l 支持SD卡的4bit数据传输。

l 在1-bit、4-bit、8-bit SD模式,允许卡中断host。

l 支持SDIO卡的读等待控制,悬挂/重新进行操作。

l 通过停止SD时钟,支持FIFO过运行和欠运行条件。

l 支持寻址大的容量SD3.0或SD-XC卡,高达2TB

TX1提供这个控制器的两个实例,SDCARD接口用来支持SD卡插座,SDIO接口可用来支持不同的兼容外设,比如像第二个Wi-Fi/BT控制器,SD/SDIO控制器支持缺省的和高速模式,以及高低电压范围。

表7 SD/MMC控制器I/O能力

| 控制器 | 总线宽度 | 支持的电压(V) | I/O总线时钟 | 最大带宽(MBps) |

| SDCARD | 4 | 3.3, 1.8 | 208 | 104 |

| SDIO | 4 | 3.3, 1.8 | 208 | 104 |

表8 SD/SDIO信号描述

| 信号名称 | 类型 | 描述 |

| SDCARD_CLK, SDIO_CLK | Output | SD/SDIO/MMC时钟 |

| SDCARD_CMD, SDIO_CMD | Bidirectional | SD/SDIO/MMC命令 |

| SDCARD_DAT[3:0], SDIO_DAT[3:0] | Bidirectional | SD/SDIO/MMC数据总线 |

| SDCARD_WP | Input | SD写保护 |

| SDCARD_CD# | input | SD卡检测 |

3.2 SATA控制器

| 标准 | 注释 |

| SATA 版本3.1 | 包括所有的错误,ENC和TP,除了DHU(direct head unload直接的头卸载) |

| SATA高级Host控制接口(AHCI)规范,版本1.3.1 | |

SATA控制器使能一个从JetsonTX1到外部SATA设备的控制通道,SSD/HDD/ODD驱动能被连接,控制器支持二代驱动器的最大吞吐率。

特征:

l 端口复用支持

n 基于交换的命令(CBS)

l 支持的电缆和连接器

n 标准的内部连接器

n 内部微连接器

n mSATA连接器

n BGA SSD接口

n 不支持:外部连接器(eSATA)、USM、内部LIF-SATA

表9 SATA信号描述

| 信号 | 类型 | 描述 |

| SATA_RX+/- | Input | 接收数据,差分模拟输入 |

| SATA_TX+/- | output | 发送数据,差分模拟输出 |

3.3 显示接口

TX1显示控制器复合体(DisplayController Complex)集成了2个MIPI-DSI接口和2个串行输出资源(SOR),以收集(collect)来自显示管线(Display pipeline)的输出像素、将它们格式化/编码成期望的格式,然后以流的形式发布到不同的输出设备,SOR由一些独立的资源组成,能用于不同的显示设备比如HDMI、DP或eDP。

3.3.1 MIPI显示串行接口(DSI)

显示串行接口(Display SerialInterface:DSI)是并行MIPI DPI和DBI显示接口标准的串行位流替代品。DSI减少了管脚数目和I/O电源功耗,DSI支持使能两个显示控制器连接到有MIPI DSI接收器的外部显示。DSI传输像素数据从内部显示控制器到外部第三方LCD模块。

特点:

l PHY层

n 传输的开始/结束。其它带宽外信号

n 每个DSI接口:1个时钟LANE;多达4个数据Lanes

n 支持连接配置:1x4,2x4

n 2x4配置时支持双链路操作。对称/非对称分离,两个左右边或奇偶组分离方案

n DSC连接压缩

n 最大连接速度1.5Gbps,每个MIPI D-PHY1.1v版本

n 最大10MHz LP接收速率

l 带有分发器的Lane管理层

l 带包构造器的协议层

l 支持MIPI DSI1.0.1v版本强制特征

l 命令模式(One-shot),带Host和/或作为master显示控制器

l 时钟

n 位时钟:串行数据流位速率时钟

n 字节时钟:Lane管理层字节速率时钟

n 应用时钟:协议层字节速率时钟

l 错误检测/校正

n ECC产生,用于包头

n 检查和产生,用于长包

l 错误恢复

l 高速传输定时

l 低电源接收定时器

l 轮回响应超时

表10 DSI信号描述

| 名称 | 类型 | 描述 |

| DSI_0_CLK_N/P DSI_2_CLK_N/P | 输出 | 差分输出时钟,为2个1x4 DSI接口 |

| DSI_0_D[1:0]_N/P DSI_1_D[1:0]_N/P DSI_2_D[1:0]_N/P DSI_3_D[1:0]_N/P | 双向 | DSI接口的差分数据Lane DSI_0_D[1:0]和DSI_1_D[1:0]与DSI_0_CLK相关 DSI_2_D[1:0]和DSI_3_D[1:0]与DSI_2_CLK相关 |

3.3.2 HDMI和DP(DisplayPort)接口

| 标准 | 注释 |

| HDMI规范v2.0 | >340MHz像素时钟 支持水印 支持Clock/4(1/40位率时钟) |

| HDCP系统规范 v2.2 | |

| HDCO系统规范 v1.3 | |

HDMI和DP接口共享同一个连接器上的管脚,HDMI2.0增加了新的传输模式,使得链路时钟频率大于340MHz高达600MHz。

特点:

l 片上HDCP存储,不需要外部加密ROM

l 支持HDCP1.3和HDCP2.2

l HDMI

n HDMI2.0模式(3.4Gbps < 数据速率 <=6Gbps)

n HDMI1.4模式(数据速率 <= 3.4Gbps)

n 来自HAD控制器的多通道音频,多达8个通道,192kHz24-bit

n 厂家专有的帧内(VSI)包传输

n 24-bit RGB和24-bit YUV444(HDMI)像素格式

n 变化最小化差分信号(TDMS)功能上达340MHz像素时钟速率

表11 HDMI信号描述

| 信号 | 类型 | 描述 |

| DP1_TX3+ DP1_TX3- | Output | HDMI差分时钟,载板上要求是AC耦合且下拉(带禁止) |

| DP1_TX[2:0]+ DP1_TX[2:0]- | Output | HDMI/DP差分数据,载板上要求是AC耦合且下拉(带禁止) DP1_TX0 = HDMI_TXD2 DP1_TX1 = HDMI_TXD1 DP1_TX2 = HDMI_TXD0 |

| DP1_HPD | Input | 中断,用于热插拔检测,要求有电平转换电路,因为这个叫不兼容5V |

| HDMI_CEC | 双向 | CEC 单线串行总线 NVIDIA提供低级CEC API(读/写),这些在早期Android版本里是不支持的。为了增加CEC支持,需要第3方库生效。 |

| DP1_AUX_CH+(DDC_SCL) | Output | DDC串行时钟,要求电平偏移,因为这个脚不支持5V |

| DP1_AUX_CH-(DDC_SDA) | 双向 | DDC串行数据,要求电平偏移,因为这个脚不支持5V |

表12 DP信号描述

| 信号 | 类型 | 描述 |

| DP1_TX[3:0]+ DP1_TX[3:0]- | 输出 | DP差分线,载板上要求AC耦合 |

| DP1_HPD | 输入 | 中断,用于热插拔检测 |

| DP1_AUX_CH+ DP1_AUX_CH- | 双向 | DP辅助通道,载板上要求AC耦合 |

3.3.3 嵌入式显示端口接口(eDP:Embedded DisplayPort)

| 标准 | 注释 |

| eDP1.4 | 支持eDP1.4特征: l 附加的连接速率 l 扩展的帧 l 电源序列 l 减少辅助定时 l 减少主电压摆幅 |

eDP是一个混合信号接口,由4对差分输出lane和1个PLL组成,这个PLL用来根据输入的像素时钟来锁相产生一个高频位时钟,以便能够按期望的模式以像素速率使每个lane处理10bit的并行数据,嵌入式显示端口(eDP)模式(RBR 1.6GHz、2.16GHz、2.43GHz、HBR 2.7GHz、3.42GHz、4.32GHz、HBR2 5.4GHz)。

注意:eDP已经通过DP1.2b PHYCTS测试,即使eDPv1.4支持低摆幅电压和其它中间的位率。这意味着下面的标称电压级别(400mV、600mV、800mV、1200mV)和数据速率(RBR、HBR、HBR2)被测试过。这个接口来重新调节电路参数,以驱动更低电压摆幅(400mV以下),能被编程到其它中间位率,以满足具体的平板显示屏和系统设计者的要求,

eDP模块收集(collect)来自显示管线输出的像素、将它们格式化/编码成期望的格式,然后以流的形式发布到不同的输出设备,它仅驱动本地平板显示器(不支持外部DP端口),包括一个小的测试模式发生器和CRC发生器。

表13 eDP信号

| 信号 | 类型 | 描述 |

| DP0_TX[3:0]+ DP0_TX[3:0]- | 输出 | eDP差分Lanes |

| DP0_HPD | 输入 | eDP热插拔检测 |

| DP0_AUX_CH+ CP0_AUX_CH- | 双向 | eDP辅助通道 |

3.4 音频接口

通过I2S控制器在系统内存和音频codec之间传输音频数据流。I2S控制器支持I2S格式、左调整格式、右调整格式、DSP格式、以及I2S规范定义的格式。

I2S和PCM(主和从模式)支持的时钟速率达24.5760MHz。

I2S控制器支持点到点串行接口的I2S数字音频流。I2S兼容产品,比如袖珍播放器、磁带设备、数字音频处理器等等可以直接连接到I2S控制器。控制器还支持PCM和电话模式的数据传输。PCM是数字化音频的标准方法尤其是对语音。I2S控制器支持双向音频流且支持半双工和全双工模式。

特点:

l 基本的I2S模式,支持(I2S、RJM、LJM和DSP),Master和Slave模式

l PCM模式:短(1bit时钟宽)和长帧(2bit时钟宽)同步,无论是主还是从模式

l NW模式:独立的slot选择,无论是Tx还是Rx

l TDM模式灵活的多slot和slot选择

l Capability to drive-out a High-z outside the prescribed slot fortransmission

l 流控制:外部输入/输出流

表14 I2S信号描述

| 信号 | 类型 | 描述 |

| I2S[3:0]_LRCK | 双向 | 帧同步/字选择,支持I2S/PCM音频,接口可能是主或从 |

| I2S[3:0]_CLK | 双向 | 串行时钟/位时钟。支持I2S/PCM音频。接口可能是主或从 |

| I2S[3:0]_SDIN | Input | 数据输入,支持I2S/PCM音频,接口可能是主或从 |

| I2S[3:0]_SDOUT | 双向 | 数据输出,支持I2S/PCM音频,接口可能是主或从 |

3.5 USB接口

| 标准 | 注释 |

| USB规范3.0 | 参考规范中有关接口时序细节 |

| USB规范2.0 | USB电池充电规范V1.0;包括数据连接检测协议。 模式:Host和Device。 速度:Low、Full、High。 参考规范中相关接口时序细节。 |

| USB增强Host控制器接口规范1.0 | 参考规范中相关接口时序细节。 |

参见Jetson TX1 OEM ProductDesign Guide所描述的被支持的USB3.0/PCIe/SATA配置和连接例子。

表15 USB信号

| 信号 | 类型 | 描述 |

| USB[2:0]_D- | 模拟 | USB数据负(USB2.0接口) |

| USB[2:0]_D+ | 模拟 | USB数据正(USB2.0接口) |

| USB_SS1_RX- | 输入 | USB3.0#1:接收数据负输入 |

| USB_SS1_RX+ | 输入 | USB3.0#1:接收数据正输入 |

| USB_SS1_TX- | 输出 | USB3.0#1:发送数据负输出 |

| USB_SS1_TX+ | 输出 | USB3.0#1:发送数据正输出 |

| USB_SS2_RX-(PEX1_RX-或PEX3_RX-) | 输入 | USB3.0#2可选:接收数据负输入 |

| USB_SS2_RX+(PEX1_RX+或PEX3_RX+) | 输入 | USB3.0#2可选:接收数据正输入 |

| USB_SS2_TX-(PEX1_TX-或PEX3_TX-) | 输出 | USB3.0#2可选:发送数据负输出 |

| USB_SS2_TX+(PEX1_TX+或PEX3_TX+) | 输出 | USB3.0#2可选:发送数据正输出 |

| USB_SS3_RX-(SATA_RX-) | 输入 | USB3.0#3可选:接收数据负输入 |

| USB_SS3_R+(SATA_RX+) | 输入 | USB3.0#3可选:接收数据正输入 |

| USB_SS3_TX-(SATA_TX-) | 输出 | USB3.0#3可选:发送数据负输出 |

| USB_SS3_t+(SATA_TX+) | 输出 | USB3.0#3可选:发送数据正输出 |

注释:USB_SS0接口在连接器上不可用,因为它用于千兆以太网。

3.6 PCIe接口

| 标准 | 注释 |

| PCIe基本规范2.0 | TX1满足Gen2(5.0GT/S)数据速率的时序要求,参看标准中的完整接口定时细节 虽然NVIDIA验证了TX1设计满足PCIe规范,但是PCIe软件支持可能是有限的 |

TX1集成了x5 Lane PCIe桥,使能控制路径从TX1到外部PCIe设备,2个PCIe Gen2控制器(一个x4,一个x1)支持连接到1个或2个EP上。

参见Jetson TX1 OEM ProductDesign Guide所描述的被支持的USB3.0/PCIe/SATA配置和连接例子。

| 信号功能 | 类型 | 描述 |

| PEX_WAKE# | Input | PCIe唤醒 这个信号用作PCIe规范定义的WAKE#信号,当这个信号被PCIe设备断言的时候,它请求恢复系统电源,这个信号的断言不导致中断或其它结果 |

| PCIe控制器0 |

| PEX0_REFCLK+/- | Output | 差分参考时钟,PEX0_REFCLK与PCIe控制器0相关 |

| PEX2_RX+/-(Lane3) PEX_RFU_RX+/-(Lane2) USB_SS1_RX+/-(Lane1) PEX0_RX+/-(Lane0) | Input | 差分接收数据Lanes,与PCIe控制器0相关 |

| PEX2_TX+/-(Lane3) PEX_RFU_TX+/-(Lane2) USB_SS1_TX+/-(Lane1) PEX0_TX+/-(Lane0) | Output | 差分发送数据Lanes,与PCIe控制器0相关 |

| PEX0_CLKREQ# | 双向 | PCIe参考时钟请求 这个信号是PCIe设备用来指示它需要PEX_REFCLKP和PEX_REFCLKN上有有效的的参考时钟,PEX0_CLKREQ#与PCIe控制器0相关 |

| PEX0_RST# | Output | PCIe复位 这个信号用来复位所有的PCIe连接,在PCIe插座上的电源稳定之后,这个信号必须断言100ms,PEX0_RST#与PCIe控制器0相关。 |

| PCIe控制器1 |

| PEX1_REFCLK+/- | Output | 差分参考时钟,PEX1_REFCLK与PCIe控制器1相关 |

| PEX1_RX+/- | Input | 差分接收数据Lane,与PCIe控制器1相关 |

| PEX1_TX+/- | Output | 差分发送数据Lane,与PCIe控制器1相关 |

| PEX1_CLKREQ# | 双向 | PCIe参考时钟请求 这个信号是PCIe设备用来指示它需要PEX_REFCLKP和PEX_REFCLKN上有有效的的参考时钟,PEX1_CLKREQ#与PCIe控制器1相关 |

| PEX1_RST# | Output | PCIe复位 这个信号用来复位所有的PCIe连接,在PCIe插座上的电源稳定之后,这个信号必须断言100ms,PEX0_RST#与PCIe控制器1相关。 |

3.7 SPI接口

SPI控制器运行速度在Master模式可达65Mbps,在从模式可达45Mbps,它可以在控制器和外部设备之间进行双工、同步、串行通讯,SPI有4个信号:SS_N(片选)、SCSK(时钟)、MOSI(Master数据输出和从数据输入)和MISO(从数据输出和主数据输入)。数据按照数据传输方向在每个SCK边沿在MOSI或MISO上传输,而接收器总是在另一个SCK边沿时刻接收数据。

特点:

l 独立的RX FIFO和TX FIFO

l 软件控制的位长,支持包尺寸1到32位。

l 打包模式支持位长7bit(8bit包长)和15bit(16bit包长)

l SS_N能由软件控制来选择,或者它能自动由硬件在包边界产生。

l 接收比较模式(控制器在接受数据进入FIFO之前在输入数据上监听特定的模式)

l 同时接收和发送支持

l 支持master模式。从模式无效

表17 SPI信号描述

| 信号 | 类型 | 描述 |

| SPI[2:1]_CS[1:0]# SPI0_CS0_N | 双向 | 片选SPI[2:1]:取决于管脚复用。每个SPI接口可能有一个或多个片选选择。 |

| SPI[2:0]_MISO | 双向 | Master In / Slave Out |

| SPI[2:0]_MOSI | 双向 | Master Out / Slave In |

| SPI[2:0]_CLK | 双向 | 串行时钟:时钟相位和极性可编程 |

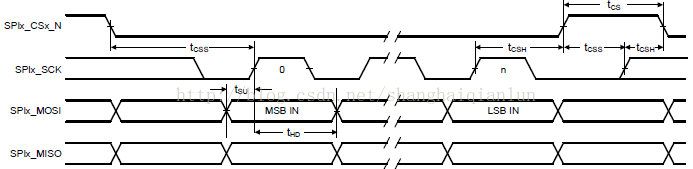

图6 SPI Master定时

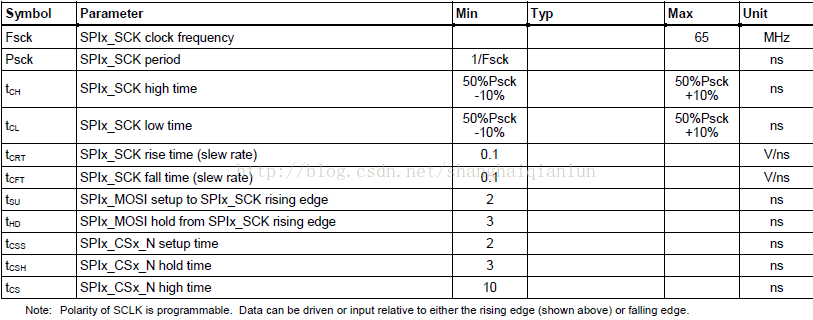

表18 SPI主模式定时参数

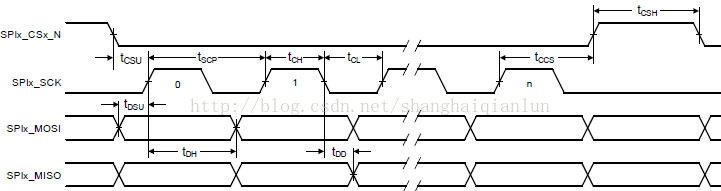

图7 SPI从模式时序图

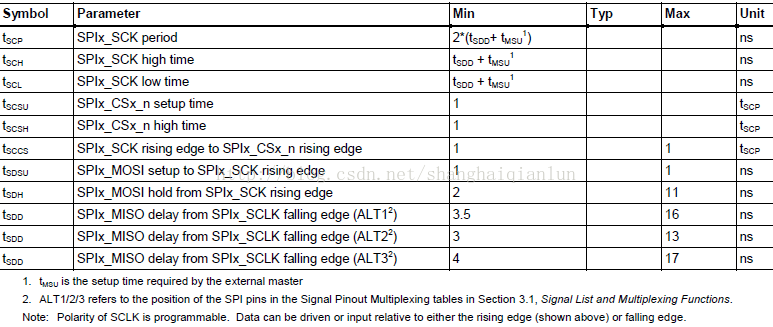

表19 SPI从模式shixu1参数

3.8 芯片之间通讯(I2C)控制器

I2C控制器支持多主或多从,标准速度100kbit/s,快速400kbit/s,以及快速+1Mbit/s,高速3.4Mbit/s。支持7bit和10bit从地址模式

表20 I2C使用

| 接口名 | 目标应用 | TX1上的终端 |

| I2C_GP0_CLK/DAT | 多用途 | 1K欧连接到1.8V |

| I2C_GP1_CLK/DAT | 电源监视 | 1K欧连接到3.3V |

| I2C_PM_CLK/DAT | 相机 | 1K欧连接到1.8V |

| I2C_CAM_CLK/DAT | 相机和相机相关的功能 | 1K欧连接到1.8V |

| DP1_AUX_CJ+/- | 显示:HDMI/DP(DDC) | 没有 |

| DP0_AUX_CJ+/- | 显示:eDP | 没有 |

表21 I2C信号描述

| 信号 | 类型 | 描述 |

| I2C_GP[1:0]_CLK I2C_PM_CLK I2C_CAM_CLK | 双向 | 时钟 |

| I2C_GP[1:0]_DAT I2C_PM_DAT I2C_CAM_DAT | 双向 | 数据 |

3.9 UART控制器

特点:

l 同步串行数据流:起始位和停止位添加到发送数据形成一个数据字符。

l 支持16450-和16550-兼容模式,缺省模式是16450

l 设备时钟高达200MHz,波特率12.5Mbit/秒

l 数据完整性可通过添加奇偶校验位非数据字符。

l 支持字长5到8bit及可选的奇偶校验位、1或2个停止位

l 支持调制解调器的控制输入。

l DMA伺服于TX和RX

l 8bit x 36深的TX FIFO

l 11bit x 36深的RX FIFO。在FIFO模式每个条目11bit的3bit或注册RX错误(break、帧、奇偶校验错误作为FIFO条目的10、9、8bit)

l 自动敏感比特率检测

l 超时中断,指示是否输入流停止

l 优先级中断机制

l 流控制:RTS和CTS

l 内部环路

l SIR编码/解码(3/16或4/16波特率脉冲宽度到发送位0)

表22 UART信号描述

| 功能 | 类型 | 描述 |

| UART[2:0]_TX | Output | 发送数据 |

| UART[2:0]_RX | Input | 接收数据 |

| UART[2:0]_CTS# | Input | 清除发送 |

| UART[2:0]_RTS# | output | 请求发送 |

3.10 视频输入接口

MIPI相机串口(CSI)

| 标准 | 注释 |

| MIPI CSI2.0接收规范 | |

| MIPI D-PHY v1.2物理层规范 | |

Jetson TX1模块具有3个MIPI CSI x4模块,支持多种设备类型和摄像机配置。摄像机串行接口(CSI)是基于MIPI CSI2.0标准的规范,CSI接收器,接收来自外部相机模块使用CSI发送器发送的数据。

特点:

l 支持摄像机配置:

n 1 x4:单相机,具有4个lane传感器,使用3个MIPI x4块的任意一个。

n 2 x4:立体对,每个相机有4个lane,使用三个MIPI x4块的任一对。

n 2 x2:双相机模式,将任何MIPI x4块拆分成两个x2的子块,能同时支持到6个摄像机流

l 支持输入数据格式:

n RGB:RGB888, RGB666, RGB565, RGB555,RGB444

n YUV: YUV4522-8b, YUV420-8b(传统的), YUV420-8b,YUV444-8b

n RAW: RAW6, RAW7, RAW8, RAW10, RAW12, RAW14

n DPCM: 用户定义

n 用户定义:JPEG8

n 内嵌:内嵌控制信息

l 支持单shot模式。

l 物理层接口(MIPI D-PHY)操作模式

n 高速模式:高速差分信号,达1.5Gbps,低功耗突发传输

n 低电压控制:单端1.2VCMOS级,低速信号,用于握手

n 低电压Escape:low speedsignaling for data, used for escape command entry only. 20ms

如果2个流来自单个源,那么这个流可以使用一个滤波器进行分离,这个滤波器按不同的虚拟通道号或数据类型进行检索。如果使用数据类型分离,正常数据类型从嵌入的数据类型分离出来,因为仅2个像素解析器(parsers),虚拟通道和内嵌数据能力不可能同时使用。

表23 CSI信号描述

| 信号名称 | 类型 | 描述 |

| CSI_[5:0]_CLK_N CSI_[5:0]_CLK_P | 输入 | 差分CSI时钟 |

| CSI_[5:0]_D[1:0]_N CSI_[5:0]_D[1:0]_P | 输入 | 差分CSI数据Lanes,每个数据对可能会与不同的相机关联,或CSI_[1:0]_D[1:0], CSI_[3:2]_D[1:0], CSI_[5:4]_D[1:0]可以用来与4Lanes相机接口 |

摄像机/VI(video input视频输入)

视频输入(VI)模块从CSI接收器中接收数据,将其送到系统内存或专用的图像信号处理器(ISP)执行资源,VI提供的格式RGB、YCbCr、和原始的Bayer数据,以支持多种相机用户模块,这些模块包括单个和多个相机系统,可能有多达6个有效的流,这些输入流从MIPI兼容的CMOS传感器相机模块获得。

表24 相机时钟和控制信号描述

| 信号 | 类型 | 描述 |

| I2C_CAM_CLK | 双向 | 见I2C一节 |

| I2C_CAM_DAT | 双向 | 见I2C一节 |

| CAM[1:0]_MCLK | 输出 | 视频输入Master时钟,用于主、次相机 |

| GPIO1_CAM1_PWR# GPIO0_CAM0_PWR# | 双向 | 相机电源控制信号:连接到相机的掉电脚,可用作通用目的IOs |

| GPIO5_CAM_FLASH_EN | 输出 | 相机闪光灯使能:连接使能闪光灯电路,可用作通用目的IO |

| GPIO3_CAM1_RST# GPIO2_CAM-_RST# | 输出 | 相机复位,用于相机模块复位,如果自动聚焦使能被要求,GPIO3_CAM1_RST#到相机模块的AF_EN脚,使用GPIO2_CAM0_RST#作为公共的复位线,可用作通用目的IOs。 |

3.11 其它接口

调试接口

TX1有一个可选的JTAG接口

表25 调试信号描述

| 信号 | 类型 | 描述 |

| JTAG_RTCK | Output | 返回的测试时钟 |

| JTAG_TCK | Input | 测试时钟 |

| JTAG_TDI | Input | 测试数据入 |

| JTAG_TDO | Output | 测试数据出 |

| JTAG_TMS | Input | 测试模式选择 |

| JTAG_TRST# | Input | 测试复位 |

PWFM(脉冲宽度/频率调制器)

PWFM是一个频率除法器,具有可变脉冲宽度,PWFM运行时钟是在时钟和复位控制器里的设备时钟,最大频率48MHz,PWFM先预分频(除256),这个信号可在TX1脚上得到,主要用于LCD对比度和亮度调整,另一个用于风扇速度控制。

表26 PWFM信号

| 信号 | 类型 | 描述 |

| LCD0_BKLT_PWM FAN_PWM | output | LCD背光(PM3_PWM0)和FAN(PM3_PWM3)脉冲频率调整信号,这些输出一个频率信号,是设备时钟源的分频,及输出一个可编程的脉冲宽度 |

本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有涉嫌抄袭侵权的内容,请联系:hwhale#tublm.com(使用前将#替换为@)