基于NIOS-II软核与verilog语言的流水灯实现

文章目录

- 基于NIOS-II软核与verilog语言的流水灯实现

- 1.实验目的

- 2.实验设备

- 3.实验内容

- 4.软核设计

- 4.1 新建一个工程

- 4.2 Qsys 系统设计

- 4.3 进行逻辑连接

- 4.3.1 在 Quartus-II 中新建一个原理图

- 4.3.2 进行逻辑连接和生成管脚

- 4.3.3 编译

- 4.3.4 绑定引脚

- 5. 软件设计

-

- 6. 烧录

- 7. verilog语言实现流水灯

- 8.总结

- 9.参考文章

1.实验目的

(1)学习 Quartus Prime 、Platform Designer、Nios II SBT 的基本操作;

(2)初步了解 SOPC 的开发流程,基本掌握 Nios II 软核的定制方法;

(3)掌握 Nios II 软件的开发流程,软件的基本调式方法。

2.实验设备

硬件:PC 机、DE2-115 FPGA 实验开发平台;

软件:Quartus Prime 18.1、Platform Designer、Nios II SBT

3.实验内容

使用 FPGA 资源搭建一个简单 Nios II 处理器系统,具体包括:

(1) 在 Quartus Prime 中建立一个工程;

(2) 使用 PD 建立并生成一个简单的基于 Nios II 的硬件系统;

(3) 在 Quartus Prime 工程中编译基于 Nios II 的硬件系统并生成配置文件.sof;

(4) 在 Nios II SBT 中建立对应硬件系统的用户 C/C++工程,编写一简单用户程序,在

Nios II SBT 中编译程序生成可执行文件.elf;

(5) 将配置文件.sof 和可执行文件.elf 都下载到 FPGA 进行调试运行。

4.软核设计

4.1 新建一个工程

选择目标芯片:cycloneIVE系列的EP4CE11529C7,这里根据自己板子的芯片型号选择即可

4.2 Qsys 系统设计

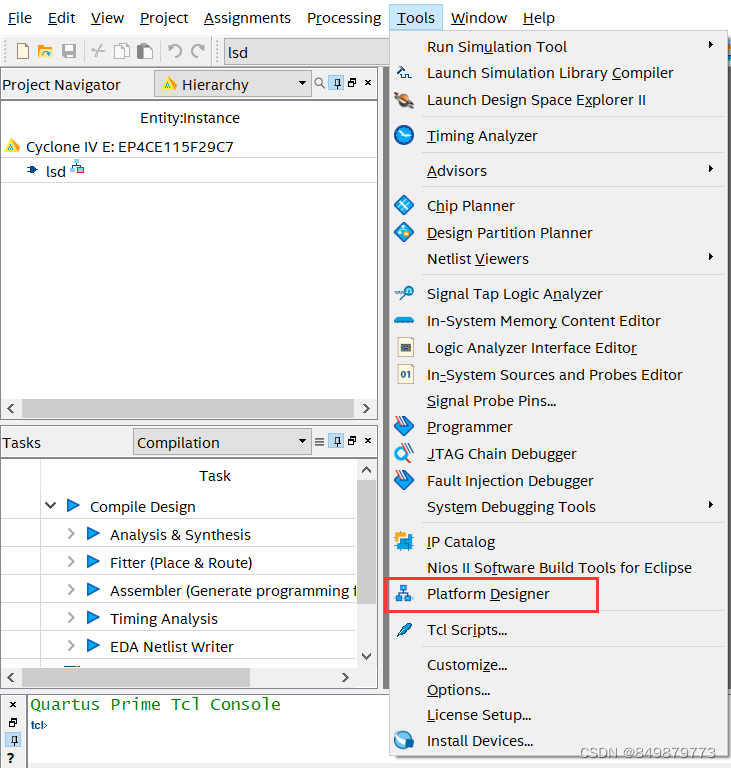

1.点击 Tools 下拉菜单下的 platform designer

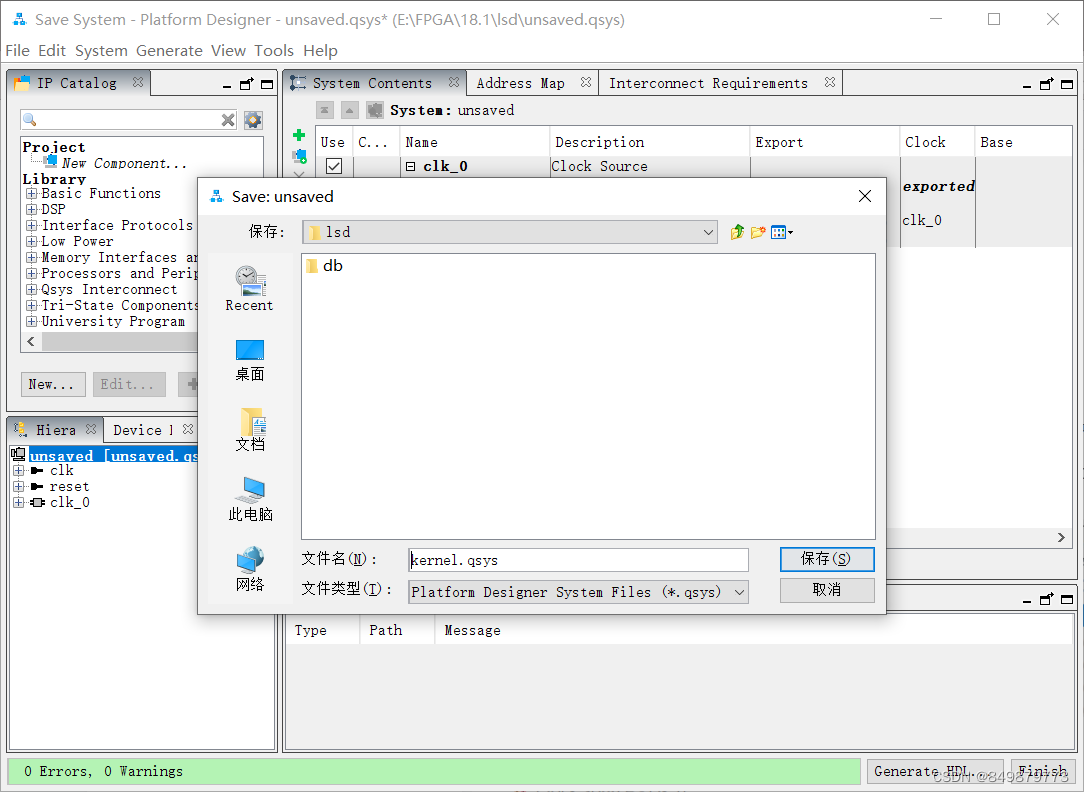

2. 启动 Qsys 后,点击 File —> save,如图 1.7 所示,在文件名中填写为 kernel,后点击 OK

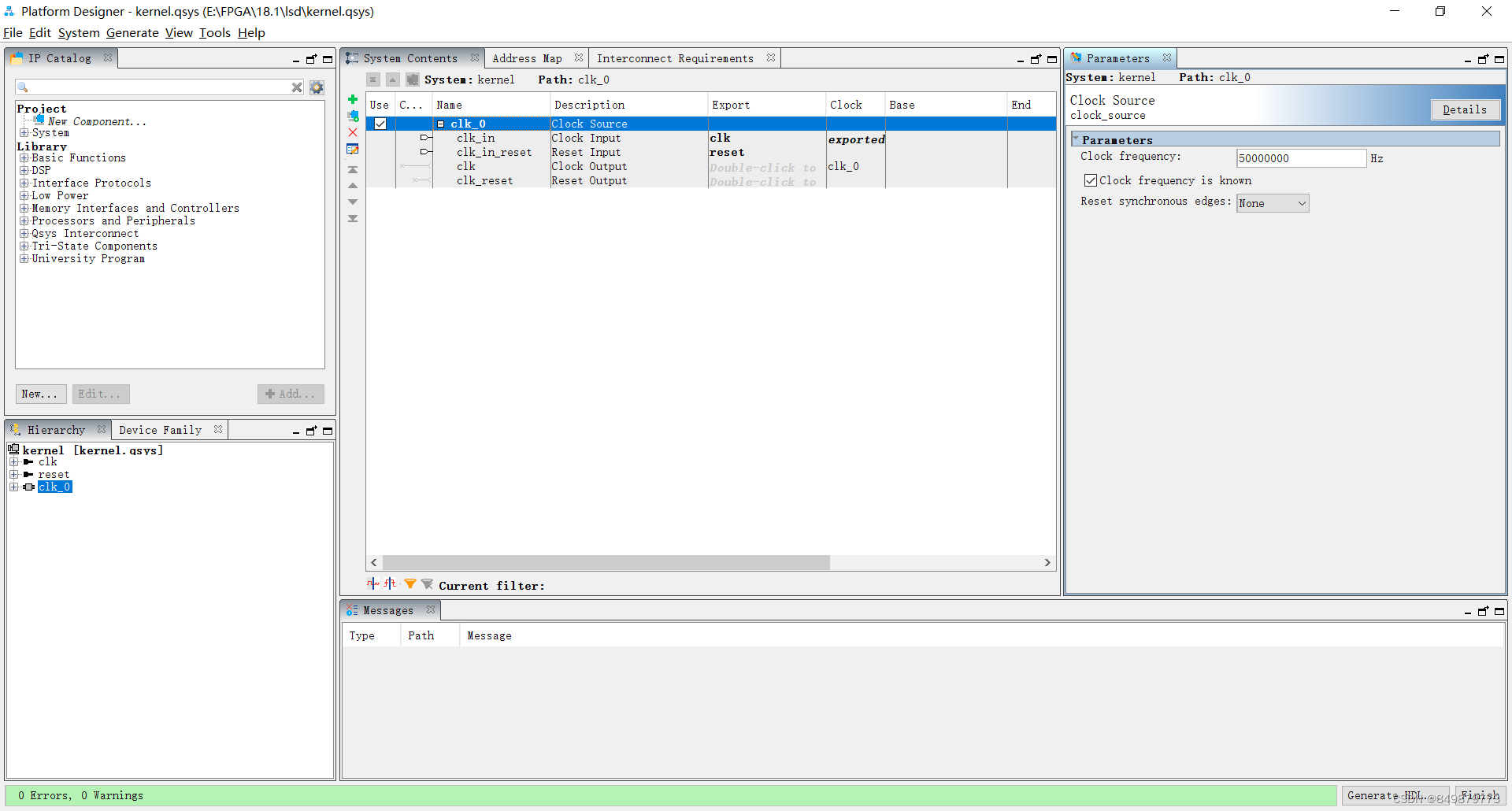

3.鼠标放在 clk_0 处点击右键 Edit 或是双击 clk_0 元件,对 Clock 进行时钟设置,设为为 50M

4.添加 CPU 和外围器件

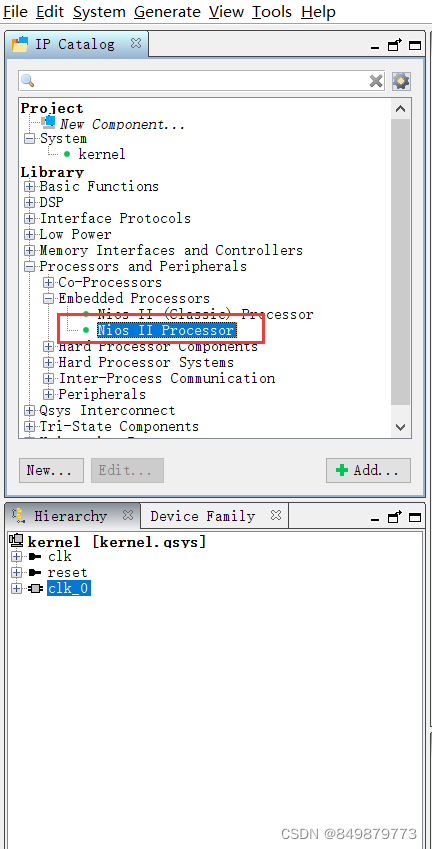

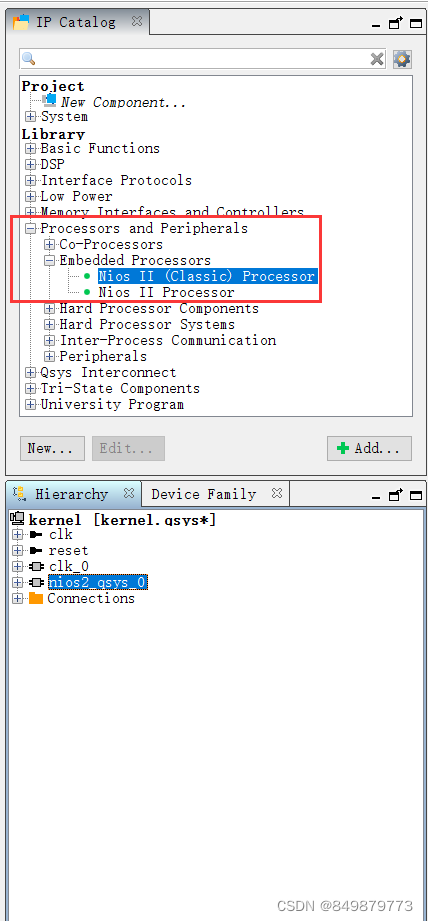

添加 Nios II 32-bit CPU

-

在 “component library” 标签栏中找到 “Nios II Processor” 后点击 Add

-

-

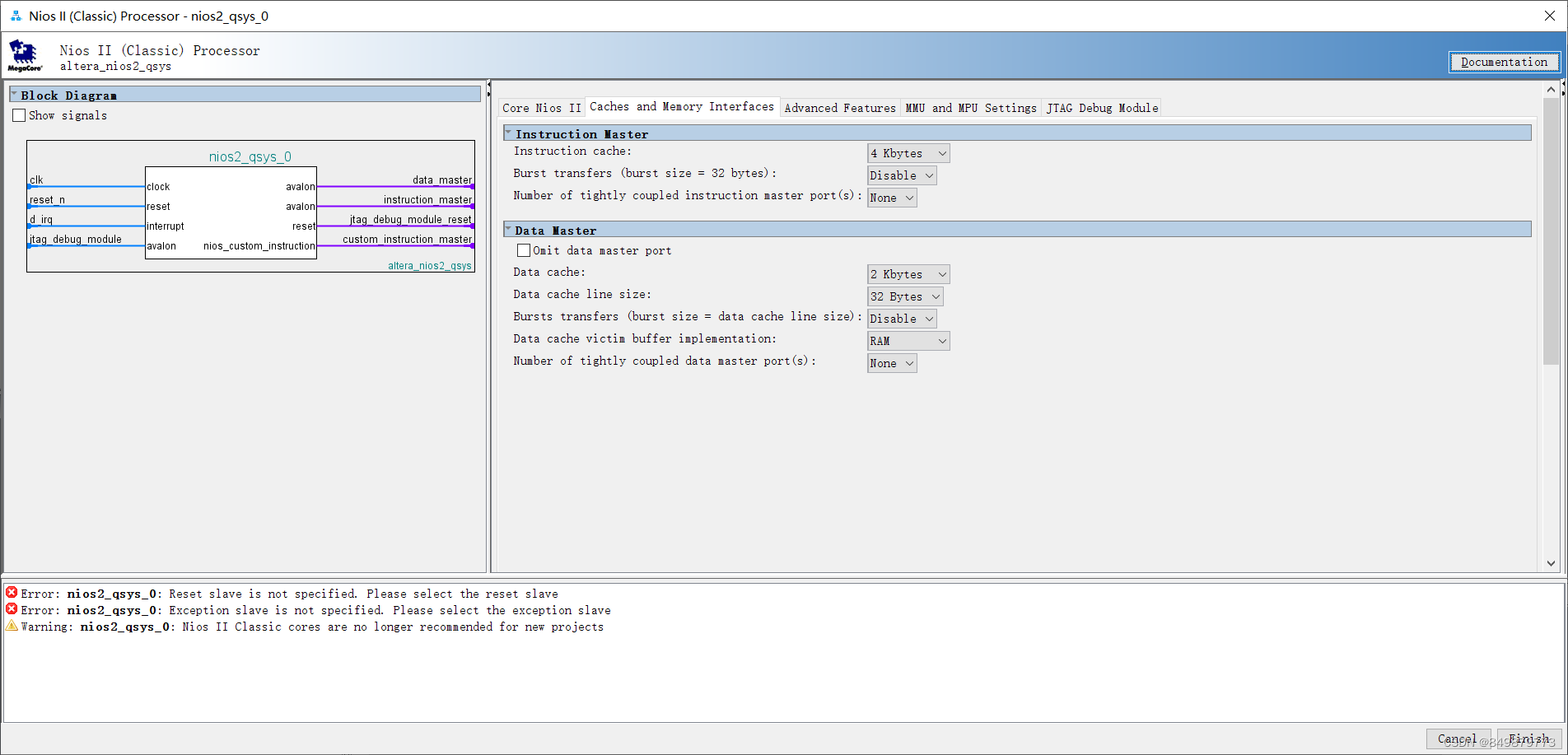

在 Nios Core 栏中选择 Nios II/f 选项,其他保持默认选项

-

-

在 ”Caches and Memory Interfaces” 标签栏中保持默认设置 (Instruction Cache 选择

4Kbytes)

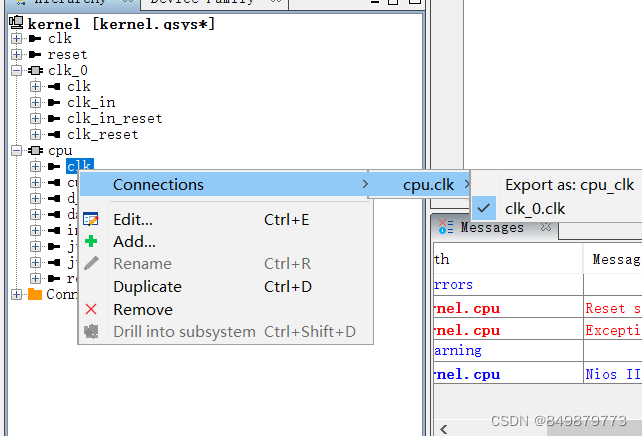

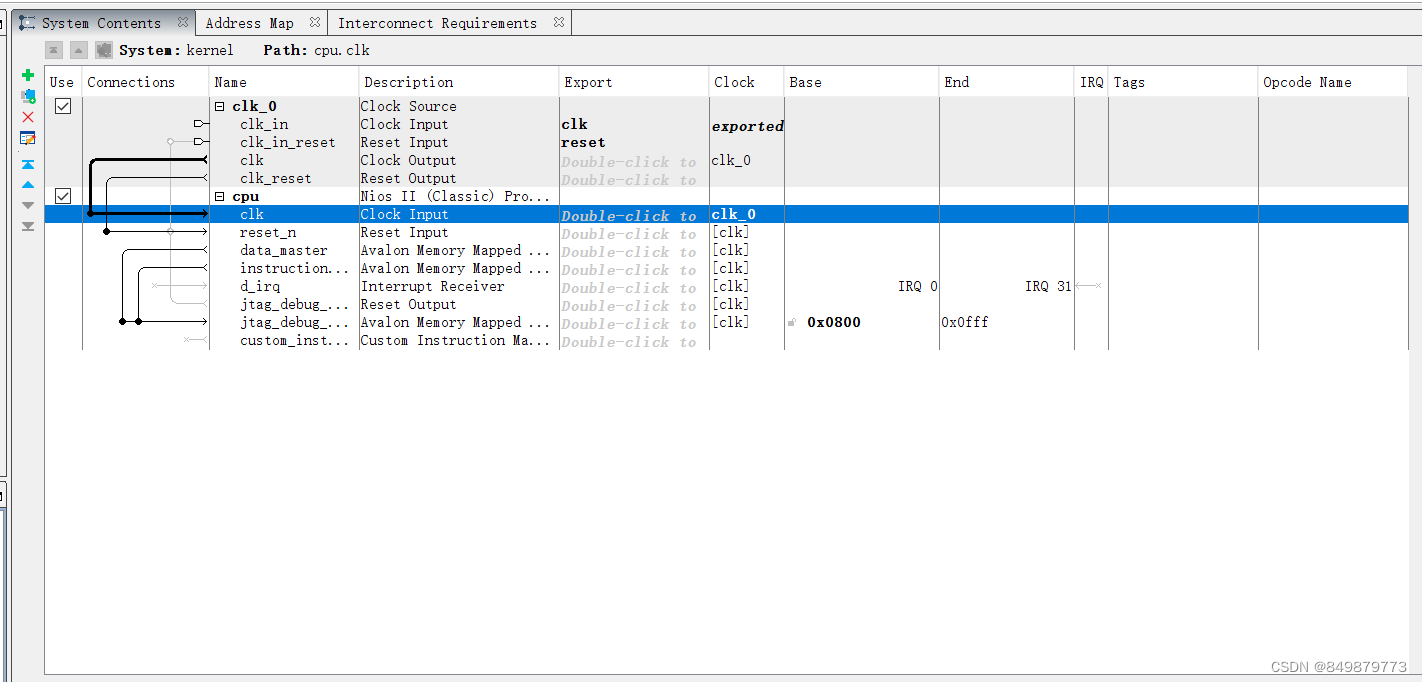

- 点击 Finish 回到 Qsys 界面 将 nios2_qsys_0 重命名为 cpu,点击 ”Rename” 即可重新命名

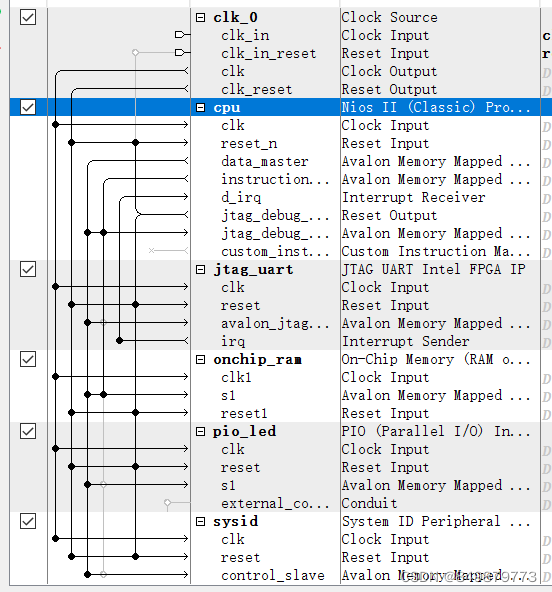

- 将 cpu 的 clk 和 reste_n 分别与系统时钟 clk_0 的 clk 和 clk_reset 相连

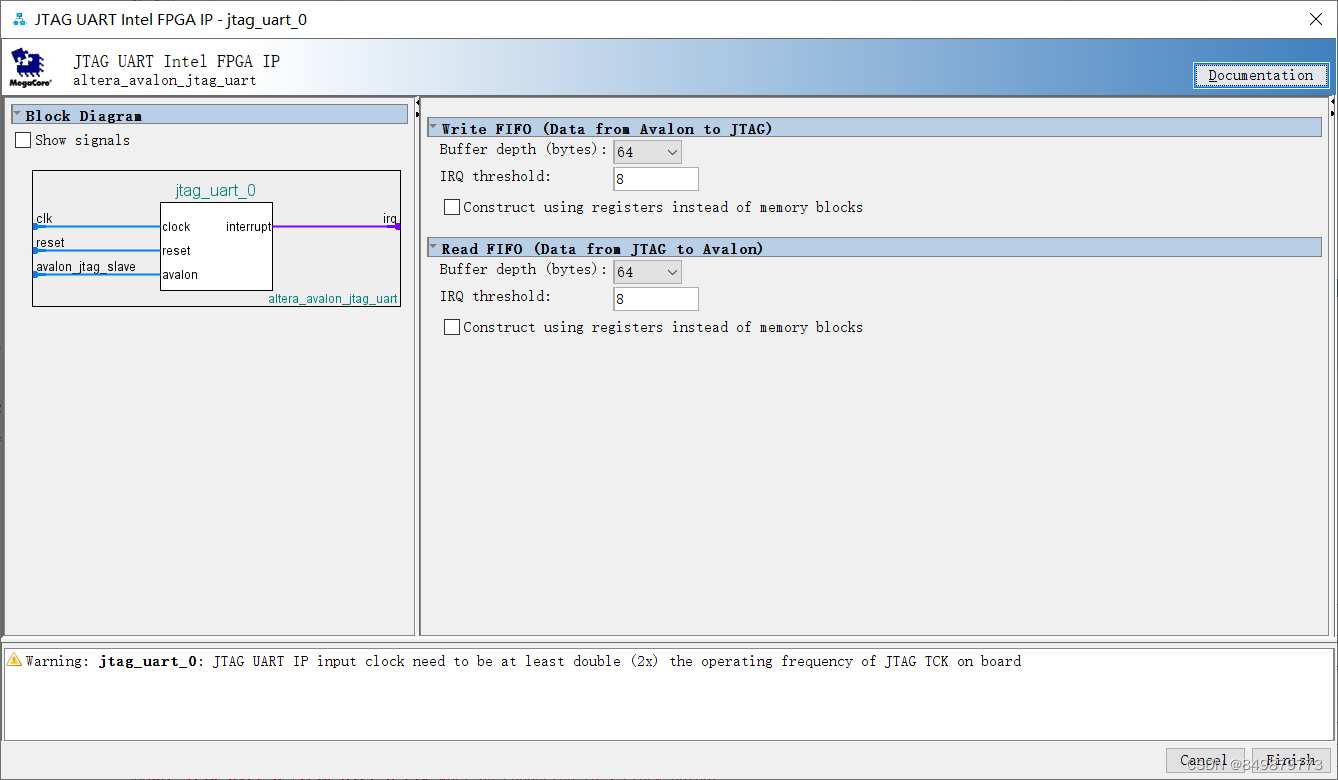

添加 jtag uart 接口

jtag uart 接口是 Nios II 嵌入式处理器新添加的接口元件,通过内嵌在 Intel FPGA 内部的 JTAG 电路,可以实现在 PC 主机与 Qsys 系统之间进行串行字符流通信。

-

在 ”Component Library” 标签栏中的查找窗口输入 jtag 找到 ”JTAG UART ”,然后点击 Add

-

在 JTAG UART-jtag-uart_0 的设置向导中保持默认选项,点击 Finish

-

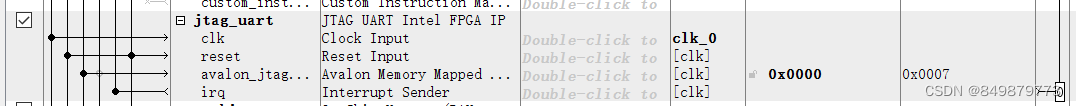

返回 ”System Contents” 标签栏可以看到新加入的 ”JTAG UART” 核。在 ”Name” 列中将

jtag-uart_0 重命名为 jtag-uart。

-

返回 ”System Contents” 标签栏可以看到新加入的 ”JTAG UART” 核。在 ”Name” 列中将

jtag-uart_0 重命名为 jtag-uart。

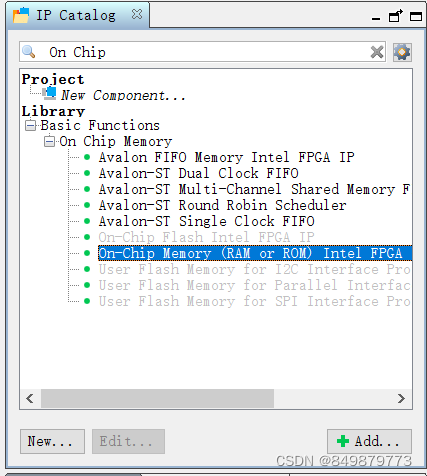

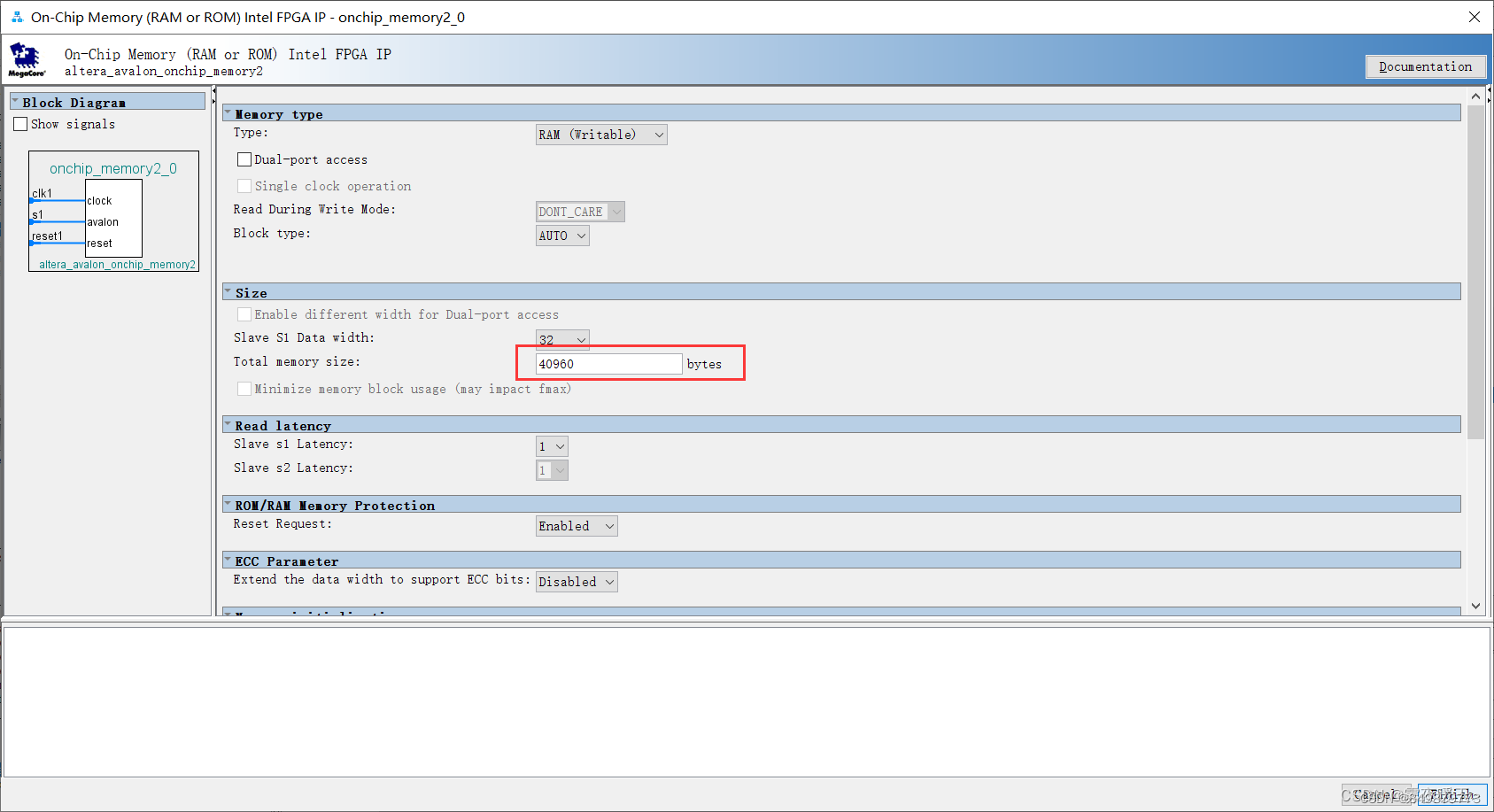

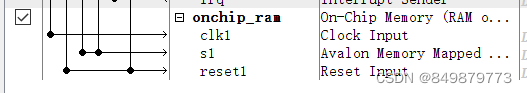

添加片上存储器 On-Chip Memory(RAM)核

- 在左侧 ”Component Library” 标签栏中的查找窗口输入 On Chip 找到 ”On-Chip

Memory(RAM or ROM)” 后点击 Add

- 在 ”Size” 栏中的 ”Total memory size” 窗口中输入 40960(即片上内存的大小为 40KB),其余选项保持默认,点击 Finish。

-

返回 ”System Contents” 标签栏可以看到新加入的 ”On-Chip Memory” 核。在 ”Name”

列中将 onchip_memory2_0 改名为 onchip_ram

-

进行时钟、数据端口、指令端口的连接

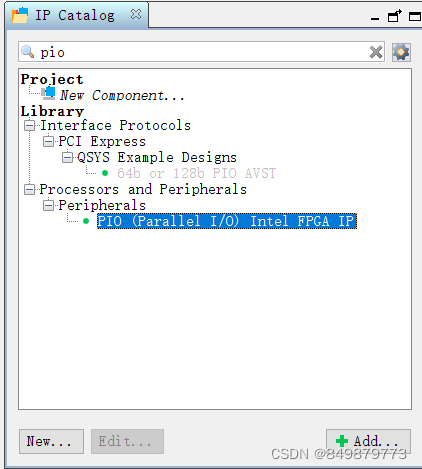

添加 PIO 接口

-

在左侧 ”Component Library” 标签栏中的查找窗口输入 pio 找到 ”PIO” 后点击Add

-

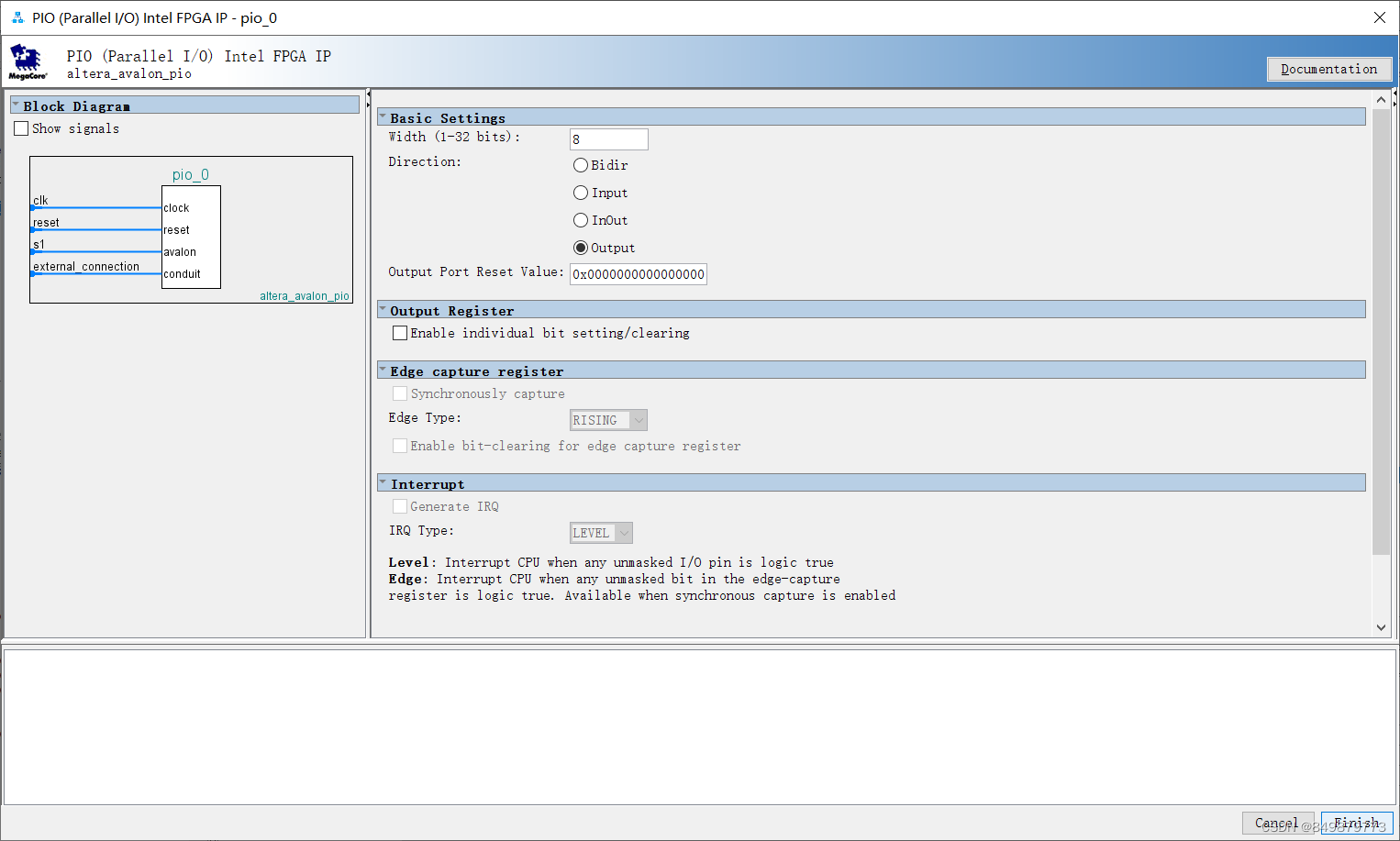

确定以下选项:Width 为 8bits,Direction 选择 output,其余选项保持默认,点击

Finish。

-

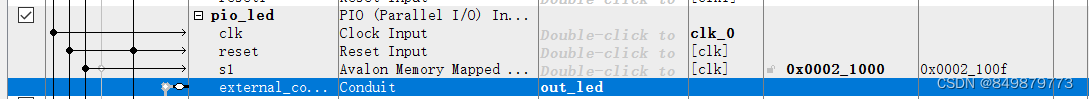

返回 ”System Contents” 标签栏可以看到新加入的 ”PIO” 核。在 ”Name” 列中将

pio_0 改名为 pio_led。并在在 Export 栏处双击,把输出口引出来,并命名为 out_led。

-

进行时钟、数据端口、指令端口的连接

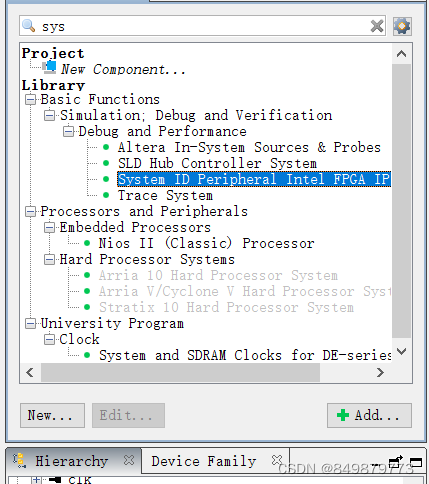

添加片 System ID Peripheral 核

-

在左侧 ”Component Library” 标签栏中的查找窗口输入 sys 找到 ” System ID

Peripheral” 后点击 Add

-

保持默认选项,单击 Finish。

-

返回 ”System Contents” 标签栏可以看到新加入的 ” System ID Peripheral” 核。在 ”Name” 列中将 sysid_qsys_0 改名为 sysid

-

进行时钟、数据端口的连接

- 完成 Qsys 设计的后续工作

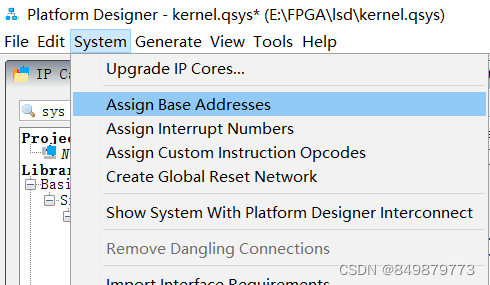

- **基地址分配:**点击 Qsys 主界面菜单栏中的 ”System” 下的 ”Assign Base Addresses”。

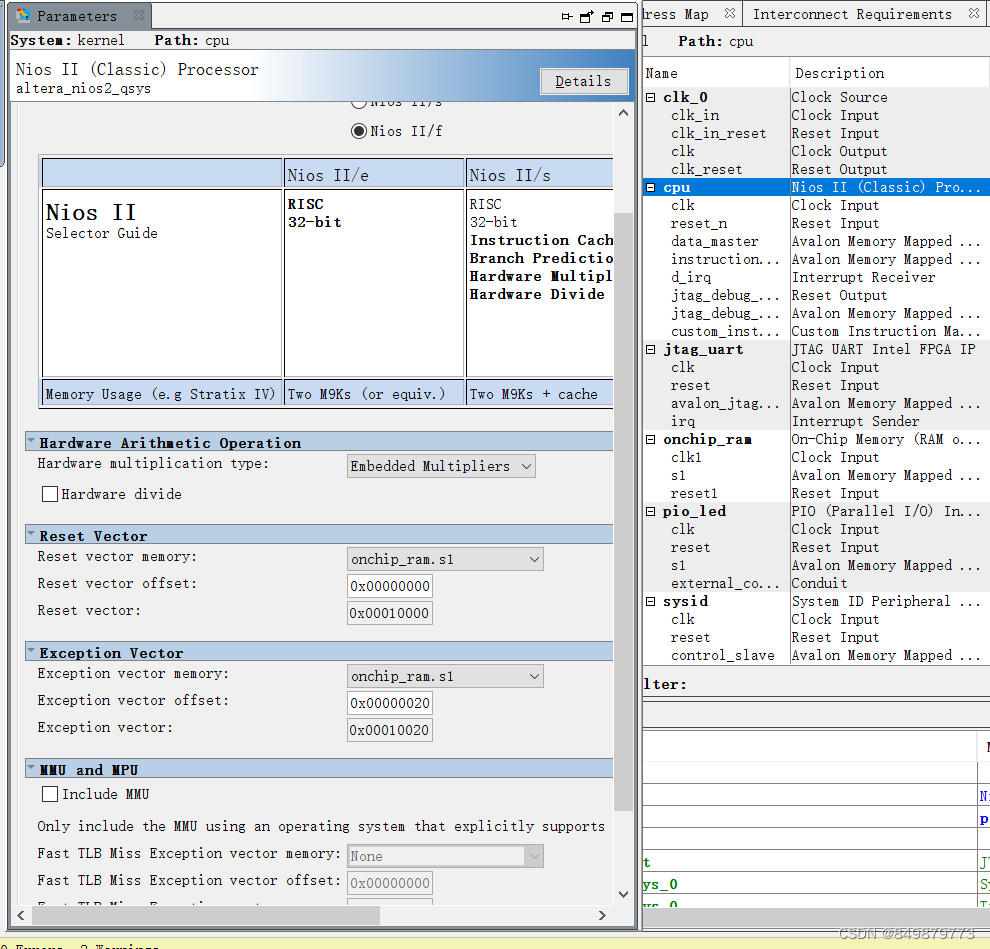

- 指定 NIos II 的复位和异常地址:选中CPU,单击右键,点击edit 进入 Nios II

Processor 的配置界面,配置 Reset Vector 和 Exception Vector 为

”onchip_ram.s1”,点击 Finish。

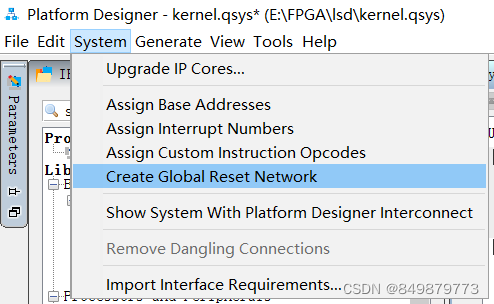

- 点击 Qsys 主界面菜单栏中的 ”System” 下的 ”Create Global Reset Network”。完成后会自动连接所有复位端口

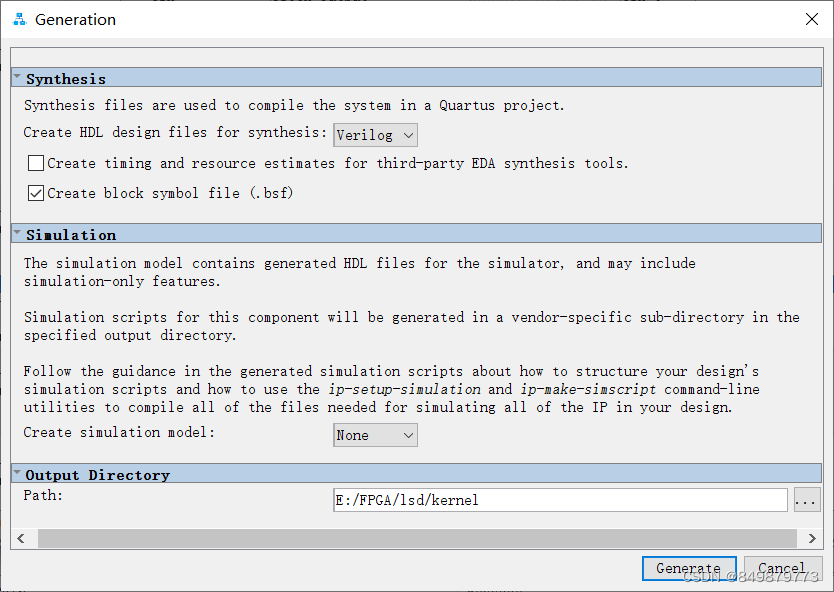

- **生成 Qsys 系统:**点选 ”Generation HDL” 标签栏中 Generate 按钮生成 Qsys 系统,保存文件

4.3 进行逻辑连接

4.3.1 在 Quartus-II 中新建一个原理图

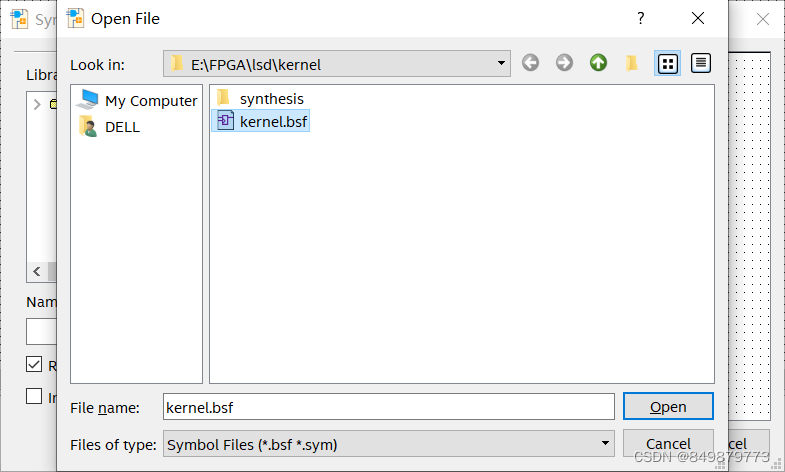

在该原理图(BDF)文件中添加 Qsys 生成的系统符号

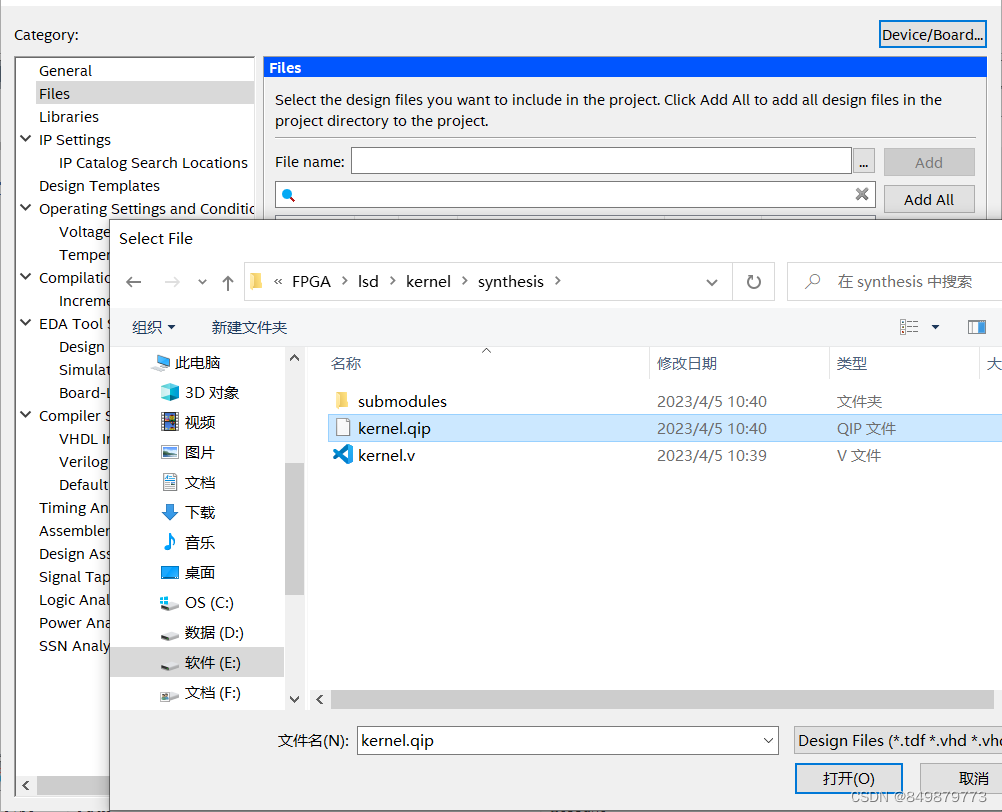

点击菜单 Project-add/remove files in project,来到如下界面,点击右侧浏览按钮找到如图所示的 qip 文件,选择并点击 add 添加。

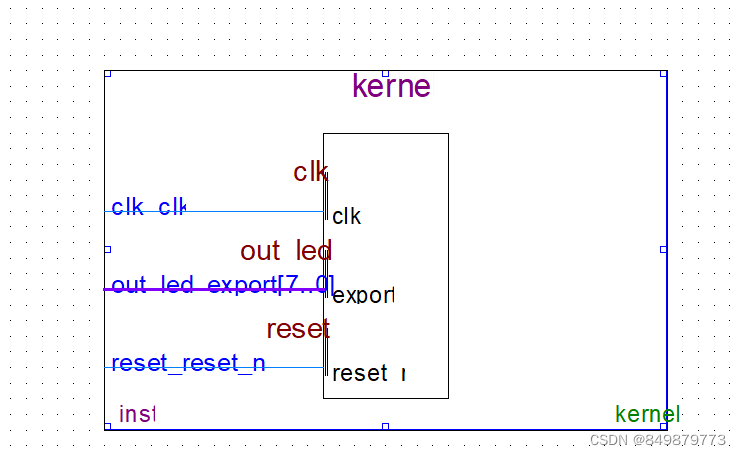

4.3.2 进行逻辑连接和生成管脚

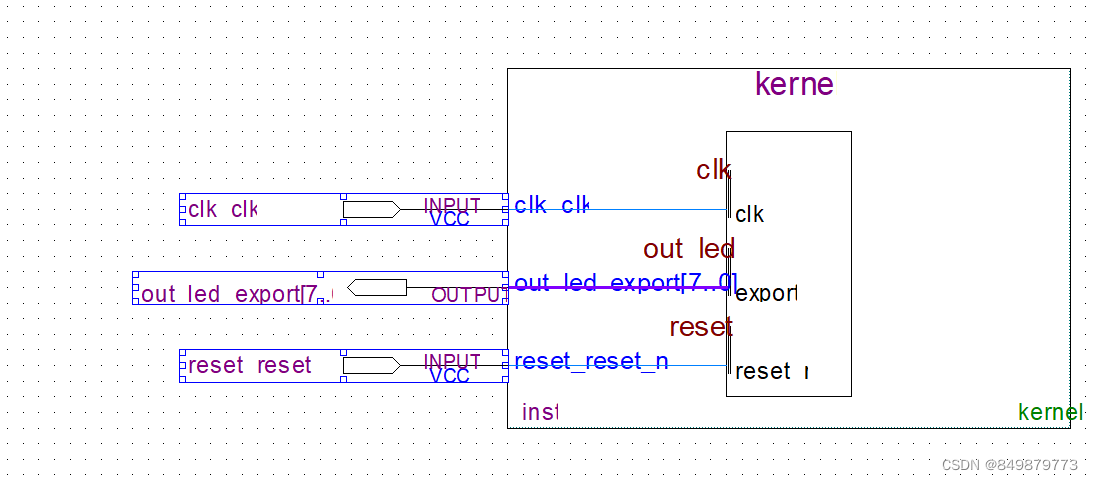

在 kernel 模块内点击鼠标右键选取 Generate Pin for Symbol Ports 生成管脚,然后将管脚命名如下

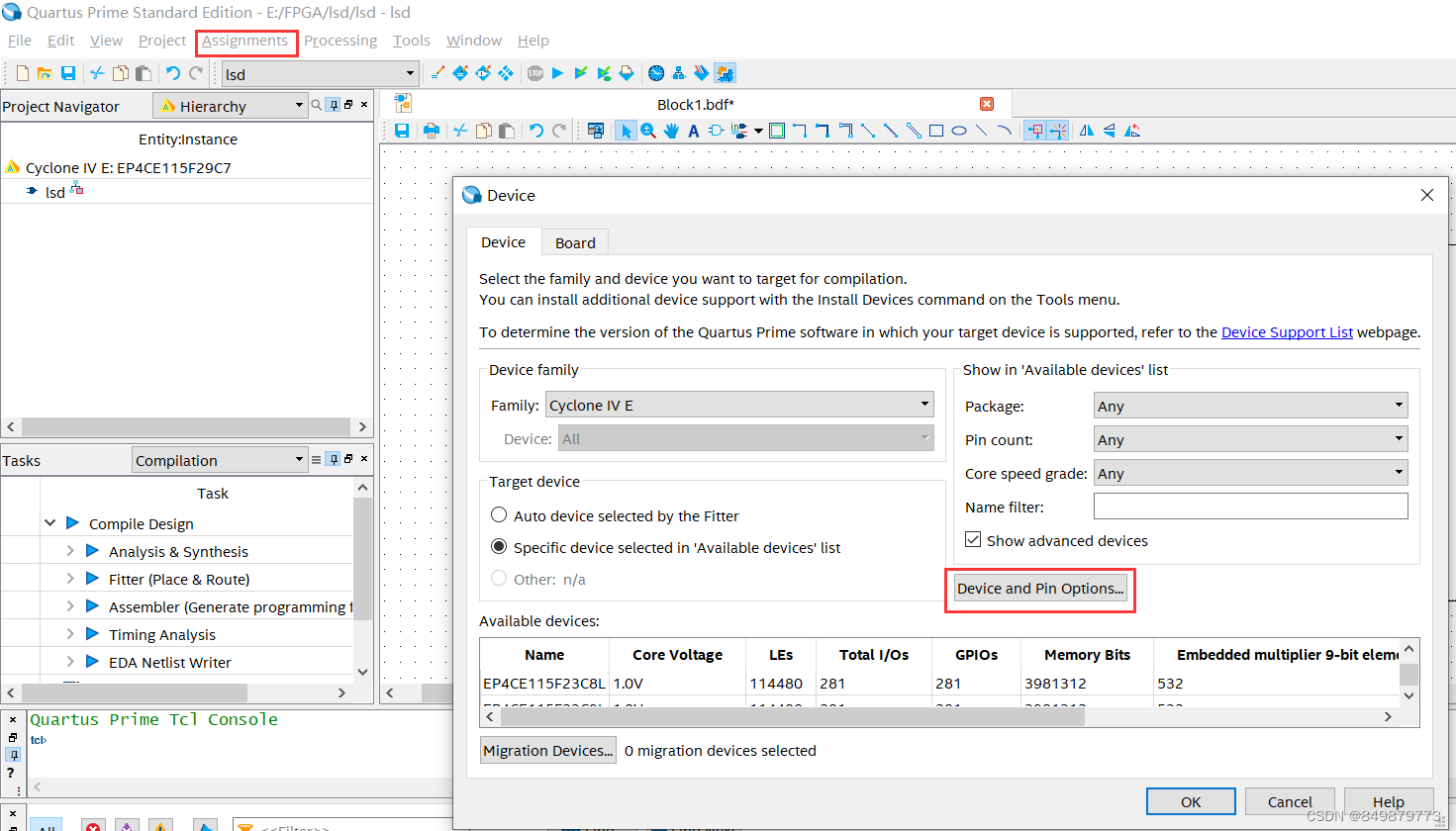

菜单里选择 Assignments-device,然后如下图所示点击 Device pin options

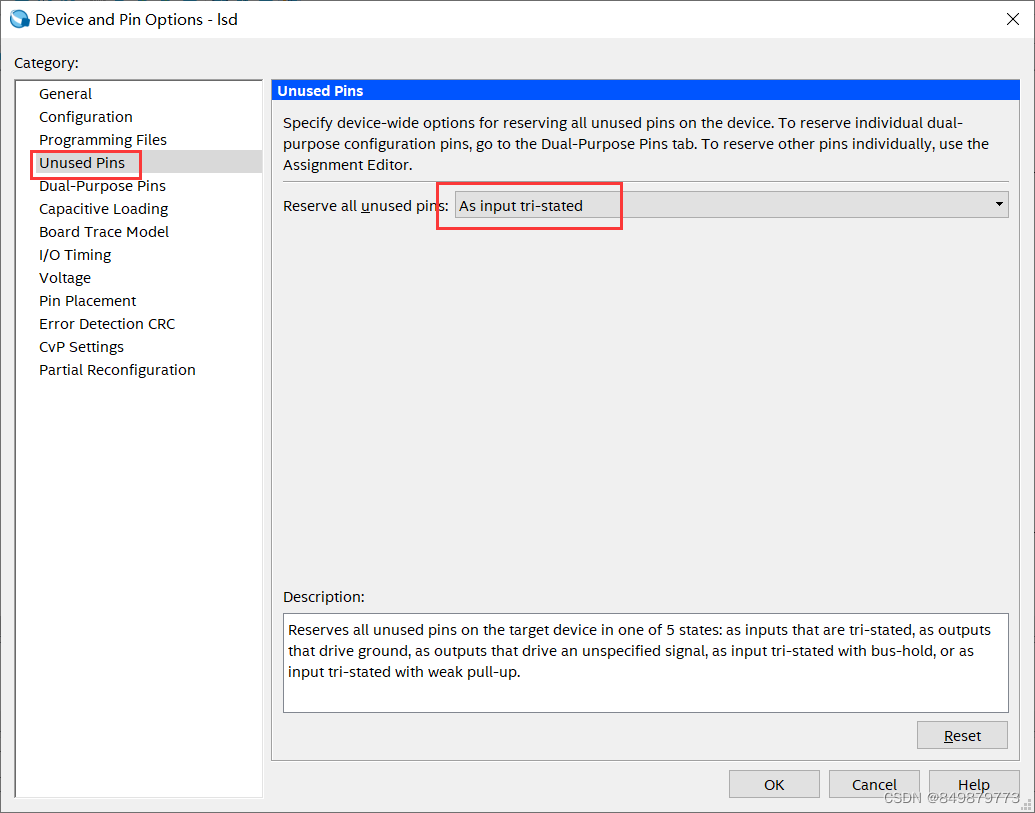

进行 unused pin 设置,可能会收到外部信号的干扰,将未用引脚设置为 As input tri-stated

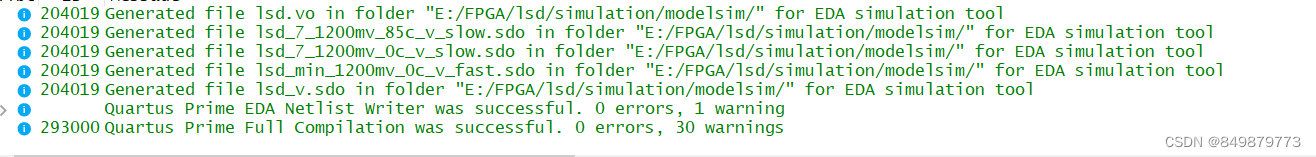

4.3.3 编译

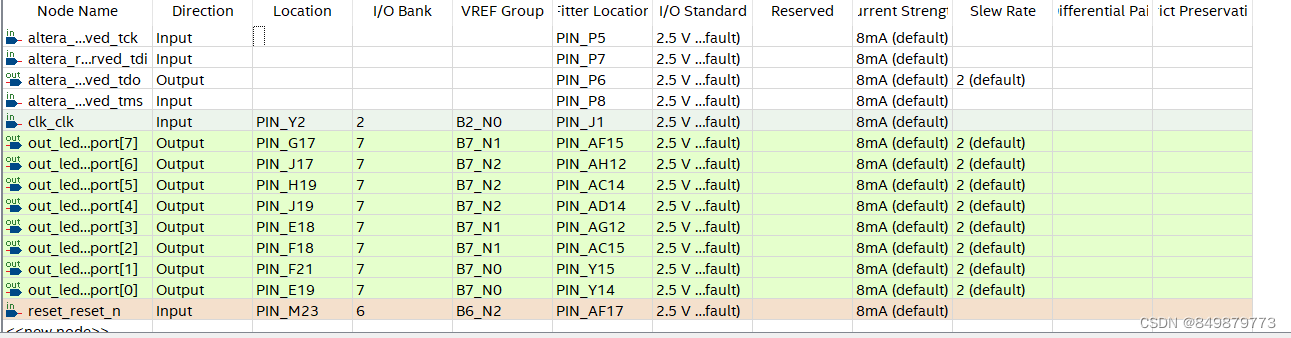

4.3.4 绑定引脚

分配物理针脚,重新编译

5. 软件设计

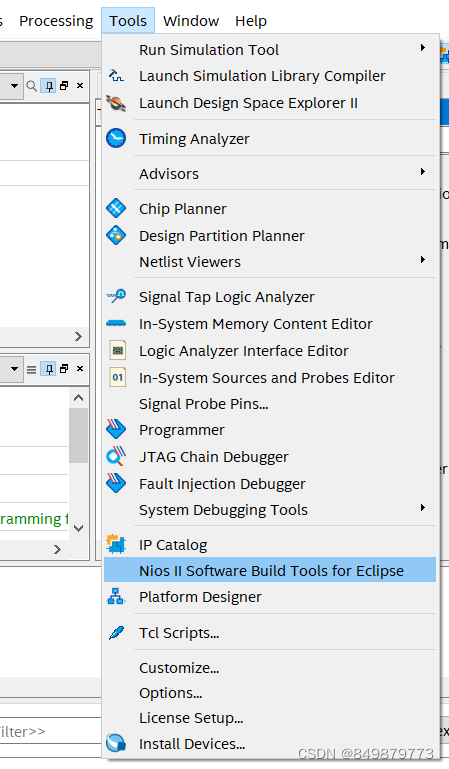

使用 Nios II Software Build Tools for Eclipse 来完成当前项目的软件开发

点击 Tools,然后点击 Nios II Software Build Tools for Eclipse 打开 Nios II SBT for Eclipse

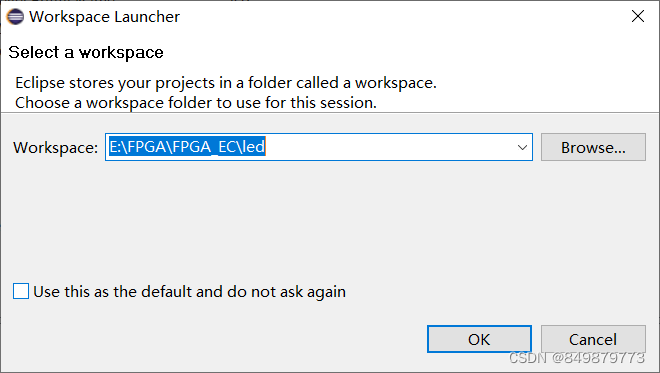

启动 Workspace选择当前的项目目录,点 OK

5.1 创建工程

在 SOPC Information File name 窗口中选择 kernel.sopcinfo 文件,以便将生成硬件配置信息和软件应用关联,CPU 栏会自动选择”CPU”。在 Project name 输入 ”hello_world” ,Project template选择 Hello World。

5.2 代码

将 hello_world.c 中的程序修改为流水灯控制程序

#include "system.h"

#include "altera_avalon_pio_regs.h"

#include "alt_types.h"

const alt_u8

led_data[8]={0x01,0x03,0x07,0x0F,0x1F,0x3F,0x7F,0xFF};

int main (void) {

int count=0;

alt_u8 led;

volatile int i;

while (1)

{

if (count==7)

{count=0;}

else

{count++;}

led=led_data[count];

IOWR_ALTERA_AVALON_PIO_DATA(PIO_LED_BASE, led);

i = 0;

while (i<500000)

i++;

printf("Hello world!\n");

}

return 0;

}

5.3 编译

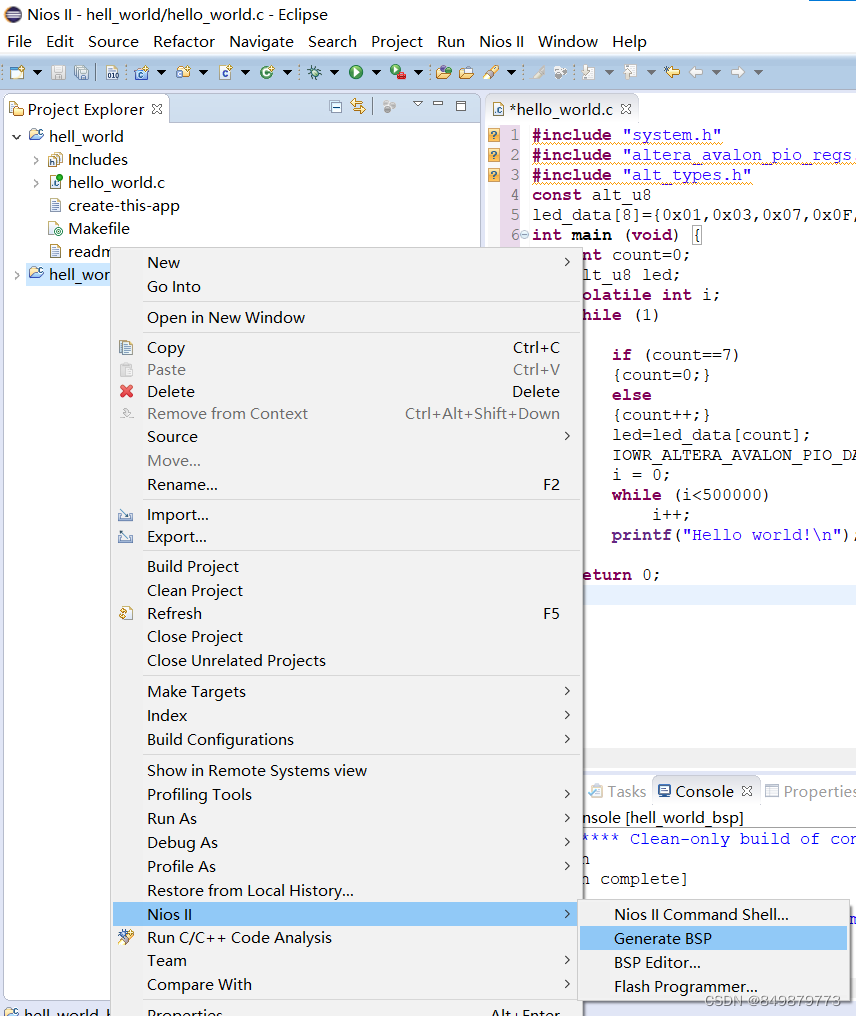

选择hello_wold_bsp,右键后,选择Nios II中的Generate BSP

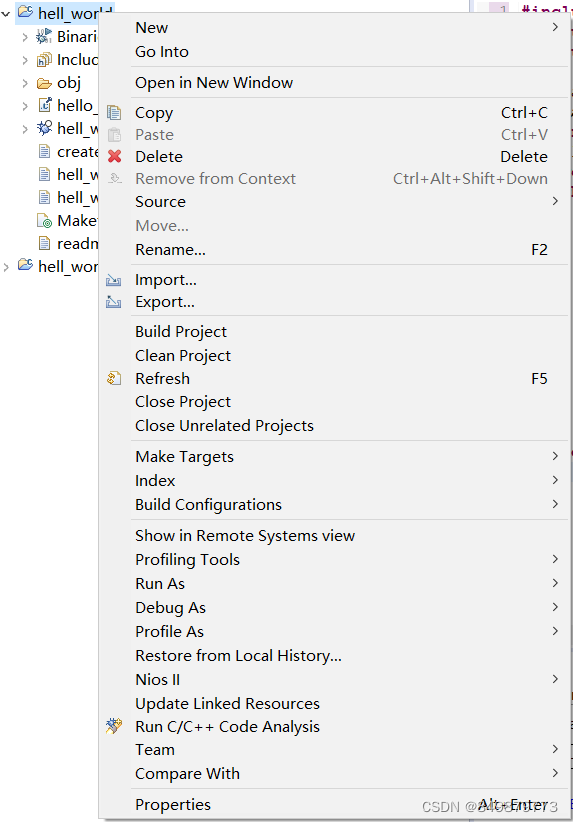

右键单击项目名称,在弹出的菜单中选择 Build Project

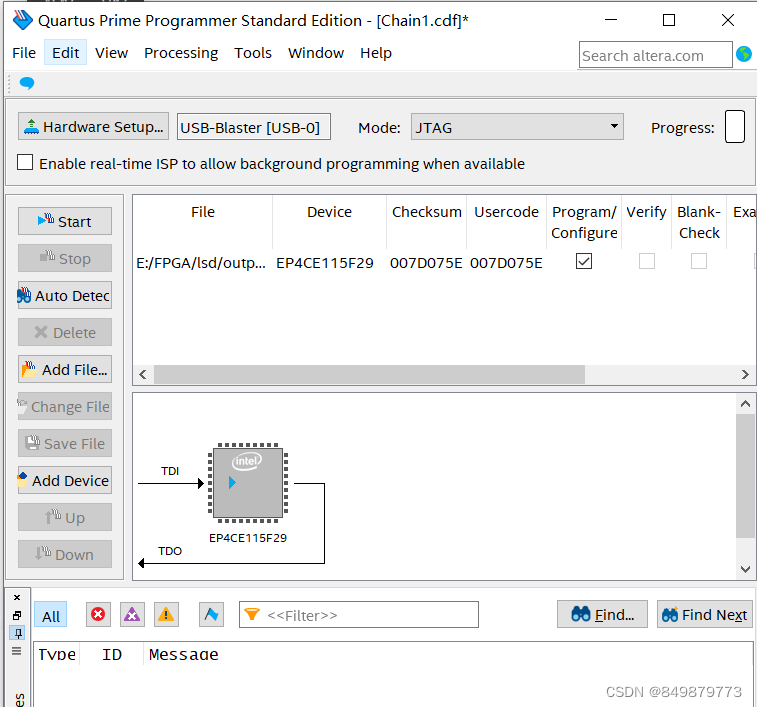

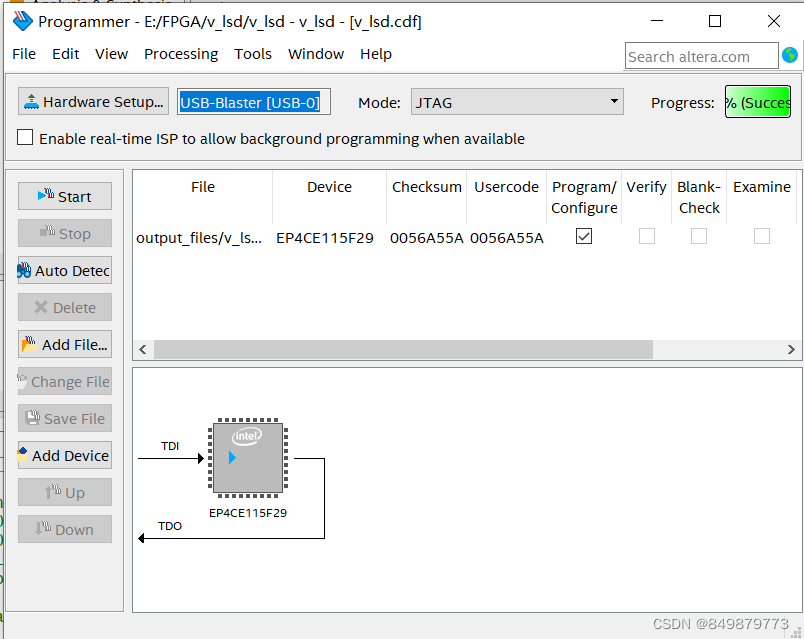

6. 烧录

把开发板接上电源,USB 接口接电脑。打开电源开关(注意不用下载时请一定关闭开关,以免烧坏板子)。点击软件工具栏上的按钮 ,则出现下载界面。第一次下载需安装硬件。即在下载界面中点击按钮“hardware setup…”,然后在弹出的对话框中选择“USBblaster”,再点击“ok”,则硬件被安装上。

安装好硬件后,在output_files中添加相应的下载文件

运行调试程序

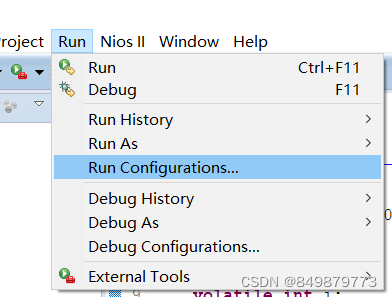

用户将运行程序来观察编译代码的执行,在菜单栏中选择 Run →Run Configurations

配置 Run Configurations,转到 ”Target Connection” 标签栏,点击右侧的 Refresh

Connections 将 USB-Blaster 加入

效果:

7. verilog语言实现流水灯

新建项目

流水灯代码:

module v_lsd (

input wire clk ,

input wire rst_n ,

output [7:0] led

);

parameter CNT_MAX = 26'd5000_0000;

reg [25:0] cnt_1s;

wire flag_1s;

reg [7:0] led_reg;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

cnt_1s <= 26'd0;

else if(cnt_1s >= CNT_MAX - 26'd1)

cnt_1s <= 26'd0;

else

cnt_1s <= cnt_1s + 26'd1;

end

assign flag_1s = cnt_1s >= CNT_MAX - 26'd1;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

led_reg <= 8'b1111_1111;

else if(flag_1s)

if(led_reg == 8'b1111_1111)

led_reg <= 8'b0000_0001;

else

led_reg <= {led_reg[6:0],led_reg[7]};

else

led_reg <= led_reg;

end

assign led = led_reg;

endmodule

烧录:

8.总结

这次试验内容较多,实验的时间比较紧,所以比较仓促,也没有来得及截图,离开实验室后才重新做了一遍,所以有些步骤可能不全,但是通过实验熟悉了NIOS-II软核的基本操作,也对FPGA开发板的外设以及变成有了更进一步的认识.

9.参考文章

https://blog.csdn.net/Mjing11/article/details/116101156

https://blog.csdn.net/xwmrqqq/article/details/115937457?spm=1001.2101.3001.6661.1&depth_1-utm_relevant_index=1

本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有涉嫌抄袭侵权的内容,请联系:hwhale#tublm.com(使用前将#替换为@)