任何学习嵌入式/单片机的朋友都绕不开ARM,但初学者总是对ARM架构、内核、指令集等相关概念不够清晰或者混淆,本文帮助入门的朋友彻底弄清楚。

目录

1.芯片、CPU、SOC

2.ARM公司

3.ARM架构与内核、指令集

3.1架构与内核

3.2架构与指令集

4.ARM架构和处理器发展史

4.1ARM架构

4.2ARM处理器

原文地址:一文彻底分清ARM架构、内核、指令集等相关概念

1.芯片、CPU、SOC

在谈论ARM之前,必须把芯片、CPU、SOC这些概念解释清楚,芯片是一个广泛的词语,属于半导体元件的总称。英语会更准确:integrated circuit(集成电路)。很多人把芯片等同于CPU,这显然是错误的。CPU只是属于芯片这个概念范围内的一种。

而我们日常所谈论的手机处理器往往指的是SOC。SOC全称System on Chip,即片上系统,也就是集成了很多东西在一个芯片上,简单地说SOC包含了CPU加上很多其他模块。

复杂地说SOC包含了微处理器(MPU Micro Processor Unit)、数字IP核、模拟IP核和存储器。微处理器,也即是逻辑核,包括CPU、时钟、中断控制器、I/O端口以及用于各种IP核之间的粘合逻辑等等,负责系统的控制。数字IP核包含了我们的加速器,能够减轻处理器的计算负担。模拟IP核包含了ADC、DAC、PLL等模拟电路,负责与外界的模拟信息进行数据传输。存储器包括各种易失、非易失以及Cache等存储器,用于储存系统运行的代码以及数据。

这里要指出一个概念上的CPU问题,CPU其实是一个相对概念(注意理解Unit单元),当我们指手机的CPU,就是指这个手机的中央处理单元,也就是SOC,比如高通骁龙888,当我们指SOC的CPU则是指SOC中的中央处理器单元,也就是微处理器(MPU),当我们指MPU的CPU时,则是指MPU的中央处理单元。你要是看多了英文资料,你就会发现老外很少用CPU这个词,而基本上都用Processor处理器,有处理功能的都可以叫处理器。

附:MCU(MicroController Unit)和SOC并没有特别本质的区别,SOC比MCU集成了更多东西,更强大而已。而单片机这个概念更是广泛,MCU和SOC都可以称为单片机,不详细论述了。如51、STM32F1、STM32F4等都可以叫MCU,而STM32MP、S3C2440、IMX6ULL、高通骁龙、海思麒麟等都可以叫SOC,他们也都可以被叫做单片机,当然一般来说单片机指的是MCU。

2.ARM公司

首先ARM是家公司,在1990年成立,全名是“Advanced RISC Machines Ltd.,”——先进精简指令集机器公司.ARM公司是一家知识产权(IP)供应商,它不制造处理器,而是设计,售卖设计器方案(不止设计处理器,但主要是处理器)。

ARM公司的历史就不赘述了,感兴趣的直接去他官网就能知道。https://www.arm.com/

也就是说ARM公司设计出一种处理器设计方案,然后其他有制造SOC、MCU需求的公司,比如三星、ST、TI、IMX、华为等,去购买ARM公司的方案,在他的基础上删删改改,加些外围东西变成自己想要的SOC、或MCU设计,再去找制造公司生产。

3.ARM架构与内核、指令集

3.1架构与内核

首先要理解架构是什么东西。架构指的是一种大体上的方案,比如造房子,高楼、平房、独栋别墅,这就是三种不同的架构。

你想造一个房子,在具体的细节实现之前,你必须思考,我到底要造高楼、平房、独栋别墅.........然后我确定我要造平房,什么样的平房?我要造三室一厅的平房,这就是一种基于平房架构的内核,我要造四室一厅的平房,这就是基于平房架构的另外一种内核。

先有架构,再有内核,一个架构可以衍生出多种内核

内核之所以称之为内核,是因为他是在SOC、MCU内部中最核心的逻辑处理部分,就是SOC、MCU的CPU。所以内核也可以叫做处理器。

别的公司可以向ARM公司购买架构使用权,ARM给你架构,你自己去设计内核,这就是自研内核,比如三星、高通、苹果公司都有基于ARM架构的自研内核。ARM公司自己针对自己架构设计的内核又称作公版内核,别的公司也可以购买ARM的公版内核使用权,比如华为用的就是公版内核。

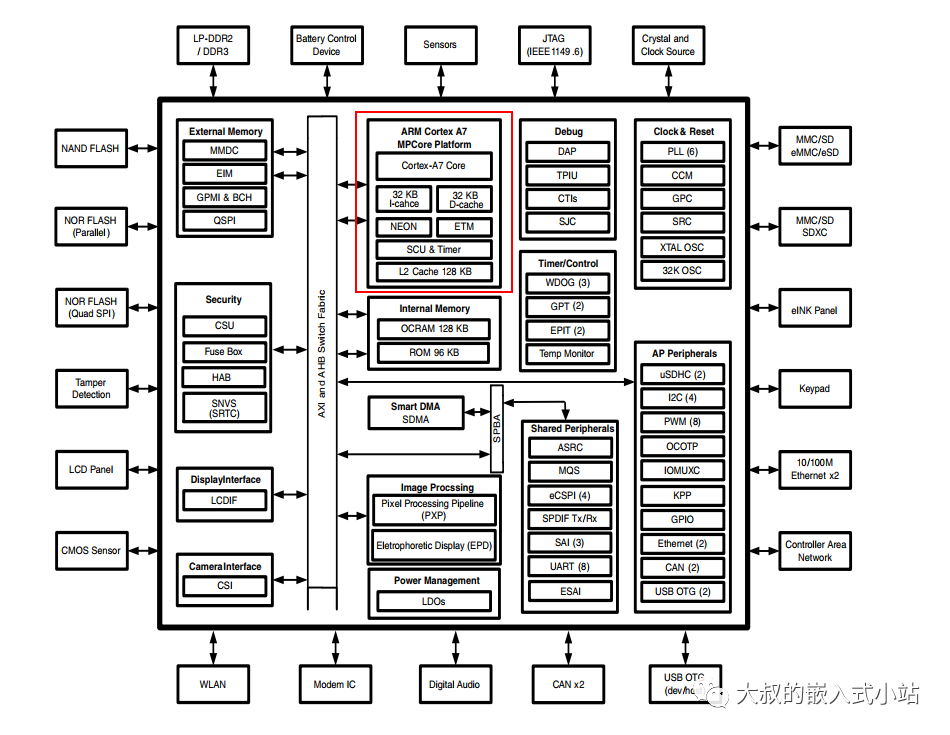

现以IMX6ULL芯片为例,IMX6ULL芯片,又可以叫IMX6ULL SOC。其内部组成如下:

用红框标出来的部分叫做内核,为ARM Cortex-A7,而这个内核时基于ARMv7-A 架构。

以STM32F407芯片为例,STM32F407芯片又可以叫做STM32F407 MCU(太大,只展示一部分):

内核为ARM Cortex-M4,而这个内核基于ARMv7E-M架构。

3.2架构与指令集

ARM架构和ARM指令集经常放在一起说。经常说成ARM指令集架构,实际上并不完全相等。

ARM架构包含了指令集、寄存器集、存异常模型、内存模型等内容。

指令集是指处理器能够识别并执行的指令集合。

ARM,Advanced RISC Machines,先进精简指令集机器,其中RISC是Reduced Instruction Set Computer的缩写,意为精简指令集处理器,ARM是RISC最突出的代表,其它比较有名的RISC指令集还有:MIPS,PowerPC,SPARC,RISC-V。

与RISC相对的是CISC,Complex Instruction Set Computer,复杂指令集处理器,闻名世界的X86指令集就是一种CISC指令集。

ARM指令集也是一个统称,实际上ARM指令集还分为 ARM64指令集、 ARM32指令集、THUMB指令集、THUMB-2指令集、NEON指令集、VFP指令集、DSP指令集。不同版本架构支持不同指令集。

4.ARM架构和处理器发展史

4.1ARM架构

ARMv1:1985年发布,最早的ARM架构。

ARMv2:1986年发布,改进了ARMv1,增加了32位地址总线和指令集扩展(增加了一些指令)。

ARMv3:1992年发布,支持虚拟内存、增加了指令集扩展,包括支持协处理器(coprocessor)。

ARMv4:1994年发布,增加了Java虚拟机指令集扩展(Jazelle)和Thumb指令集,提高了代码密度。

ARMv5:1997年发布,增加了支持嵌入式Java的指令集扩展(Jazelle-RCT)、增加了支持浮点运算的指令集扩展(VFP)。

ARMv6:2002年发布,增加了Thumb-2指令集,提高了代码密度和执行效率,同时也增加了一些指令集扩展,包括支持Jazelle-DBX。

ARMv7:2004年发布,增加了基于TrustZone的安全扩展、NEON指令集扩展,支持向量浮点运算(VFPv3)等。

ARMv8:2011年发布,增加了AArch64架构,支持64位处理器,同时保留了AArch32架构,提高了性能和能耗效率。

ARMv9:2021年发布,增加了Confidential Compute Architecture(CCA)和Realms技术,提高了安全性和隔离性。

4.2ARM处理器

针对每一种ARM架构,ARM都设计了很多的处理器(内核),这里就不列出来了,感兴趣去官网能够查找。这里主要讲讲命名的变化。

主要分为经典处理器、Cortex-M系列处理器、Cortex-R系列处理器、Cortex-A系列处理器

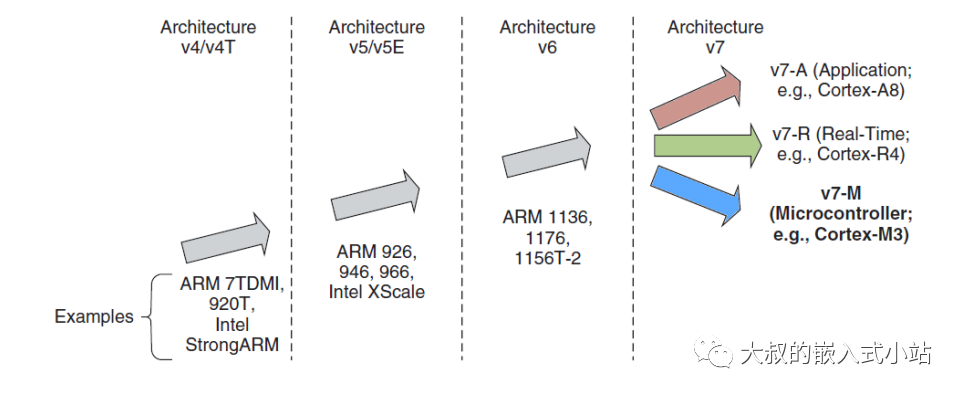

经典处理器都是按照数字命名的,直到ARM11。也就是推出架构v7的时候,ARM公司把产品并分为三大产品线,分别是Cortex-A、Cortex-R和Cortex-M。

近两年推出的cortex-X并不是单独的产品线,它可看做cortex-A的升级版,两者的市场定位是一样的。

Cortex-A系列处理器是针对高端应用而设计的,通常应用于智能手机、平板电脑、数字电视和网络设备等。这些处理器拥有高性能、大规模的内存管理单元以及大量的内部缓存,支持多核处理和虚拟化技术。

Cortex-R系列处理器是针对实时应用而设计的,通常应用于汽车、工业控制和医疗设备等。这些处理器拥有极低的延迟、高精度的计时器和内部存储器保护机制,能够在实时响应和高可靠性方面表现出色。

Cortex-M系列处理器是针对低功耗、低成本、嵌入式应用而设计的,通常应用于传感器、智能家居、工业控制和医疗设备等。这些处理器拥有低功耗、小尺寸和低成本等优点,同时也支持实时性、安全性和可靠性等特性。

原文地址:一文彻底分清ARM架构、内核、指令集等相关概念

系列文章合集:

FreeRTOS文章合集

嵌入式Linux基础文章合集

ARM学习系列合集

C语言学习系列合集

本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有涉嫌抄袭侵权的内容,请联系:hwhale#tublm.com(使用前将#替换为@)