目录

- 1. 前言

- 2. 设置与说明

- 2.1 PS UltraScale+ Block Design

- 2.2 I/O Configuration

- 2.2.1 Bank0-3电压:

- 2.2.2 Low Speed

- QSPI

- SD卡

- CAN

- I2C

- PMU GPO

- UART

- GPIO

- SWDT and TTC

- 2.2.3 High Speed

- GEM

-

- 2.2.4 Reference Clock

- 2.3 Clock Configuration

- 2.4 DDR Configuration

- 2.5 PS-PL Configuration

- 2.6 最终效果图

1. 前言

2. 设置与说明

2.1 PS UltraScale+ Block Design

图形化设置界面,可以快速定位到需要勾选的外设或者资源。

最终设置完成的效果如下图。

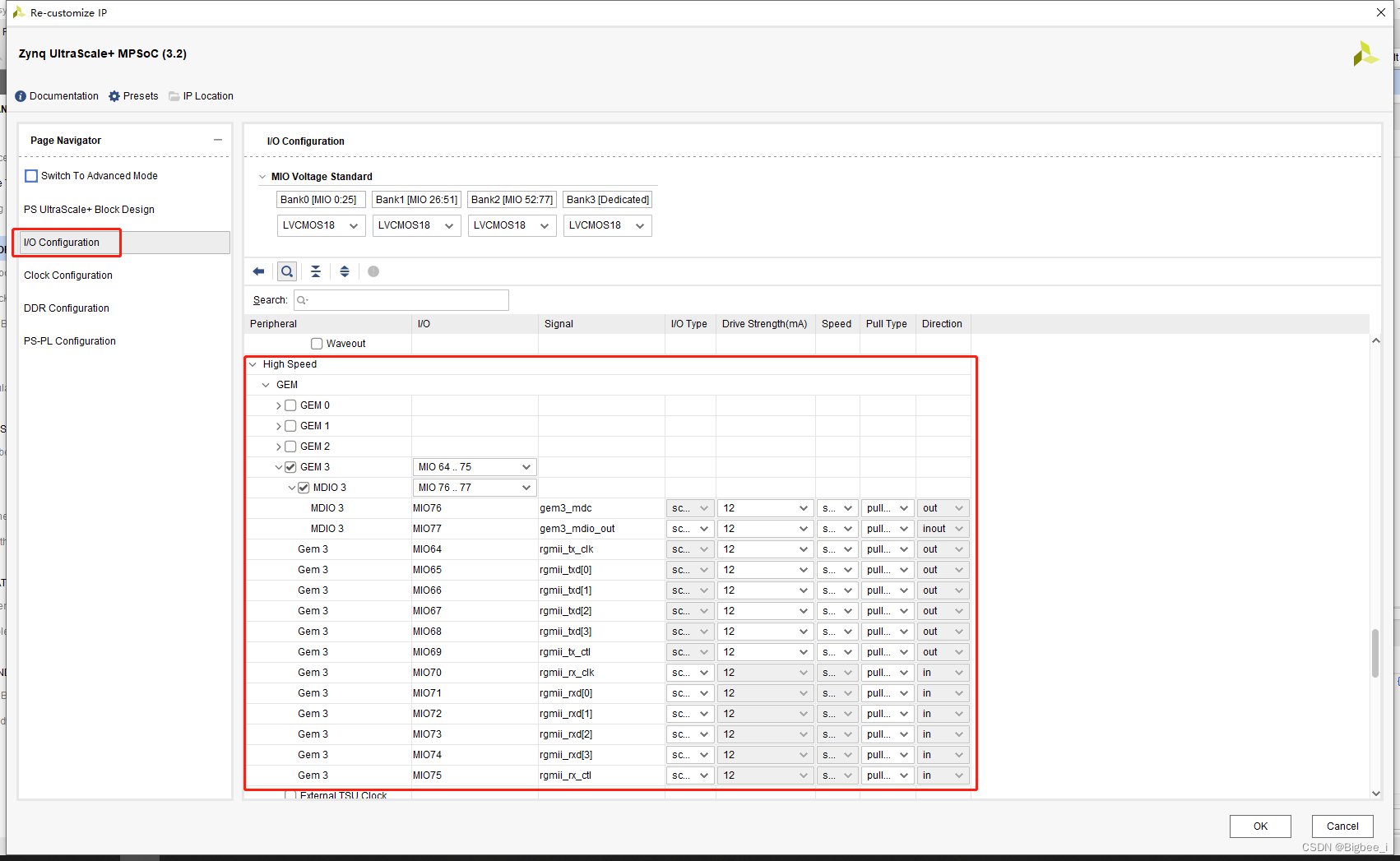

2.2 I/O Configuration

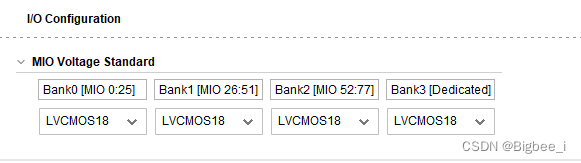

2.2.1 Bank0-3电压:

Bank电压是由硬件电路决定的,ZCU102的4个Bank电压都是LVCOMS18

2.2.2 Low Speed

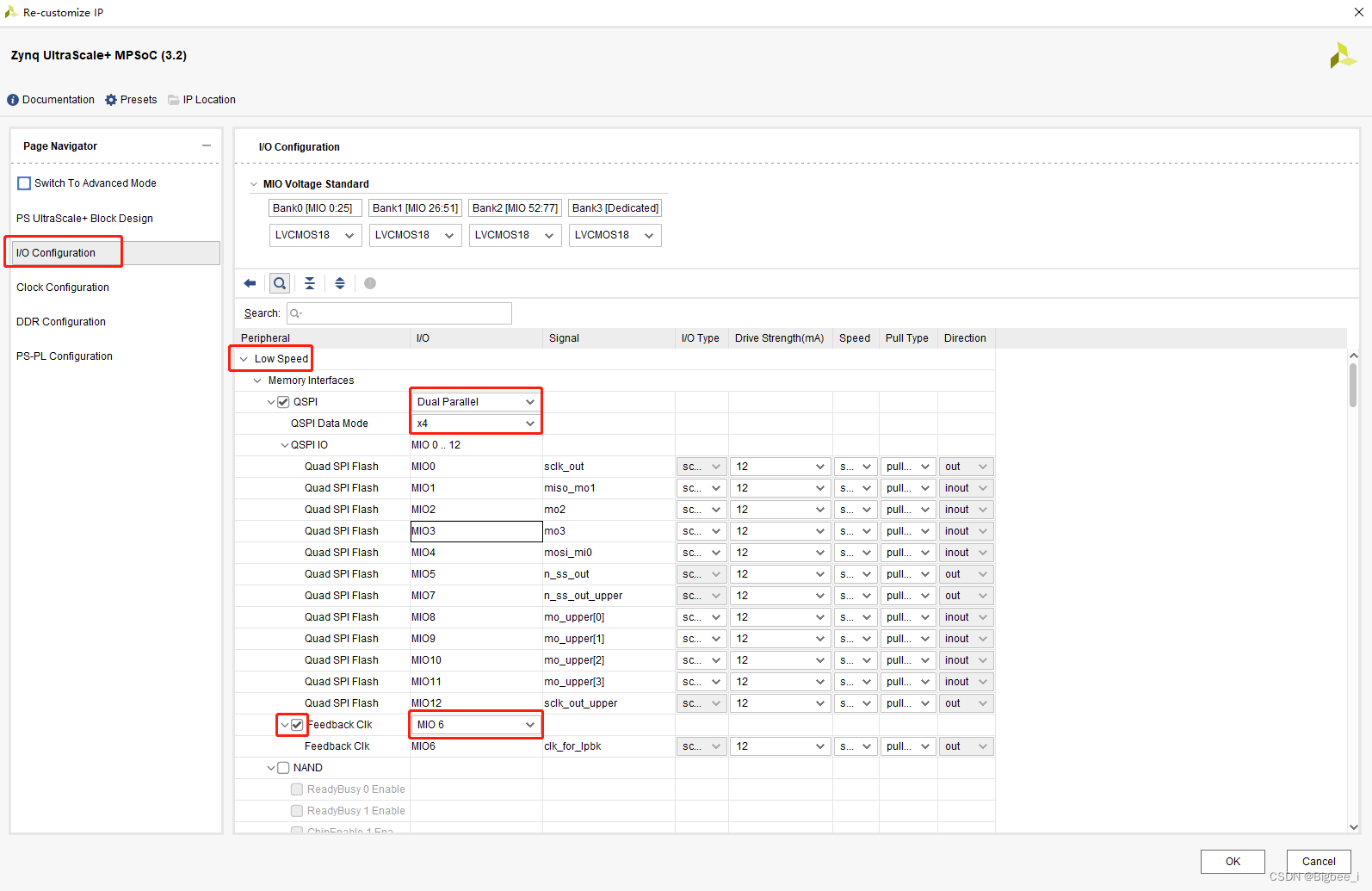

QSPI

- 选择Dual Parallel x4,平行放置的两块Flash,共同构成8位的Flash

- 使能Feedback Clk

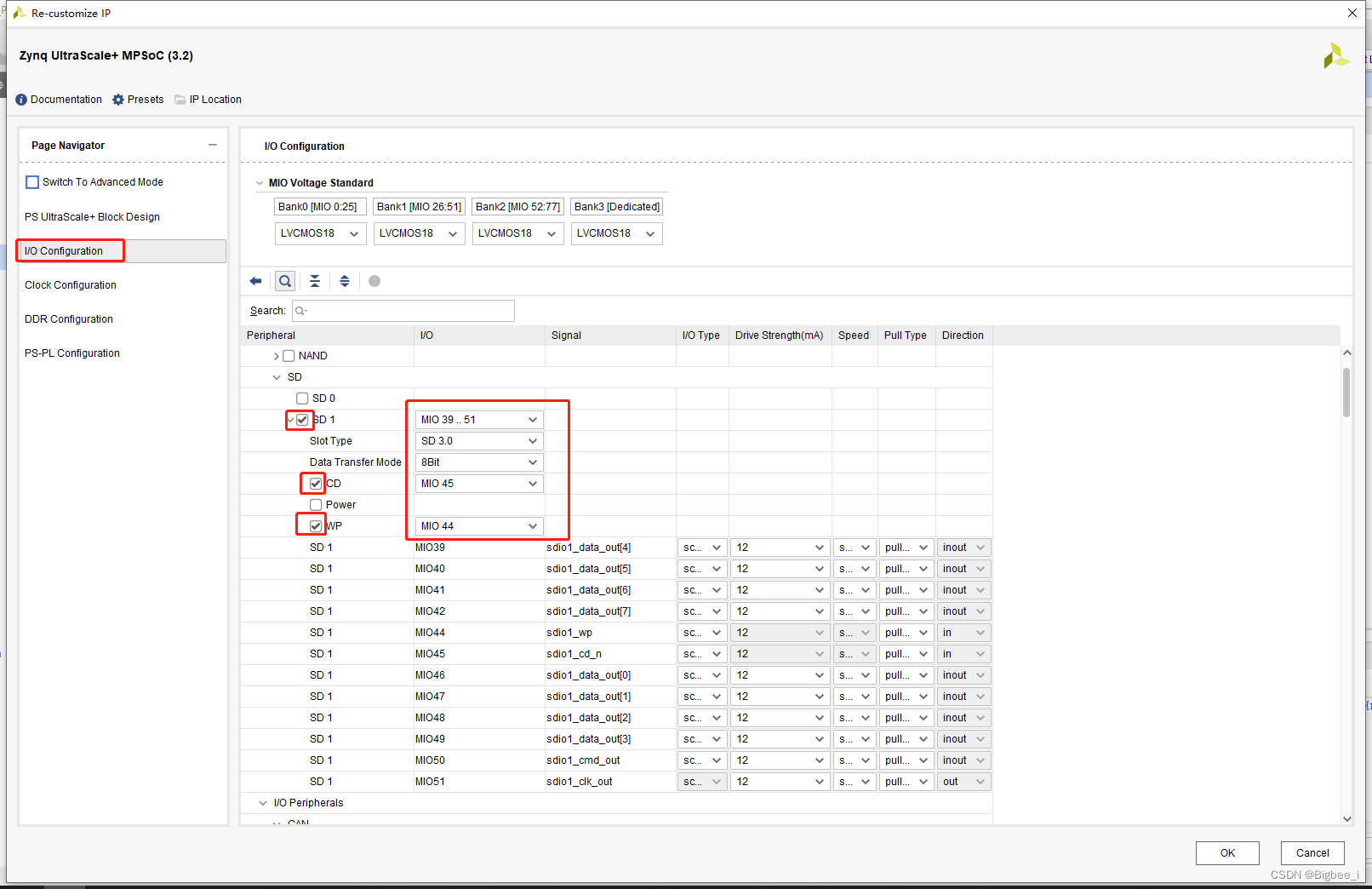

SD卡

- 选择MIO39-51

- 使能CD MIO45

- 使能WP MIO 44

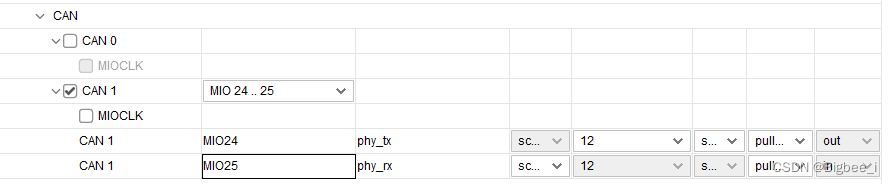

CAN

使能CAN1 MIO24,25

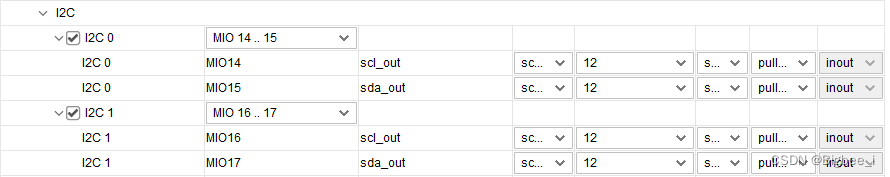

I2C

使能I2C0和I2C1

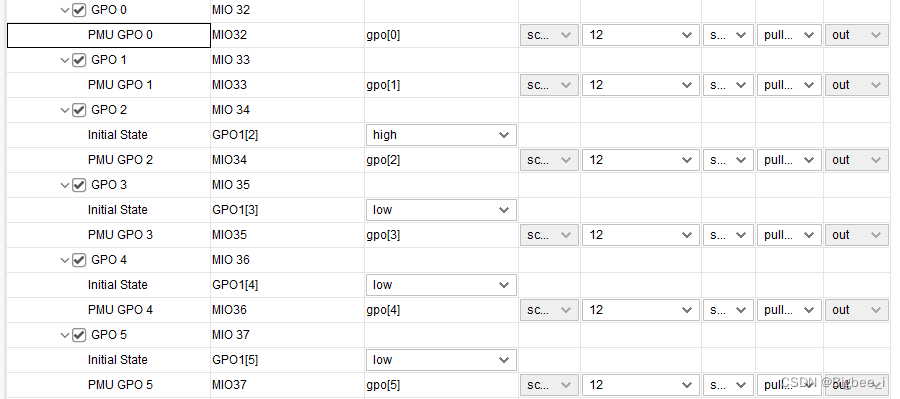

PMU GPO

PMU GPO0~5

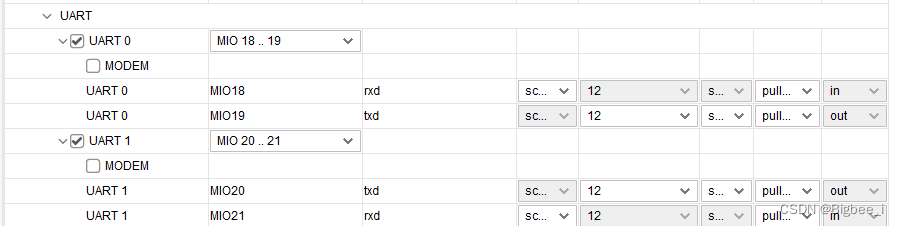

UART

使能UART0-1,ZCU102使用的UART转USB,一个USB集成了四路的UART(写博客说明)

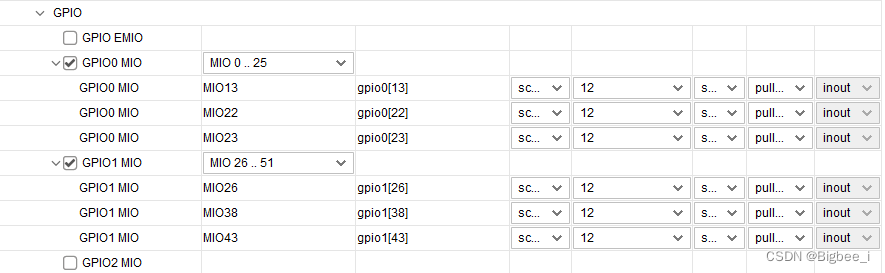

GPIO

GPIO按照需求选择

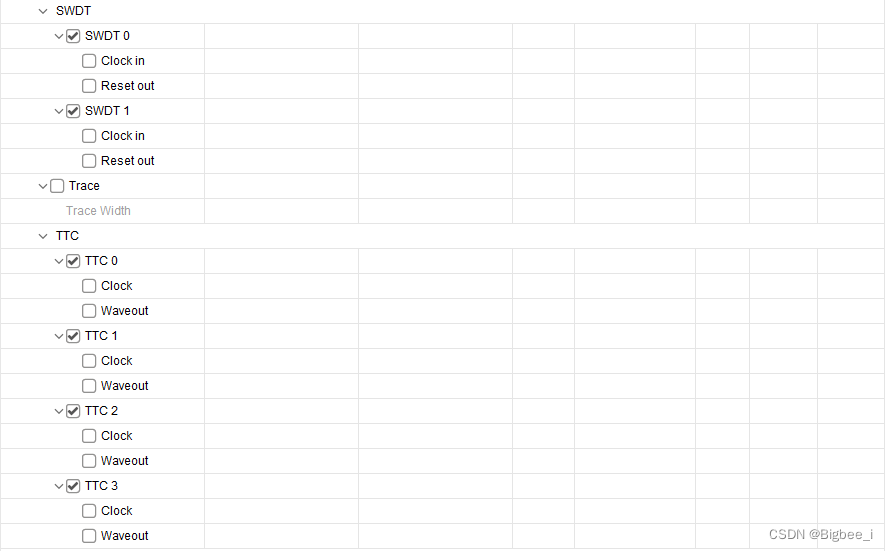

SWDT and TTC

SWDT 和TCC都选上

2.2.3 High Speed

GEM

使能GEM3

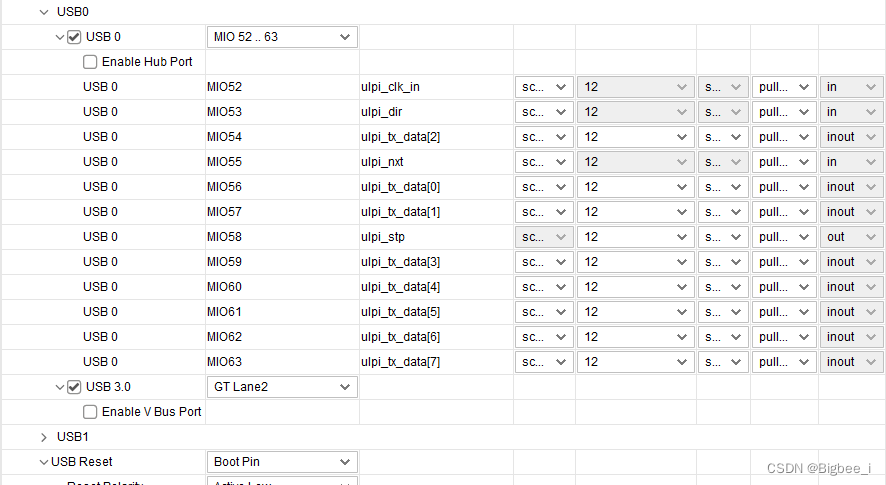

USB

- 使能USB0

- 同时使能USB3.0 GT Lane2

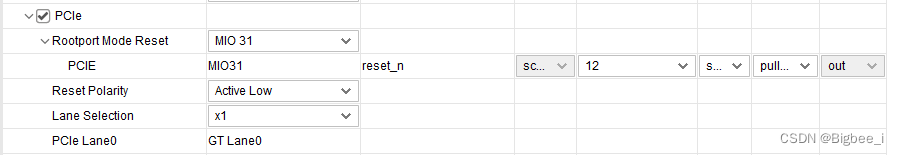

PCIe

- 选择GT Lane0

- ZCU102应该是支持x4的,这里选择x1

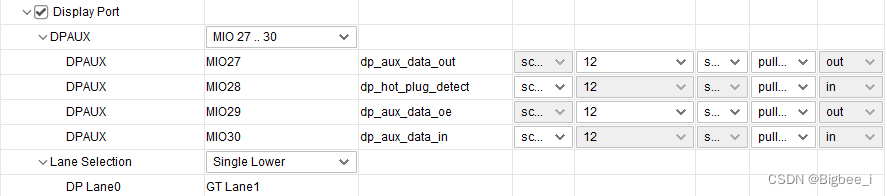

Display port

- 使能Display Port MIO27~30

- Single Lower

- GT Lane1

SATA

- GT Lane3

其他都不勾选或保持默认。

2.2.4 Reference Clock

参考时钟不勾选

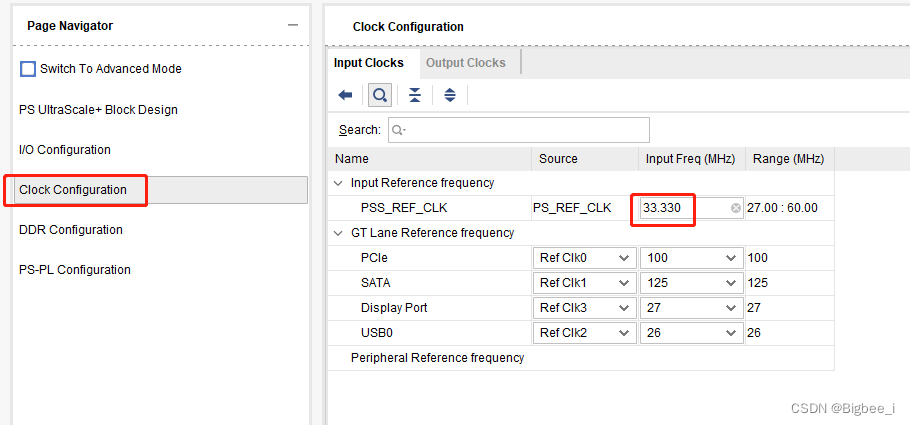

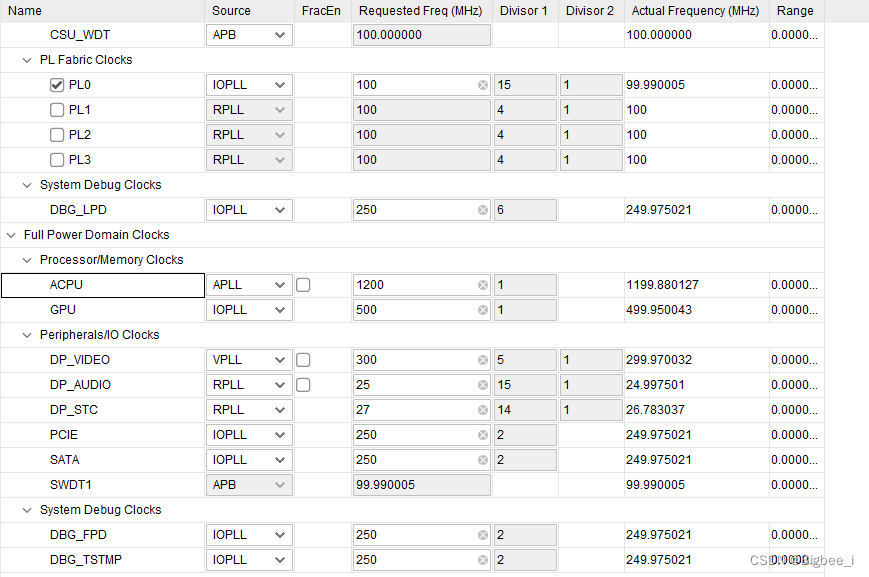

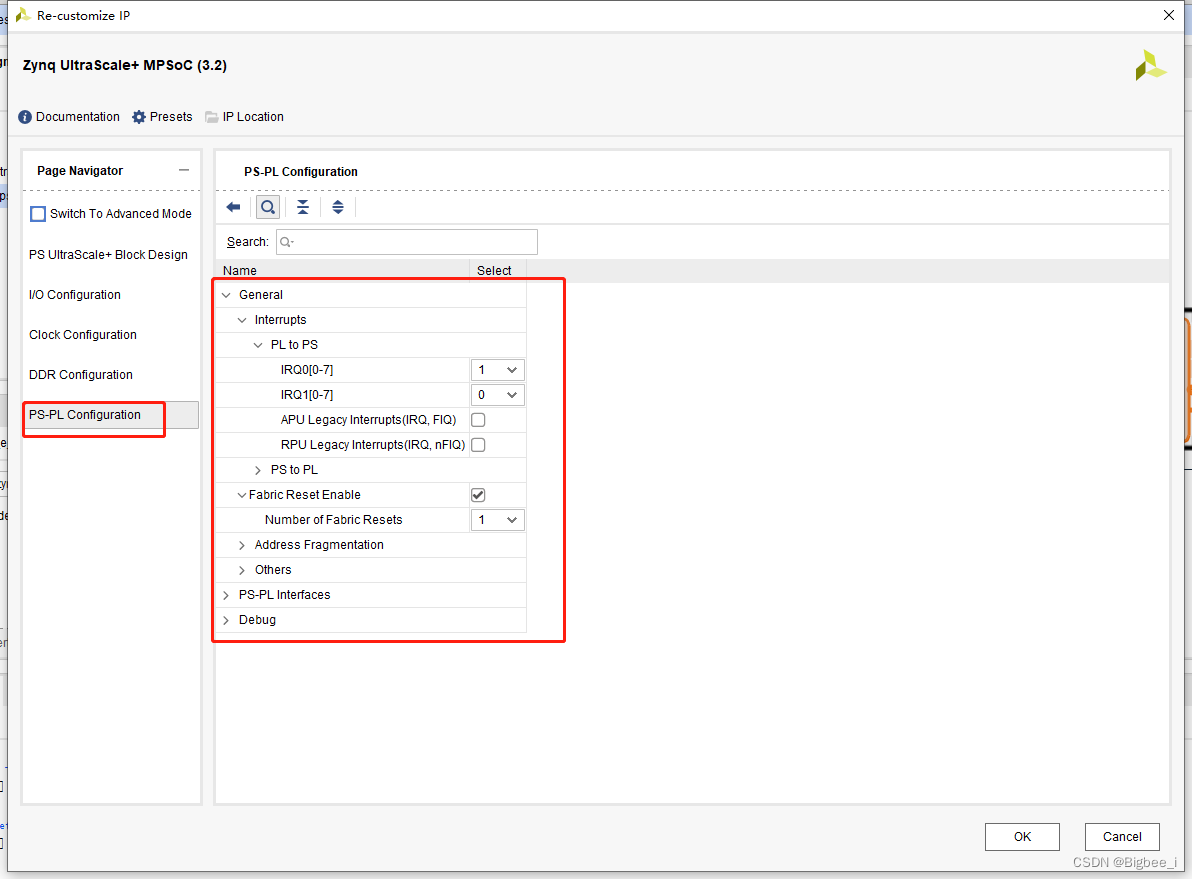

2.3 Clock Configuration

Input Clock

- PS端参考时钟,默认33.33MHz

- PCIe 100MHz

- SATA125MHz

- Display Port 27MHz

- USB0 26MHz

Output Clocks

选择时钟的源头,由那个PLL提供。

按照下图进行设置。

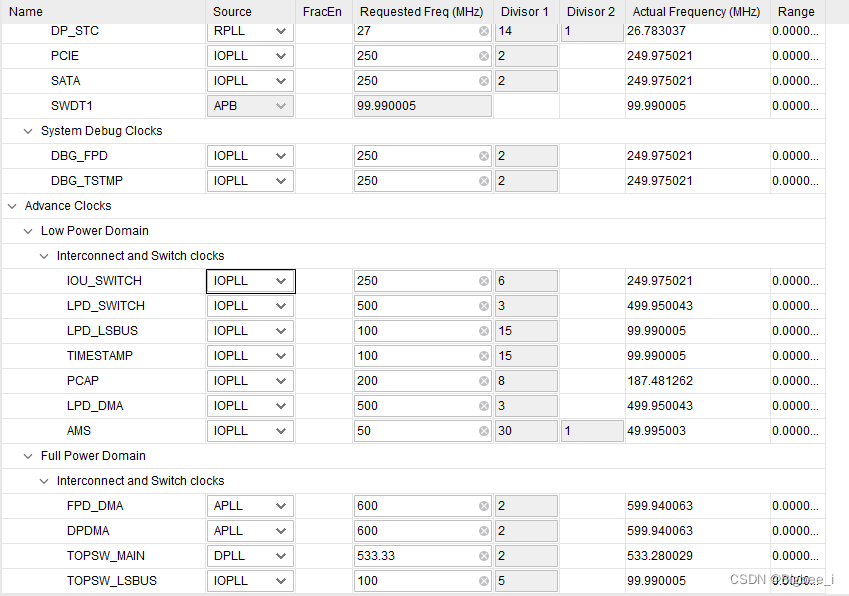

2.4 DDR Configuration

这个设置很重要!!!

DDR4设置

- 选择型号DDR4_MICRON

- Bus Width修改为16bits

- Device Capacity修改为8192 MBits

- Cas Write Latency修改为11cycles

- Row Address Count 修改为16bits

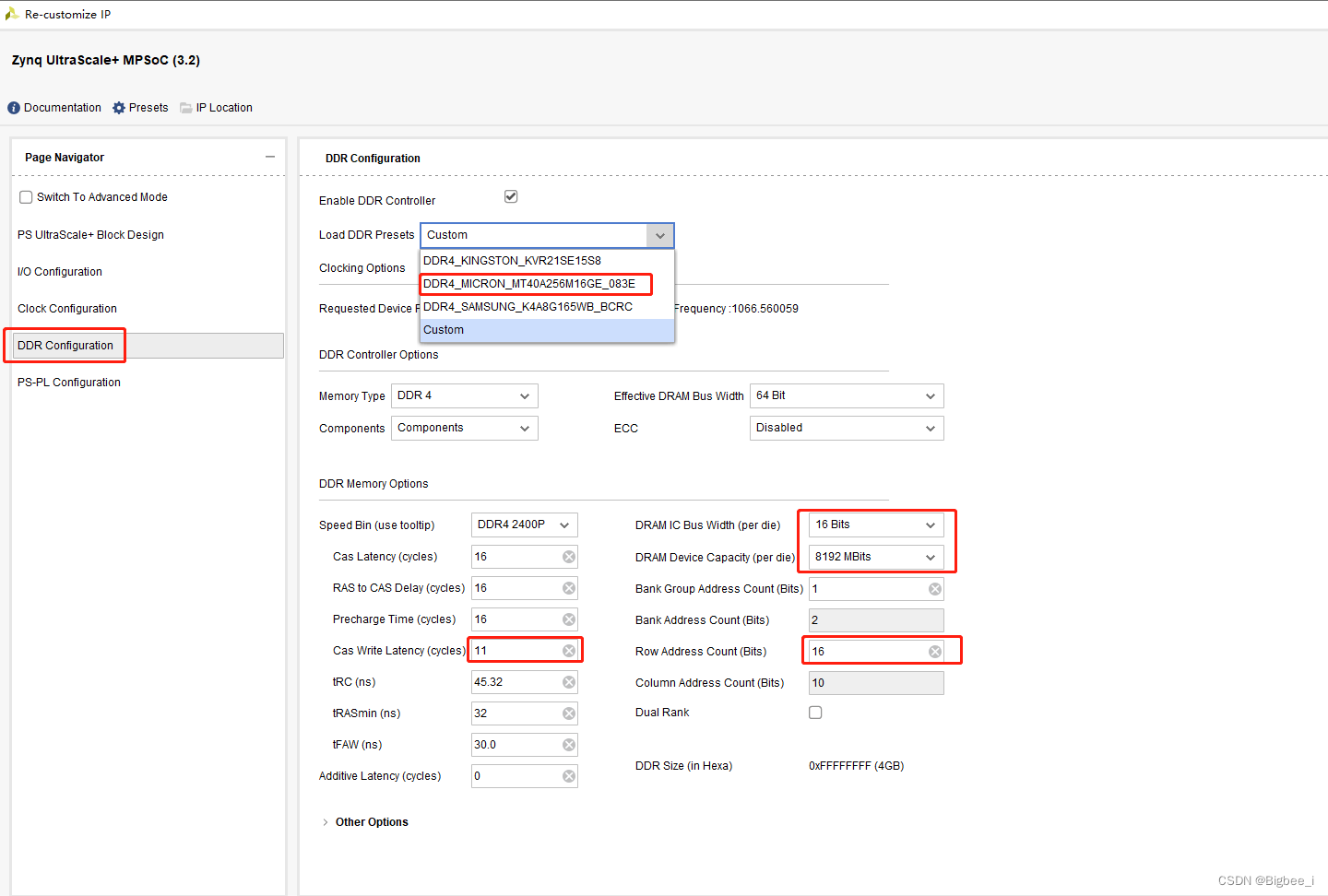

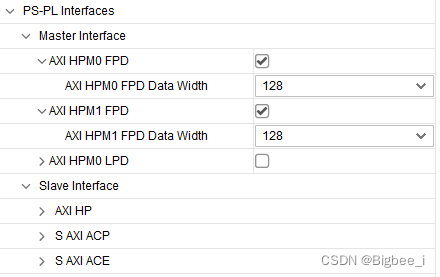

2.5 PS-PL Configuration

这个是PS与PL的交互部分,按照需求进行修改。

-

General 使能了一个PL to PS 的IRQ中断

PS-PL Interfaces

-

使能了两条PS做主,PL做从的HPM总线,位宽默认为128bit

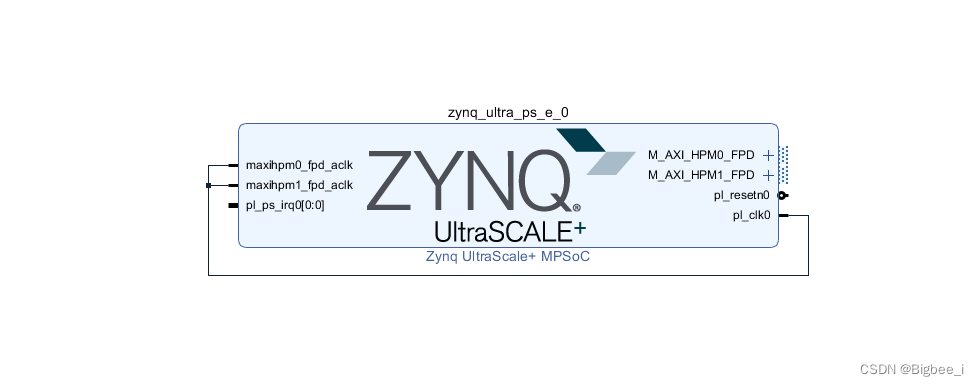

点击 OK 保存

-

将pl_clk0于总线时钟maxihom0/1_fpd_aclk相连。

-

M_AXI_HPM0_FPD可以于PL端的从设备相连,实现PS于PL端的交互。

2.6 最终效果图

本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有涉嫌抄袭侵权的内容,请联系:hwhale#tublm.com(使用前将#替换为@)