1、[Synth 8-2543] port connections cannot be mixed ordered and named ["E:/FPGA_project/Xilinx_ZYNQ/three_days_sobel/_032_face_ov7725/_032_face_ov7725.srcs/sources_1/face_pro/image_pro/image_pro.v":71]

问题:模块例化的时候最后一个端口加了逗号,把逗号删掉即可。

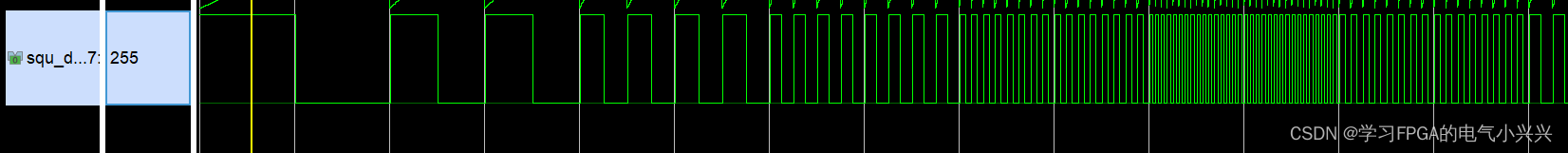

2、Vivado显示方波出现问题,将方波显示为三角波,如下图,squ_data实际上是方波。

误显示为三角波的方波

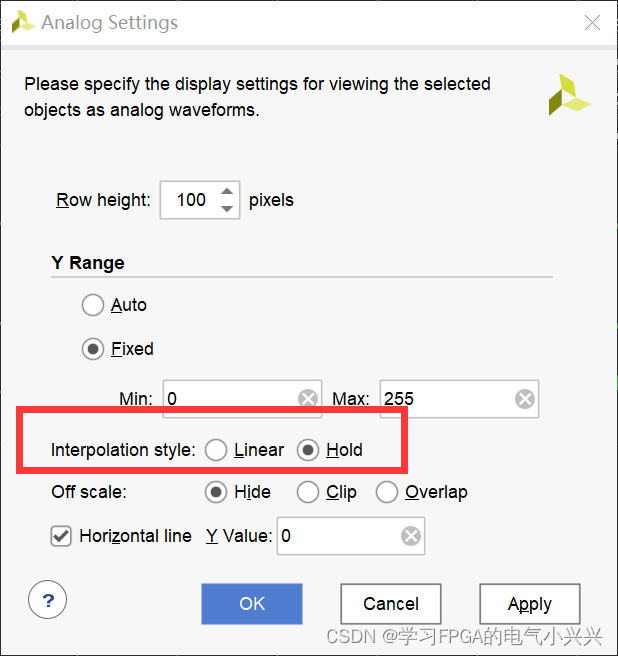

经过反复检查代码后,发现代码完全没错。之后右击信号,选择Wavefoem Style->Analog Setting,将Interpolation style由Linear设置为Hold,然后波形就恢复成方波了,如下所示。

修改设置

波形显示为方波