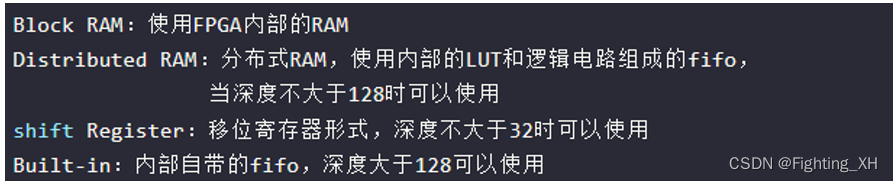

一、 注意FIFO实现方式的选择

除了同步和异步之外,区分不同实现形式下消耗的资源:

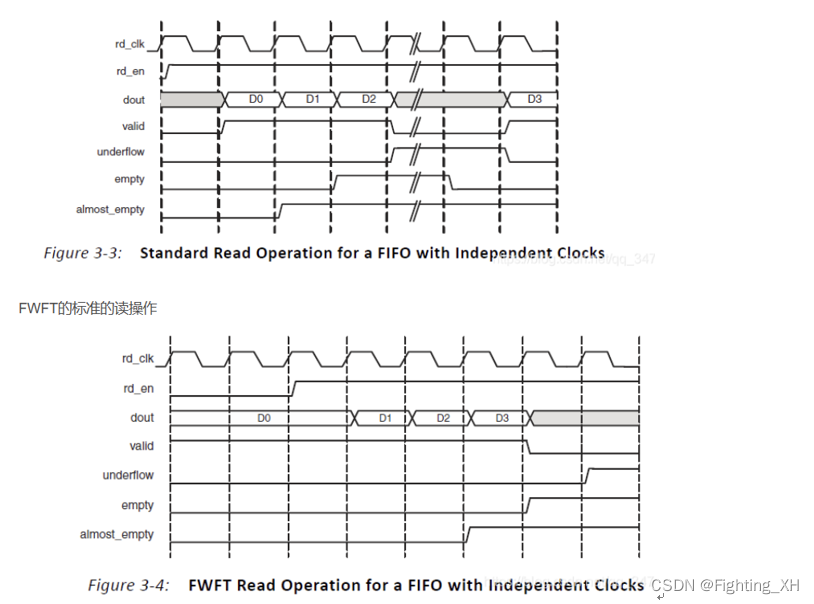

二、注意两种不同的读模式:(标准及FWFT模式)

根据图主要区别在于:

标准模式下,当rd_en有效时,数据才能出现在FIFO的数据线dout上。

FWFT模式下,即使rd_en无效,第一个数据仍然能能出现在FIFO的数据线dout上,当rd_en有效,开始依次读数据。这里rd_en相当于是一个应答信号。

三、 信号延迟

读写数据时不要立刻操作。由于FIFO内部信号存在一定的更新延迟,因此一般延迟10个clk进行操作。

四、 跨时钟处理

在异步FIFO的读写控制部分,存在空满信号的处理。比如在写控制模块中,将读空则进行写操作,这里在使用将读空信号的时候注意,该信号是读时钟下的信号,那么在写控制模块使用的时候需要打两拍,实现跨时钟域,避免亚稳态。