注:大部分参考内容来自“征途Pro《FPGA Verilog开发实战指南——基于Altera EP4CE10》2021.7.10(上)”

贴个下载地址:

野火FPGA-Altera-EP4CE10征途开发板_核心板 — 野火产品资料下载中心 文档

hdmi显示器驱动设计与验证 — [野火]FPGA Verilog开发实战指南——基于Altera EP4CE10 征途Pro开发板 文档

VGA正文开始

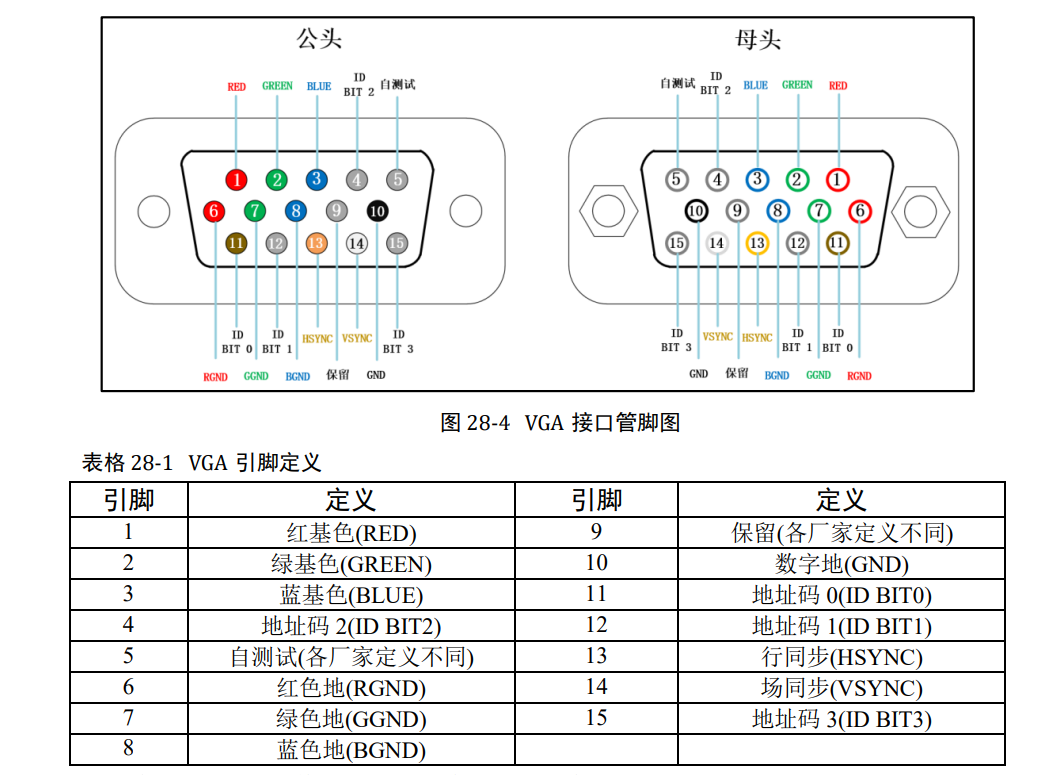

要通俗的理解VGA显示驱动,就要知道实物长什么样子,如下图所示,VGA接口总共有15个,但是需要我们关心的只有以下五个,分别是:

1:红基色,模拟信号,三原色中的R

2:绿基色,模拟信号,三原色中的G

3:蓝基色,模拟信号,三原色中的B

13:行同步,负责显示过程中“行”的扫描

14:场同步,负责显示过程中“场(列)”的扫描

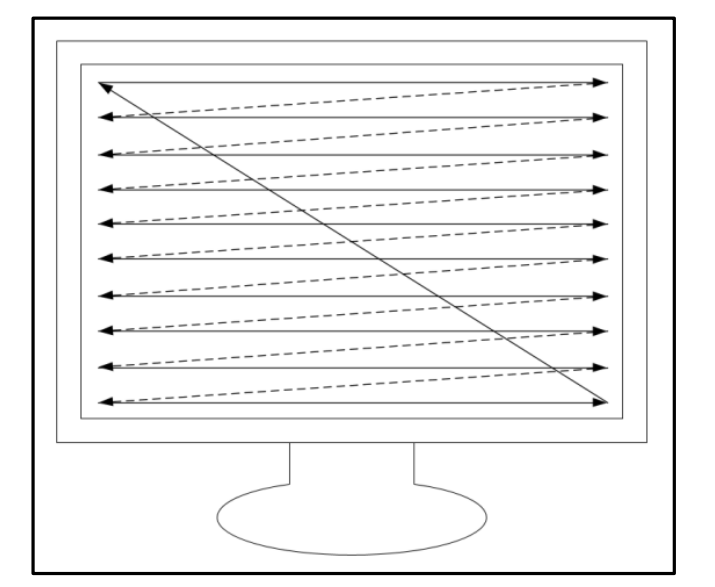

VGA的显色原理图如下

假设我们需要显色的图像是640x480的,这一幅画面上,横着的点有640个,竖着的点有480个。我们通过行同步信号和场同步信号来确定每个点的位置,然后给每个点一个数据(8位:RGB232、16位:RGB565、24位:RGB888等),即可显示出一副画面。

所以说,要想使VGA显示一副画面,就需要我们利用FPGA向行同步和场同步输出显示点的位置,然后利用FPGA向红基色接口、绿基色接口和蓝基色接口赋值即可。

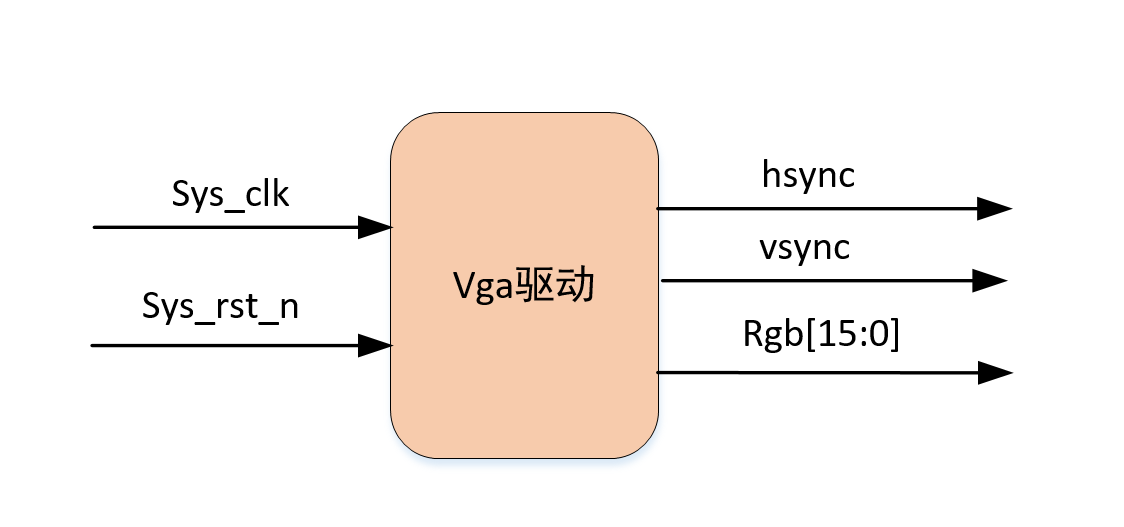

所以编写VGA的驱动模块就变得十分的简单了,只需要利用我们的FPGA,向VGA外设输出行同步信号、场同步信号和数据即可。

在绑定管脚时,行同步和场同步各一根线绑定,RGB数据,各按照自己的位宽绑定即可(例如我这里是绑定16根线)

HDMI正文开始

上面讲了关于VGA的驱动,我们可以看出VGA 显示具有成本低、结构简单、应用灵活等优点,但缺点是 VGA 使用的模拟信号(R、G、B)极易受到外界干扰源的影响,产生信号畸变,而且 VGA 接口体积较大, 不利于便携设备的使用。

这个时候,HDMI接口便应运而生了。(讲解HDMI A Type)

HDMI接口的实物如下图所示,共有19个接口,但在显示图像时,我们只需要用到10个接口,分别是:

7、9:数据0+、数据0-(差分信号,抗干扰)

4、6:数据1+、数据1-

1、3:数据2+、数据2-

10、12:时钟+、时钟-

15、16:SCL、SDA -> 发送端与接收端通过I2C协议,得知彼此的发送与接收能力。

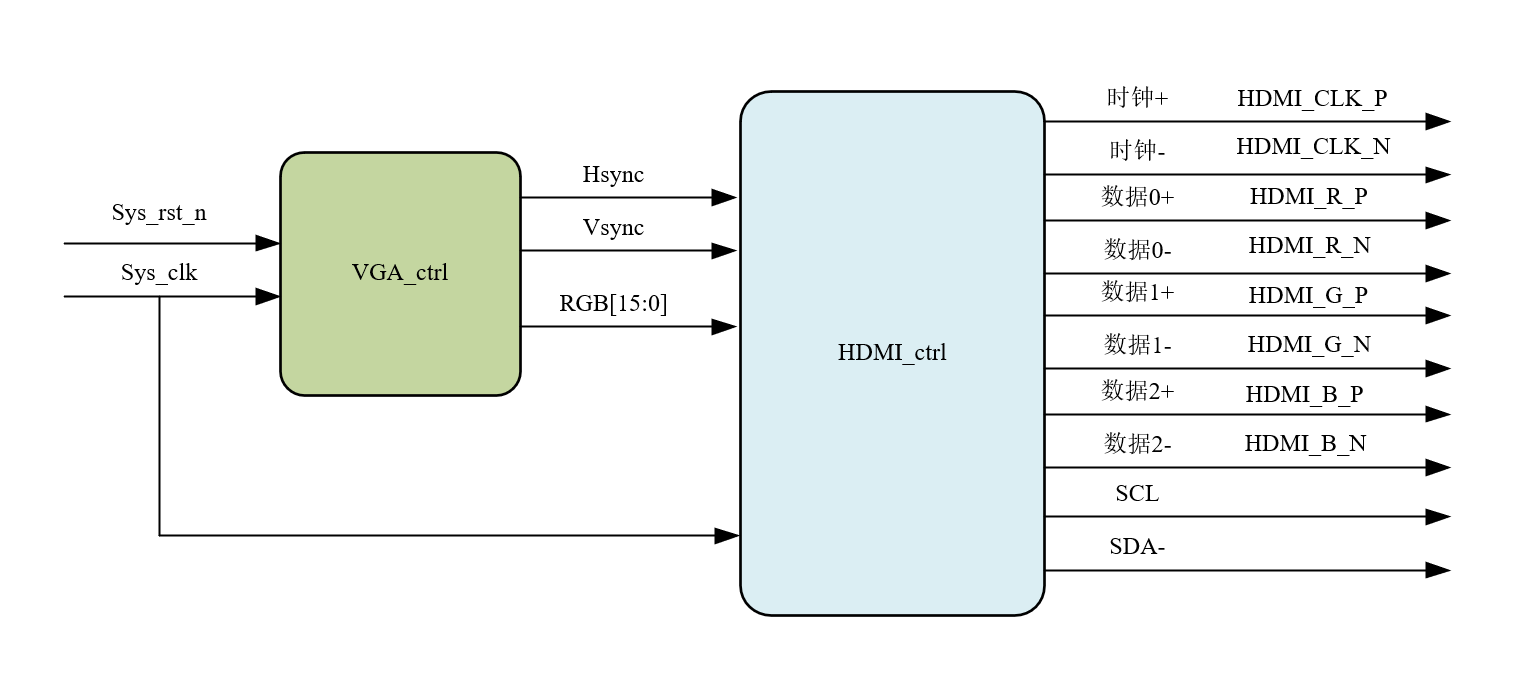

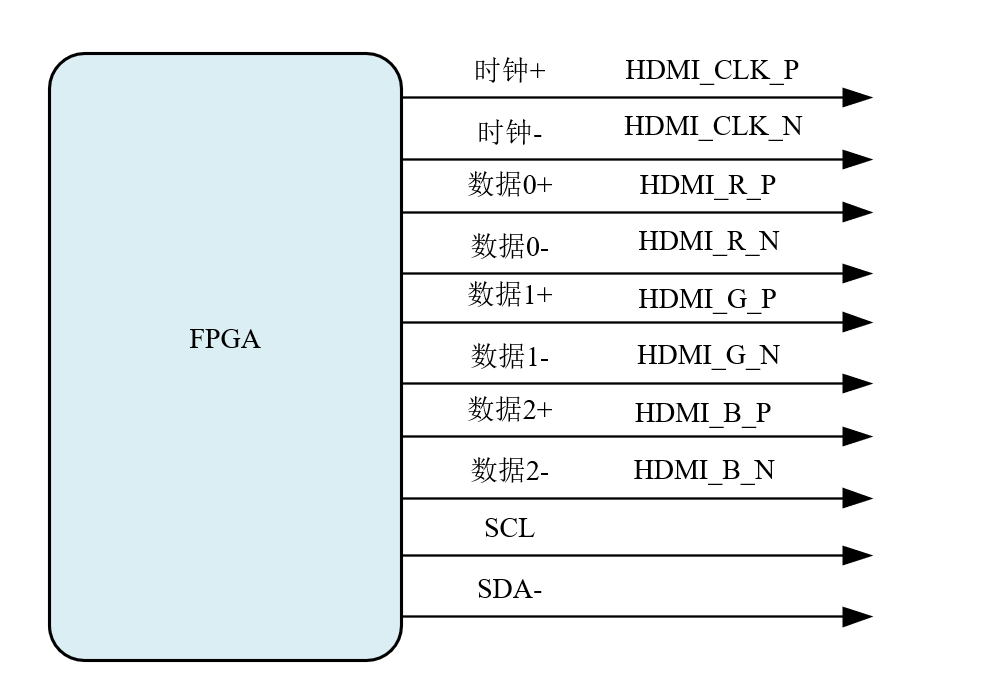

所以说,如果要用FPGA驱动HDMI显示,则FPGA应该向对HDMI的十个接口进行赋值,分别是数据0+、数据0-、数据1+、数据1-、数据2+、数据2-、时钟+、时钟-,这十个接口全部为1Bit数据,同时这十个接口也是FPGA需要往HMDI上面绑定的十个管脚,模块框图如下:

VGA转HDMI

VGA输出的RGB数据,我们可以通过特定的模块转为数据0+、数据0-、数据1+、数据1-、数据2+、数据2-。时钟我们也可以通过一个模块把输入的时钟转为差分时钟。

假设RGB一共24位(R分量占8位,G分量占8位,B分量占8位),此时我们就可以分别把R、G、B转为串行差分信号进行输出

R-------->数据0+、数据0-;

G-------->数据1+、数据1-;

B-------->数据2+、数据3-;

在转换的过程中我们需要注意并行转串行、单端转差分、以及编码(8位转9位),HDMI协议所要求。

所以顶层模块变成如下框图所示: