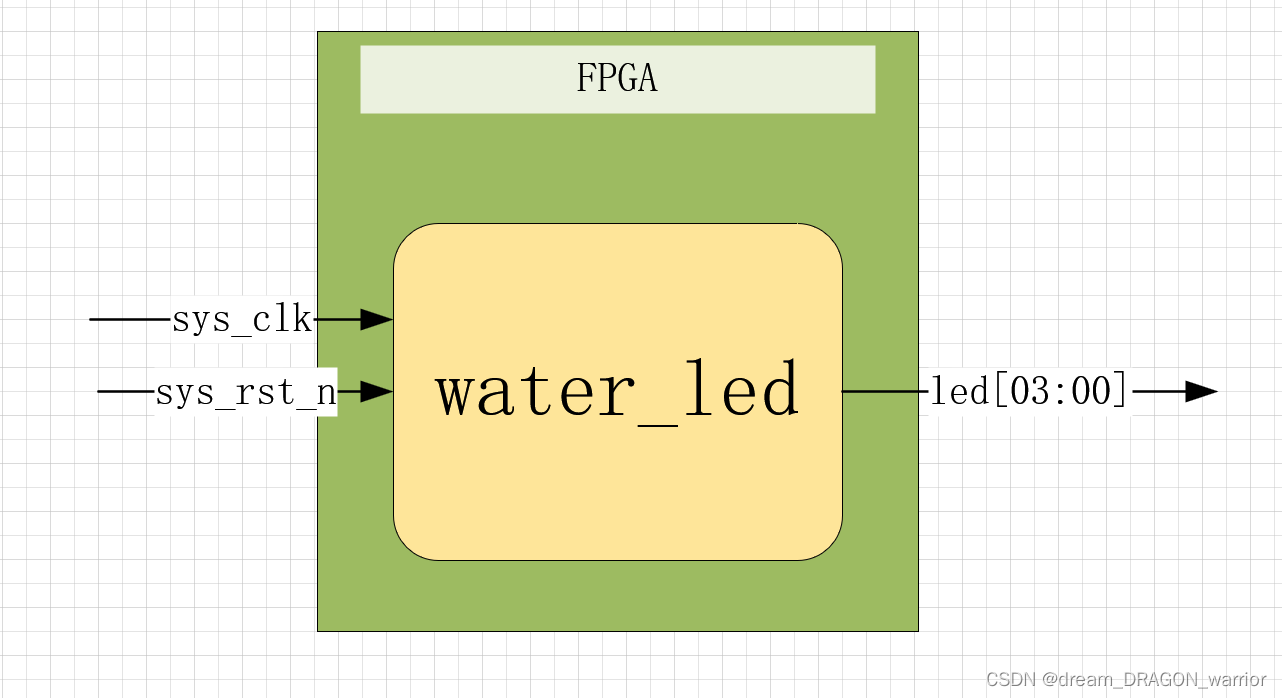

module water_led

#(

parameter MAX_CNT = 25'd25_000_000

)

(

input wire sys_clk ,

input wire sys_rst_n ,

output wire [03:00] led

);

// signal

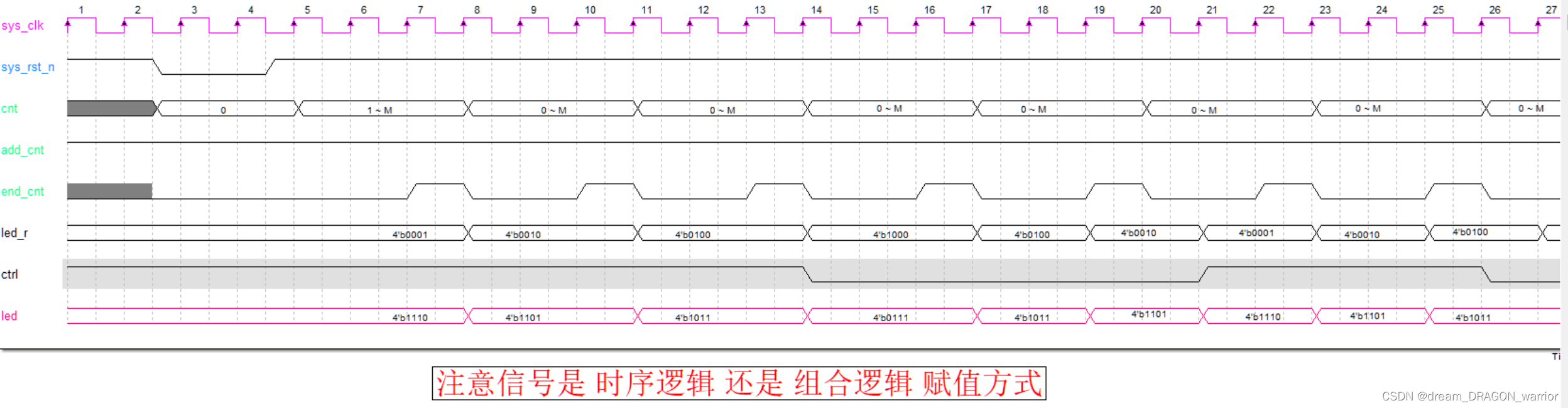

reg [24:00] cnt_half_sec ;

wire add_cnt ;

wire end_cnt ;

reg [03:00] led_r ;

reg ctrl ;

// cnt

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n) begin

cnt_half_sec <= 0 ;

end else begin

if(add_cnt) begin

if(end_cnt) begin

cnt_half_sec <= 0 ;

end else begin

cnt_half_sec <= cnt_half_sec + 1'b1 ;

end

end else begin

cnt_half_sec <= 0 ;

end

end

end

assign add_cnt = 1'b1 ;

assign end_cnt = add_cnt && cnt_half_sec == ( MAX_CNT - 1'b1 ) ;

// // led_r <<

// always @(posedge sys_clk or negedge sys_rst_n) begin

// if(~sys_rst_n) begin

// led_r <= 4'b0001 ;

// end else begin

// if((led_r == 4'b1000) && end_cnt ) begin

// led_r <= 4'b0001 ;

// end else begin

// if(end_cnt) begin

// led_r <= ( led_r << 1 ) ;

// end else begin

// led_r <= led_r ;

// end

// end

// end

// end

// led_r {}

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n) begin

ctrl <= 1'b1 ;

end else begin

if(end_cnt && led_r == 4'b0010) begin

ctrl <= 1'b1 ;

end else begin

if(end_cnt && led_r == 4'b0100) begin

ctrl <= 1'b0 ;

end else begin

ctrl <= ctrl ;

end

end

end

end

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n) begin

led_r <= 4'b0001 ;

end else begin

if(ctrl) begin

if(end_cnt) begin

led_r <= {led_r[2:0],led_r[3]} ;

end else begin

led_r <= led_r ;

end

end else begin

if(end_cnt) begin

led_r <= {led_r[0],led_r[3:1]} ;

end else begin

led_r <= led_r ;

end

end

end

end

// led

assign led = ~led_r ;

endmodule

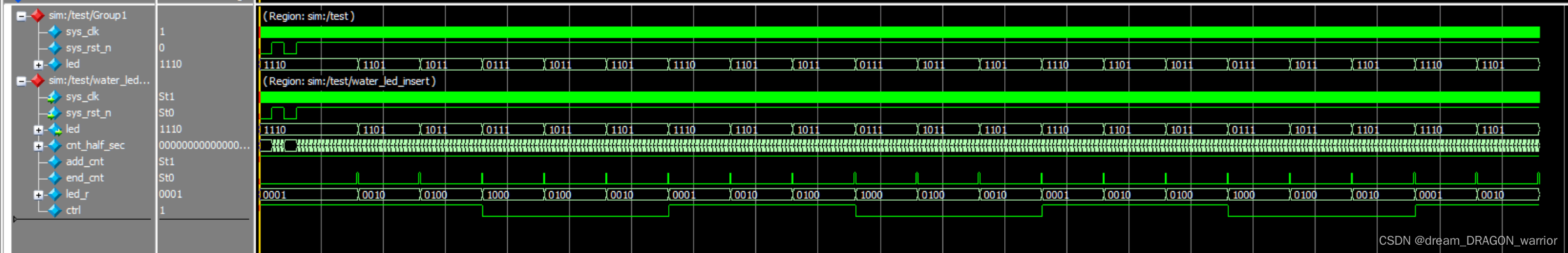

`timescale 1ns/1ns

module test();

reg sys_clk ;

reg sys_rst_n ;

wire [03:00] led ;

water_led

#(

.MAX_CNT (50)

)

water_led_insert

(

.sys_clk ( sys_clk ) ,

.sys_rst_n ( sys_rst_n ) ,

.led ( led )

);

parameter CYCLE = 20 ;

initial begin

sys_clk = 1'b1 ;

sys_rst_n <= 1'b0 ;

#( CYCLE * 10 ) ;

sys_rst_n <= 1'b1 ;

#( 210 ) ;

sys_rst_n <= 1'b0 ;

#( CYCLE * 10 ) ;

sys_rst_n <= 1'b1 ;

#( CYCLE * 50 * 20 ) ;

$stop ;

end

always #( CYCLE / 2 ) sys_clk = ~sys_clk ;

endmodule