Timing arc(时序弧)描述从一个pin到另一个pin之间的不可分割的路径时序信息。

关键术语:

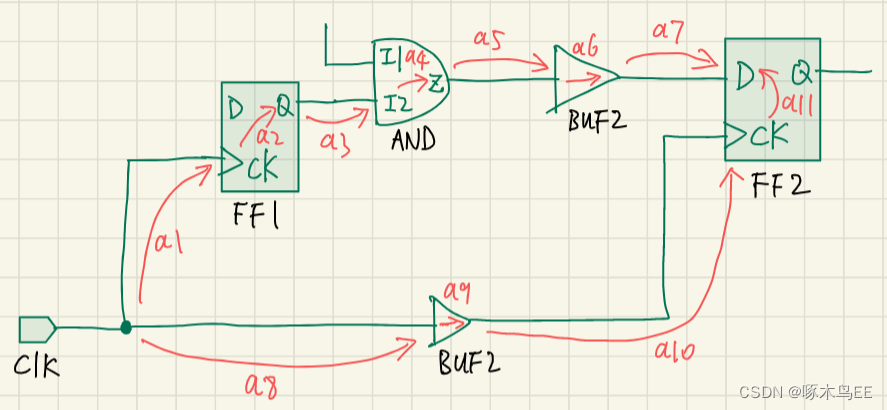

source pin:timing arc的起始点,以下图为例,CLK是a1和a8的source pin,FF1/CK是a2的source pin,而FF1/Q又是a3的source pin;

sink pin:timing arc的终止点,下图中FF1/CK是a1的sink pin,AND/Z是a4的sink pin,FF2/D是a11的sink pin;

Net arc:source pin是某个cell的output pin,而sink pin是另一个cell的input pin,下图中,a1, a3, a5, a7, a8, a10都是net arc;

Cell arc:与net arc相反,source pin是某个cell的input pin,而sink pin是这个cell的另外一个pin(delay arc对应output pin,而timing check arc对应input pin),根据cell的不同,还可以继续细分;

-

- Sequential arc:包含在sequential cell内部的timing arc,其中delay arc是CK -> output pin,而timing check arc是CK -> input pin;

- Combinational arc:包含在combinational cell内部的timing arc,只有input pin -> output pin一种。

Unateness:用于描述timing sense of an arc. 可以分为:

-

- Positive unate:rising signal input -> rising or no change signal output, falling signal input -> falling or no change signal output, e.g. BUFFER, AND, OR, all net arcs

- Negative unate: rising signal input -> falling or no change signal output, falling signal input -> rising or no change signal output, e.g. NOT, NAND, NOR

- Non unate: output pin value is not dependent on single input pin, e.g. XOR, XNOR