本文主要参考了黑金社区提供的资料,整理而成

目录

1.Vivado 开发环境

1.1 Vivado 软件介绍

1.2 Vivado 软件版本——2017.4比较稳定

2. Vivado 软件 Windows 下安装

3. 重新安装驱动

4. 大功告成!具体实验可以参考pdf文件

教程链接: https://pan.baidu.com/s/1275Ppq9xd7hQ0kJRGmdD6g 提取码: Sean

1.Vivado 开发环境

1.1 Vivado 软件介绍

一提起 Xilinx 的开发环境,人们总是先会想起 ISE,而对 Vivado 不甚了解。其实,Vivado 是 Xilinx 公司于 2012 推出的新一代集成设计 环境。虽然目前其流行度并不高,但可以说 Vivado 代表了未来 Xilinx FPGA 开发环境的变化趋势。所以,作为一个 Xilinx FPGA 的开发使用 者,学习掌握 Vivado 是趋势,也是必然。作为开发者,首先肯定有以下疑惑:既然已经有 ISE 存在了,为何 Xilinx 公司又花大力气去搞什么 Vivado 呢?在 Vivado Design Suite User Guide : Getting Started(UG910)中提到,推出 Vivado 是为了提高设计者的效率,它能显著增加 Xilinx 的 28nm 工艺的可编程逻辑器件的设计、综合与 实现效率。可以推测,随着 FPGA 进入 28nm 时 代,ISE 工具似乎就有些“不合时宜”了,硬件提升了,软件不提升的话,设计效率必然受影 响。正是出于这 一考虑,Xilinx 公司于 2008 年开始便筹划推出新一代的软件开发环境,经历 10 年时间打造出了 Vivado 工具这一巅峰之作。

1.2 Vivado 软件版本——2017.4比较稳定

安装 Vivado 2017.4 的软件。因为 Vivado 软件比较大,我们没有提供光盘安装文件, 只提供下载链接,另外用户也可以到 Xilinx 的官网下载,官网下载需要注册相关账号。 Vivado 软件的 Xilinx 官方下载地址:http://china.xilinx.com/support/download.html

Vivado 提供了 Linux 版和 Windows 版,还提供二合一版本,我们这里使用二合一版本,既 能满足 Windows 开发又能满足 Linux 开发,Vivado 要求操作系统必须是 64 位。

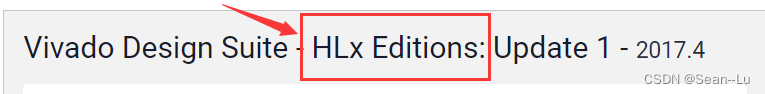

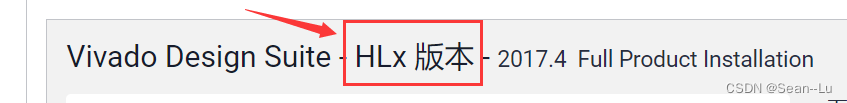

下载HLx版本——更没更新的这两个版本都行,第一次应该要注册账号!文件太大,不能放网盘,请自行下载!

2. Vivado 软件 Windows 下安装

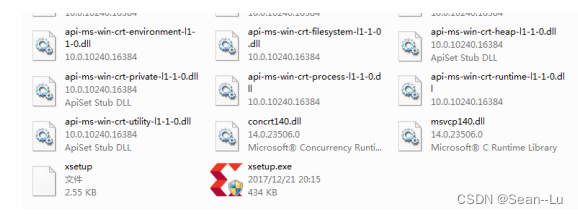

1) 下载解压 Vivado 软件压缩包,直接点击 xsetup.exe,进入安装,不过为了更好的安装,请 关闭杀毒软件,各种电脑管家,电脑用户名不要有中文,和空格

2) 如果提示版本更新,我们忽略更新,点击“Continue”

3) 点击“next”进行安装,可以看到 Vivado 对系统要求

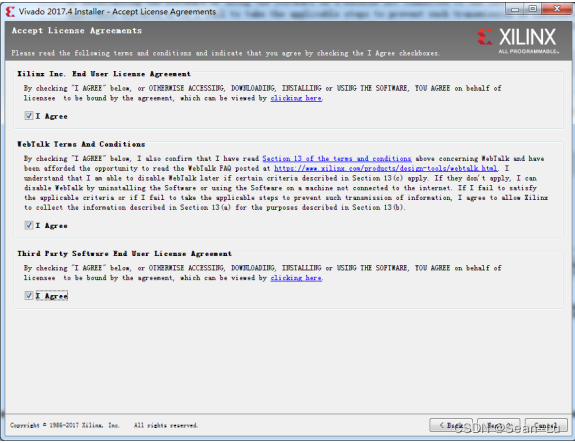

4) 点击“I Agree”接受各个条款

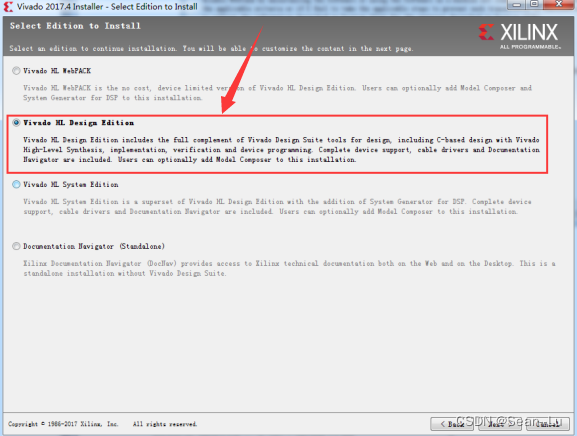

5) 选择“Vivado HL Design Edition”

6) 这里使用默认配置,点击“next”

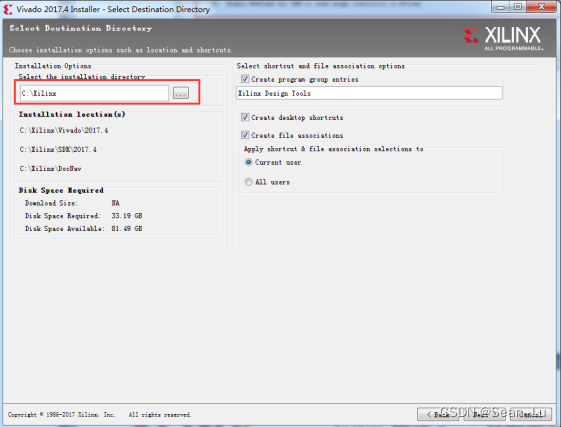

7) 安装路径这里没有修改,安装路径不能有中文、空格等特殊字符,同时电脑的用户名不要 是中文、带空格的名称。可以看到 Vivado 对硬盘大小的要求,大约 33G。

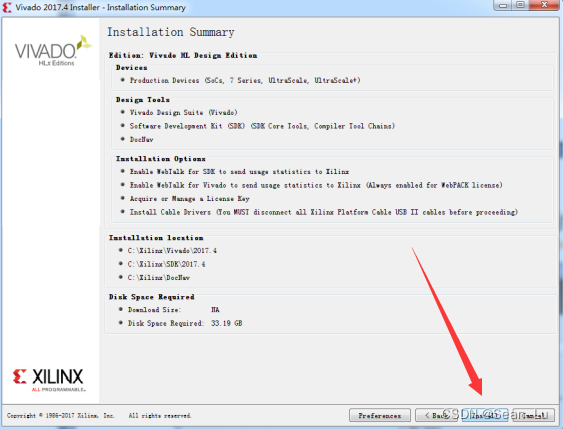

8) 点击“Install”安装

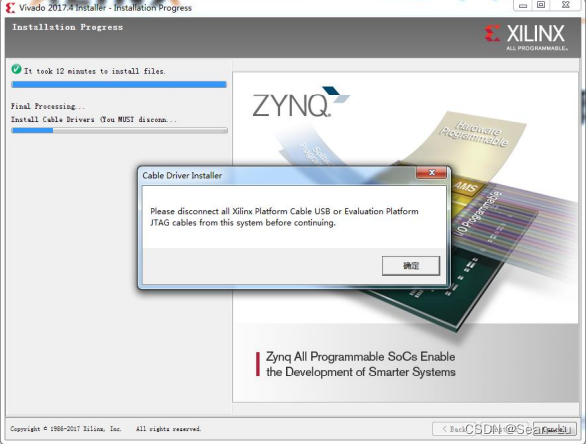

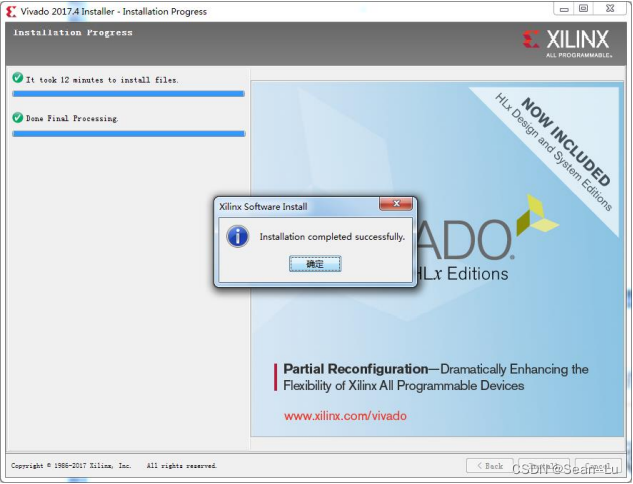

9) 等待安装,时间较长,如果没有关闭杀毒软件和电脑管家,安装过程可能会被拦截,导致 安装软件后不能使用

10) 这个时候提示我们断开下载器或者开发板的 JTAG 线,点“确定”

11) 提示安装成功

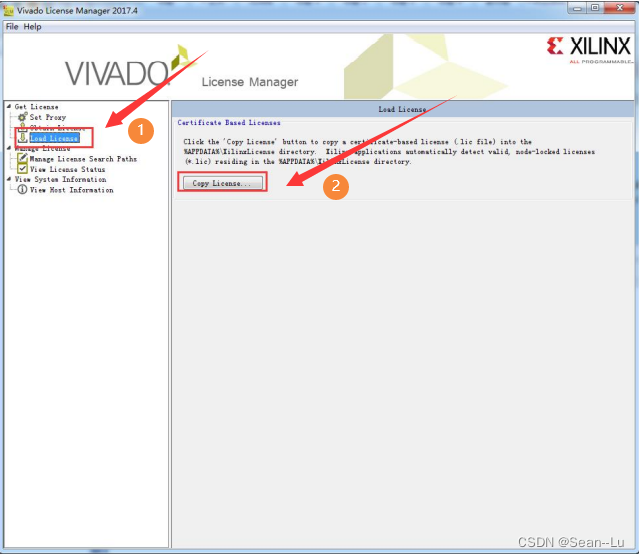

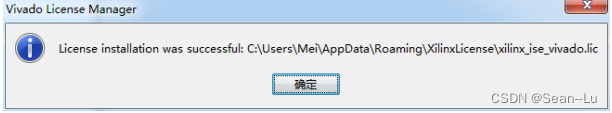

12) 安装 License 文件,点击“Copy License”,选择“xilinx_ise_vivado.lic”文件。(文件在分享的百度网盘里)

13) 可以看到安装成功

3. 重新安装驱动

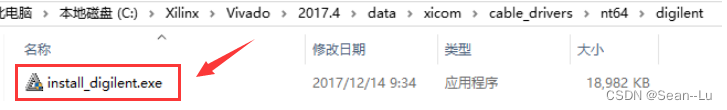

一般安装 vivado 时,都会安装下载器驱动。如果需要再次安装下载器驱动,进入 vivado 安装路径“X:\Xilinx\Vivado\2017.4\data\xicom\cable_drivers\nt64\digilent”下,双击 “install_digilent.exe”文件安装,安装前先关闭 vivado 软件,如果 vivado 识别不到下载器,请 尝试关闭防火墙,杀毒软件,也不能同时打开多个版本的 vivado、ise。

安装完成后,连接下载器,打开设备管理器,在通用串行总线控制器里找到 USB Serial Converter,说明安装成功

安装完成后,连接下载器,打开设备管理器,在通用串行总线控制器里找到 USB Serial Converter,说明安装成功

4. 大功告成!具体实验可以参考pdf文件