一、组合逻辑与时序逻辑的对比

1、组合逻辑的输出状态与输入直接相关,时序逻辑还必须在时钟上升沿触发后输出新值。

2、组合逻辑容易出现竞争、冒险现象,时序逻辑一般不会。

3、组合逻辑的时序较难保证,时序逻辑更容易达到时序收敛,时序逻辑可控。

4、组合逻辑只适合简单的电路,时序的逻辑能够胜任大规模的逻辑电路。

补充:设输出为F,输入为A、B

或:F=A+B

与:F=AB

非:F=A’

与非门逻辑表达式:Y=(A·B)’=A’+B’

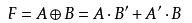

异或:

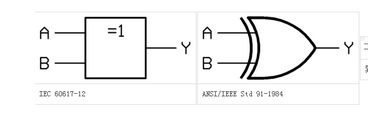

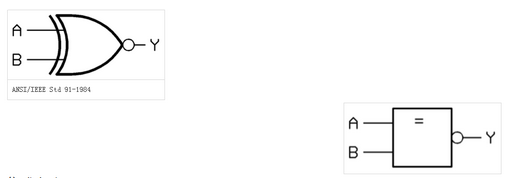

同或门逻辑表达式:(⊙为“同或”运算符)

A⊙B=AB+A’B’=(A⊕B)’

二、组合逻辑的实现

1、组合逻辑实现方式1:always @ (电平敏感信号列表)

(1)在always模块中可以使用if、case等语句

(2)一般建议使用阻塞赋值语句“=”

(3)always模块中的信号必须定义为reg型,这仅仅是语法要求,实际仍然是wire类型

2、组合逻辑实现方式2:assign描述的赋值语句

(1)信号只能被定义为wire型

三、时序逻辑的实现

1、时序逻辑实现方式:always @ (posedge clk) begin…end

(1)时序逻辑always模块中定义的reg型信号都会被综合成reg(寄存器)

(2)时序逻辑中一般建议使用非阻塞赋值“<=”

(3)敏感变量表中只要有时钟沿的变化即可,即每次触发输出变化都是时钟沿引入的