vivado2013.4和modelsim联合仿真

Hello,Panda

最近在做Zynq的项目,曾经尝试使用ISE+PlanAhead+XPS+SDK组合和Vivado+SDK来搭建工程,使用中发现前者及其不方便后者有诸多不稳定。近期得闻Xilinx退出Vivado2013.4,就迫不及待的想试用一把,看之前的bug是否有修复,稳定性有没有变好,就从和ModelSim的联合仿真做起吧。

其实Vivado IDE本身具有强大的仿真工具vivado simulator,支持功能仿真和后仿,但是那个特别耗电脑资源,笔记本基本上是跑不动的,如果电脑给力用起来还是很顺手的。它还支持与Cadence、Modelsim等第三方工具协同联合仿真(详见UG900),因为习惯原因,故选用ModelSim试一试。

1. ModelSim版本要求

Vivado2013.4只支持Modelsim10.2A及其以上版本,低版本不支持。

2. 编译仿真库

使用TCL脚本:compile_simlib(详细内容见UG835),一般而言,以下内容就以足够

compile_simlib -directory <library_output_directory> -simulator <agr>

-simulator_exec_path<sim_install_location>

例如:a)仿真库编译到D:/xilinx_sim_lib;

b)仿真工具使用Modelsim;

c)ModelSim安装在C:/modeltech64_10.2/win64;

那么完整的tcl命令就是:

compile_simlib -directory D:/xilinx_sim_lib -simulator modelsim

-simulator_exec_path C:/modeltech64_10.2/win64

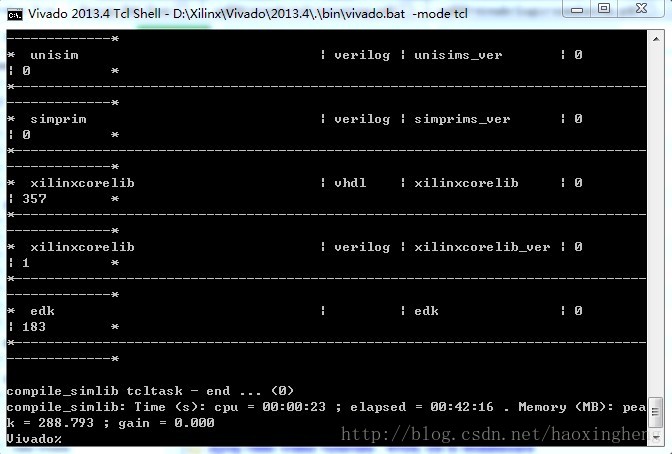

执行该命令需要耐心等待,这个过程视电脑能力好坏可能需要30~60min,直到窗口提示compile_simlib tcl task –end才算完成,如图所示。

图1 库文件编译完成提示

打开D:/xilinx_sim_lib文件夹可以发现,所有的库文件和Modelsim.ini文件均已生成。

3. 设置关联

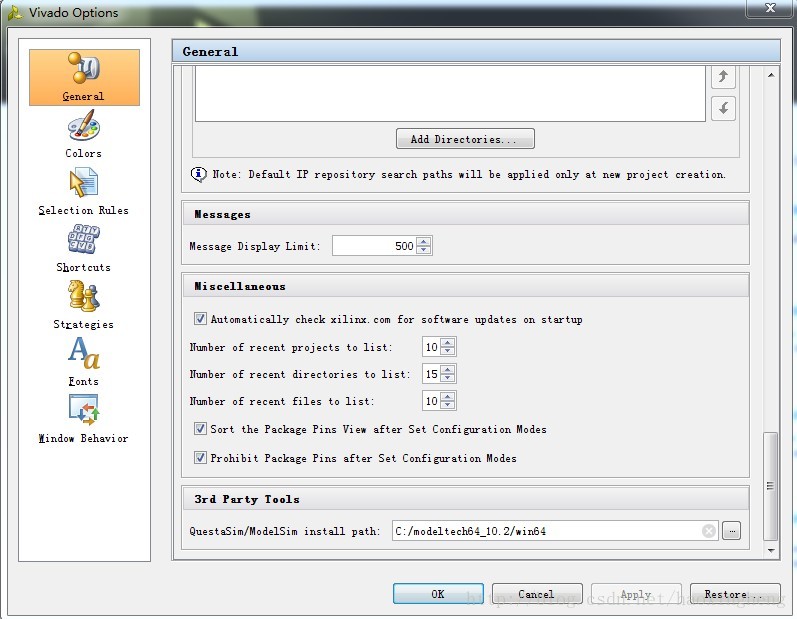

打开Vivado IDE(start_gui),在在tools -> vivado options -> general中设置第三方工具的路径,如图2所示:

图2 设置ModelSim的安装路径

4.在工程中对仿真工具进行配置

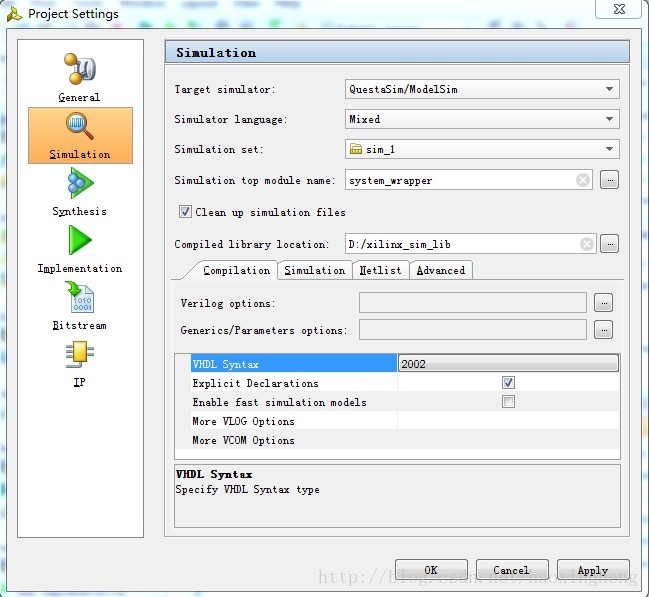

在工程配置项simulation->simulation settings中将target simulator选择为ModelSim,Compiled library Location指向刚才编译的库路径,其他设置不详细介绍,如图3所示。

图3 仿真工具设置

OK,如果中途不出什么差错,到这个步骤位置就可以顺利完成和ModelSim的联合仿真了。