DPHY的基本介绍及使用已有很多文章,基本是基于《MIPI Alliance Specification for D-PHY 》的内容,学习时也以此为准,可参考CSDN上的文章。着重讲述MIPI D-PHY的初始化部分

1 D-PHY的功能及使用

下面的文章讲的不错,既有理论,又有实际示波器抓取的波形。此处不再赘述。

MIPI 系列之 D-PHY_爱洋葱的博客-CSDN博客

2 初始化问题

2.1 Xilinx DPHY使用

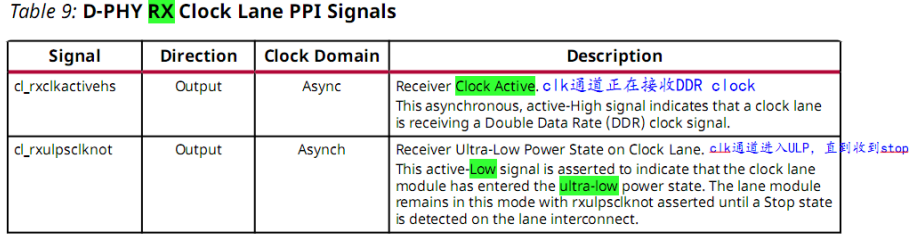

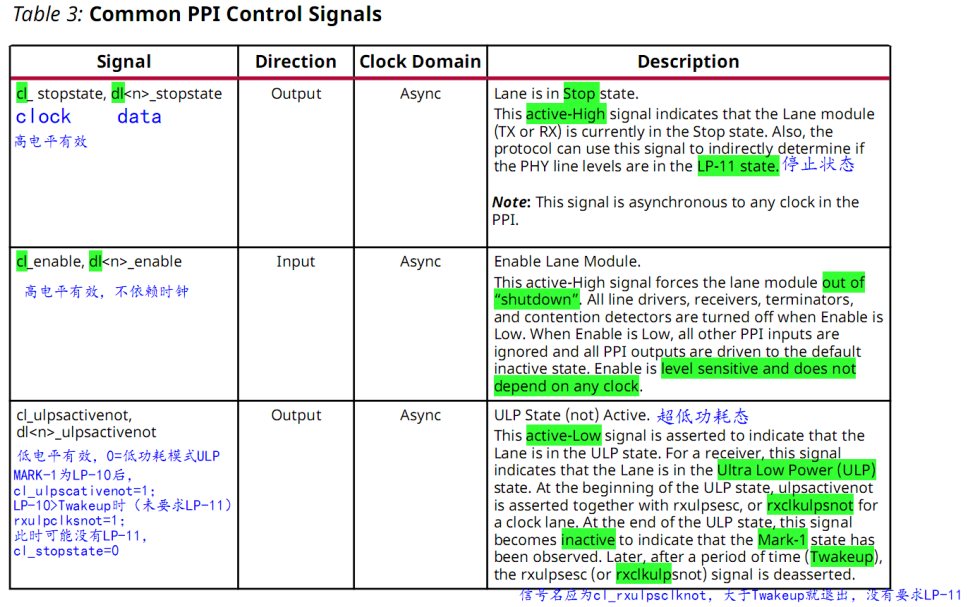

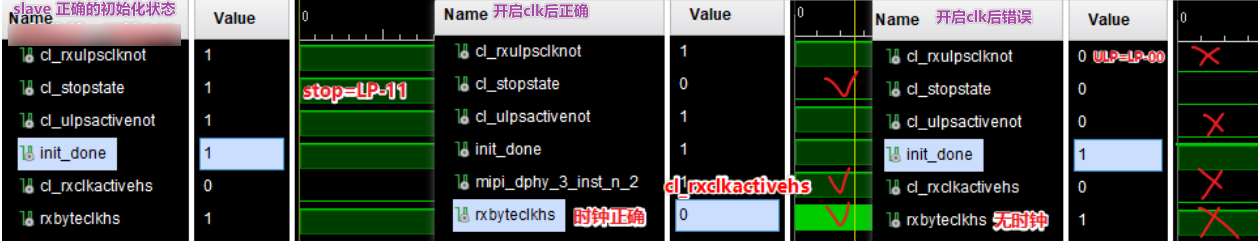

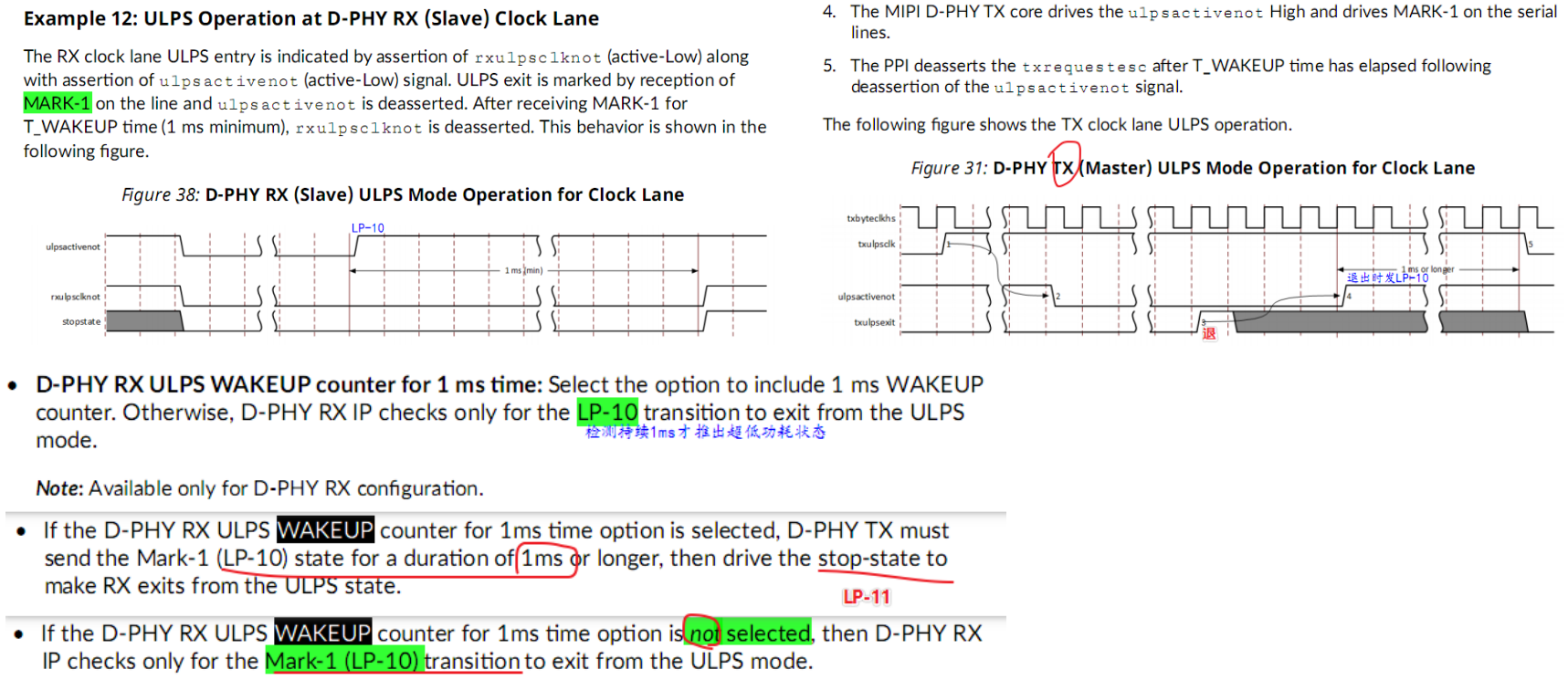

在Vivado中使用MIPI D-PHY时,发现slave的clock lane进入ULPS,导致不能正常接收clock(通过ILA抓取IP的ulps指示信号)。

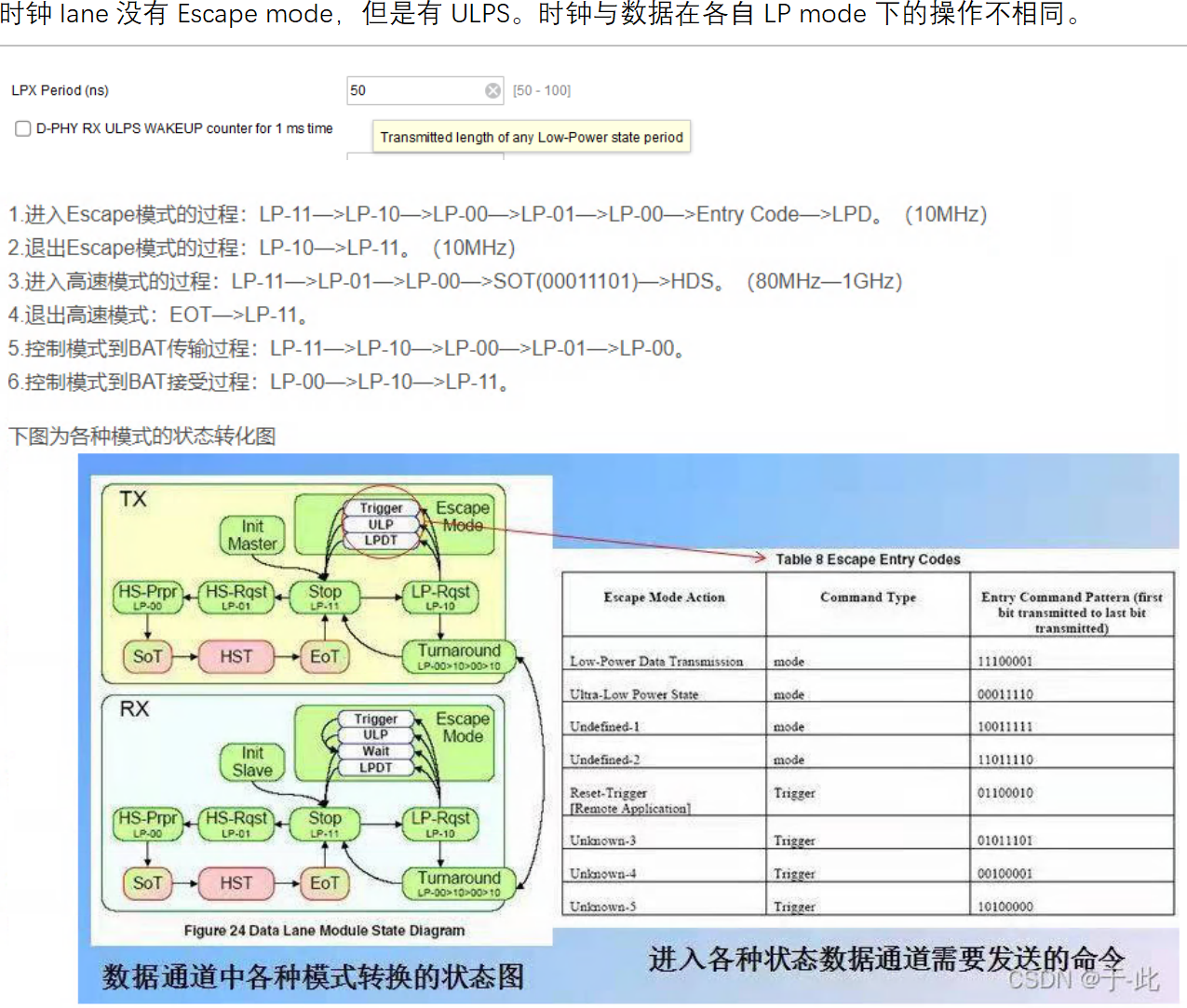

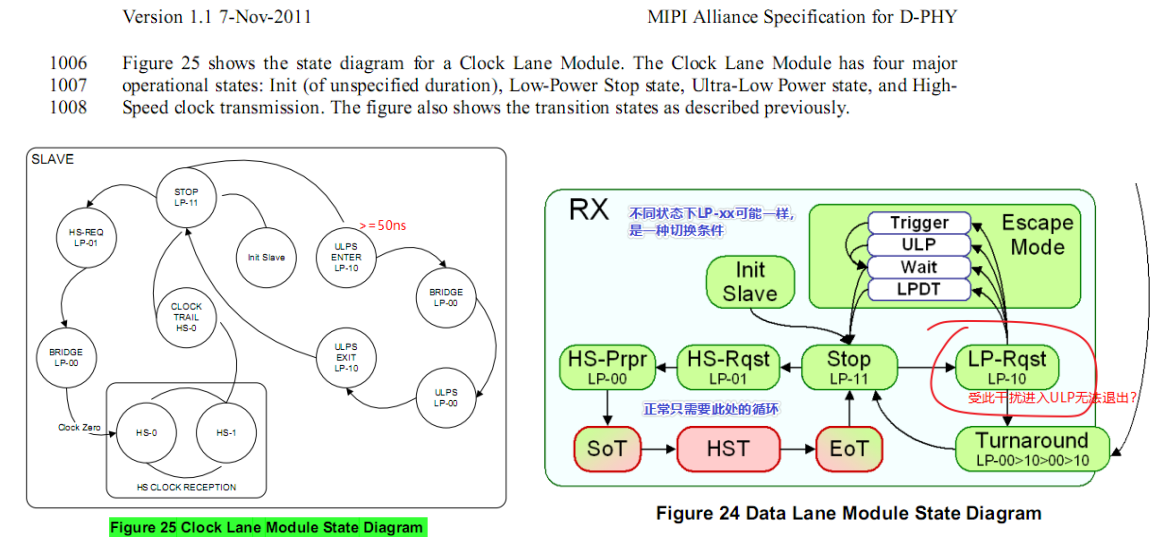

2.2 spec中的状态图

根据spec中的状态图,clk lane比data lane更容易进入ULPS。(贴图两者进入ULPS的图)

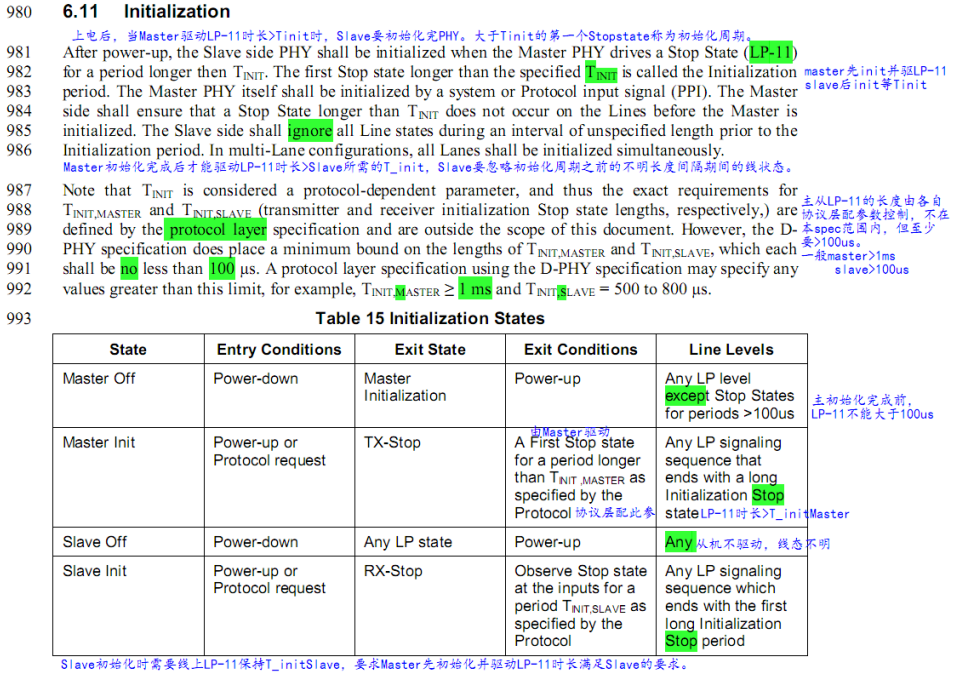

2.3 MIPI的初始化要求

根据mipi dphy spec V1.1中需要master先完成init并驱动总线LP-11,slave再进行初始化可等到足够长的LP-11.

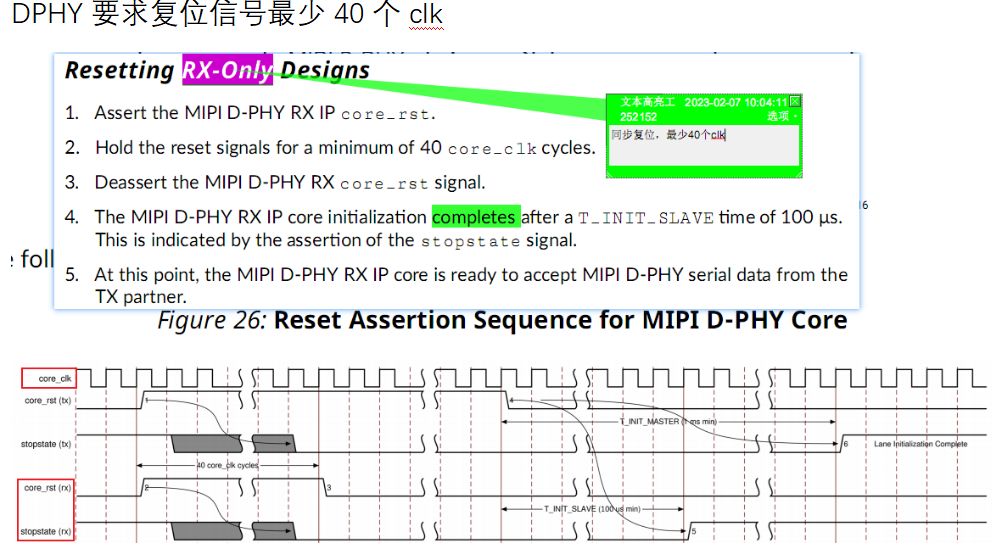

在xilinx MIPI中 提到了系统级的复位初始化时序。LP-11最少要求100us:master可采用1ms,slave可采用100us。

解决方法:在master init完成后,再对slave DPHY复位初始化(同时在GUI中去掉对ULPS的支持)。若slave先初始化,总线上状态不确定,可能会造成IP进入ULPS而无法退出。

2.4 Xilinx DPHY退出ULPS的TX、RX时序

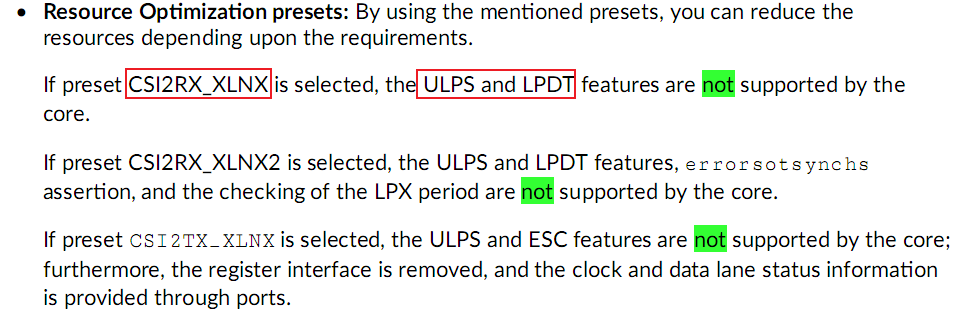

2.5 在Xilinx DPHY的GUI中去掉ULPS

在Vivado中DPHY IP GUI中可以去掉对ULPS的支持,精简资源。避免异常进入。

2.6 在Xilinx DPHY的复位要求

3 校准问题

3.1 MIPI SEPC中关于校准

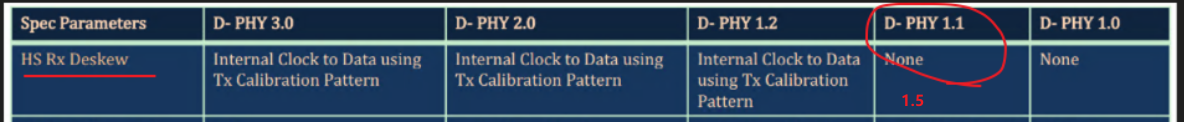

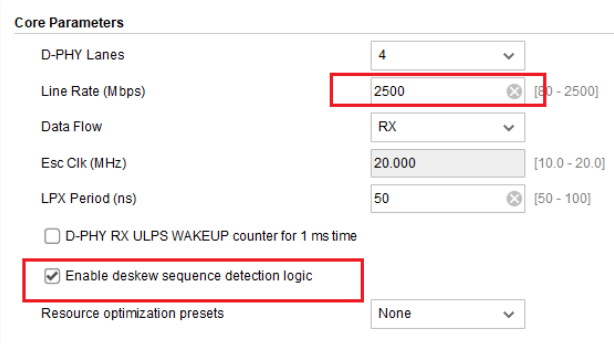

D-PHY 1.1的速率支持到1.5G,且不支持协议自动deskew,仅能通过硬件布线、FPGA中手动增加idelay的方式保证时钟/数据lane的对其关系。

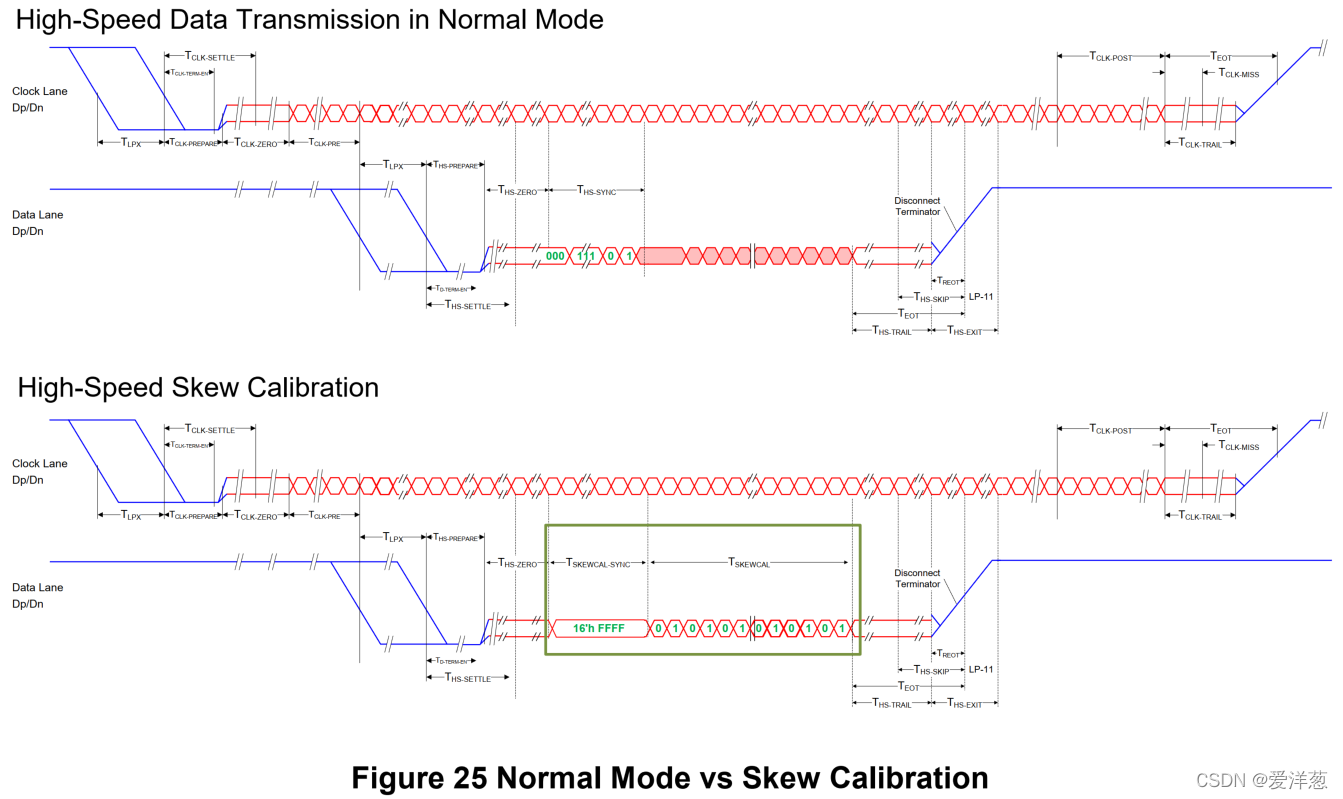

速率更高时spec标准中规定需要校准,且有校准的流程。每次进入HS发送数据前都需要校正,校正模型先发送16'hffff,后接长的010101...(长度根据RX的要求,如2^13 UI),接收端根据01自动调整采样位置。

Xilinx DPHY中<=1.5G在7系列中的IP内,有idelay的参数可以调节,KU+的IP中没有提供。在KU+的IP中当速率>1.5G 时才有deskew的选项,且要求校准模型长度2^13 UI.

4 重点内容梳理

4.1 spec中6.13节的操作流程图

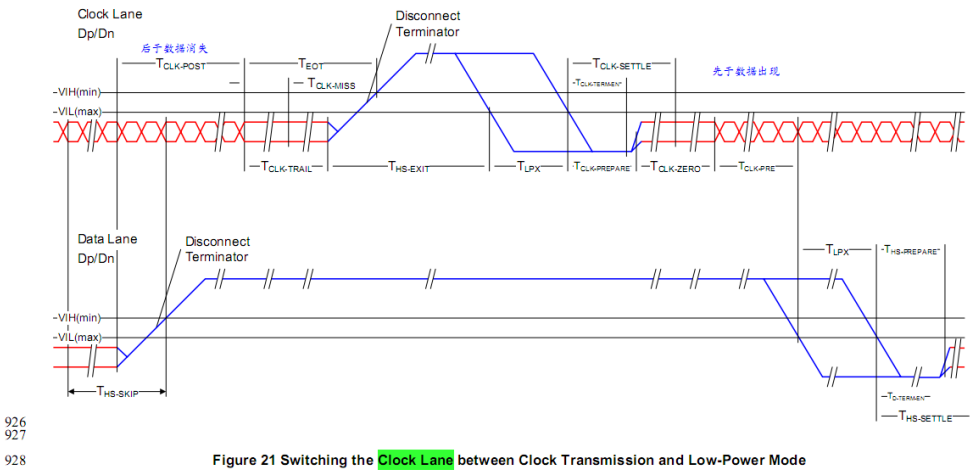

spec中的图,描述了data lane 和clock lane的完整工作流程。从LP进入/推出HS。

时钟通道

数据通道

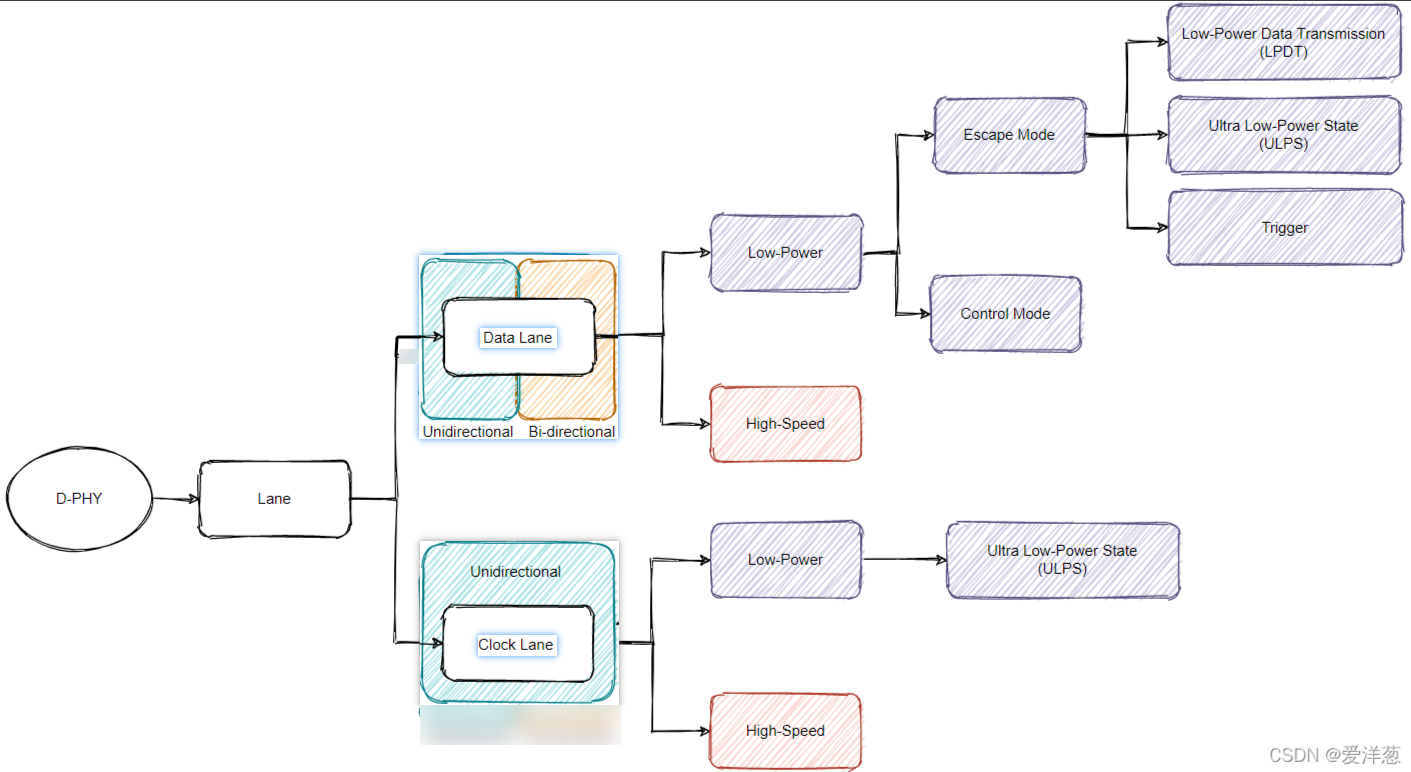

4.2 数据通道与时钟通道的不同

图片来源见水印,原图中应该有笔误,已修正如下(data双向,clk单向)。

1)data 有Escape mode(其中又细分为UPLS,LPDT,Trigger等),进入时序比较复杂。此模式下不要clk lane,时钟从独热码的LP数据中可以恢复;clk lane只有UPLS且进入时序简单;

2)data可以双向,有turnaround,slave发数据给master(LP和HS都可以反向发数据,速率最大是正向的1/4);clk只能由Master发给slave,单向。

3)数据进入HS时有SOT,即在HS-0保持一段时间后+同步字节(在PHY中同步后剥离,不进入CSI-2)。退出时要根据最后一个数据bit翻转后保持一段时间后LP-11;clk进入HS-0后仅保持一段时间可发时钟,退出时也可保持HS-0即可。

4.3 Data lane 进入ESCAPE mode

1)trriger 模式类似中断,通过在LP模式时发送固定的字节,触发一个事件,如复位;

2)LPDT模式可以发送任意字节的数据;

3) trigger模式,ULP模式退出时要先进入wait模式;

4)进入ESCAPE时有专门的cmd,一个字节的数据。比clk lane进ULPS复杂。